.-.Д. .: : . . .

Изобретение относится к автоматике н вычислительной технике в предназначено для формирования напряжения пропорциовшш Цого ивтегр лу от входного сигнала. Оно может сподьзоваться в системах автомати ческого управления различных Техаологиче- ских процессов и объектов, когда требуются больЬие постоянные интегрирования.

Известны устройства для ивтегрирования, содержажие реверсивные сдетчйкй импульсов, цифро-аналоговые преобразователи в преобразователи напряжение - частота, выполненные аа основе аналоговых интеграторов н компараторов l

Однако в известньас устройствах вслед- ствие сбоев счетчика под действием случайных помех и перерывов в подаче питания происходит разрушение информадии, накопленной интегратором, что может приводить к аварийным последствиям, а потому во многих случаях совершенно недопустимо.

Указан Чзй недостаток устраняется в аналого-цифровом интеграторе с контуром для восстановления информации, содержащем трехпозиционный блок сравнения, последовательно соединенные аналоговый внтет тор, компаратор, реверсивный счетчик имь пульсов, цифро-аналоговый преобразователь, БЫХБД которого подхлючен к первому входу сумматора, источачх задания начальных условий и источник управлякяаего сигнала, блок управления, один вход которого соэ-. дивен с выходом сумматора, а другой - с источником управляюшегосигнала .

Однако этот интегратор отличается сложностью схемы, требующей применения в контуре восстановления информадии трехпоЗИЕ1ШОННОГО блока сравнения, низким быстродействием в режимах записи начальных условий и восстановления кнформадкн, что при сбоях счетчика может привйдить к возникновению ьначительной погрешности интегратора из-за разряда запоминающего конденсатора в блоке слежения-хранения. В конечном счете снижается надежность и точность интегратора.

Целью изобретения является повышение надежности а точности устройства.

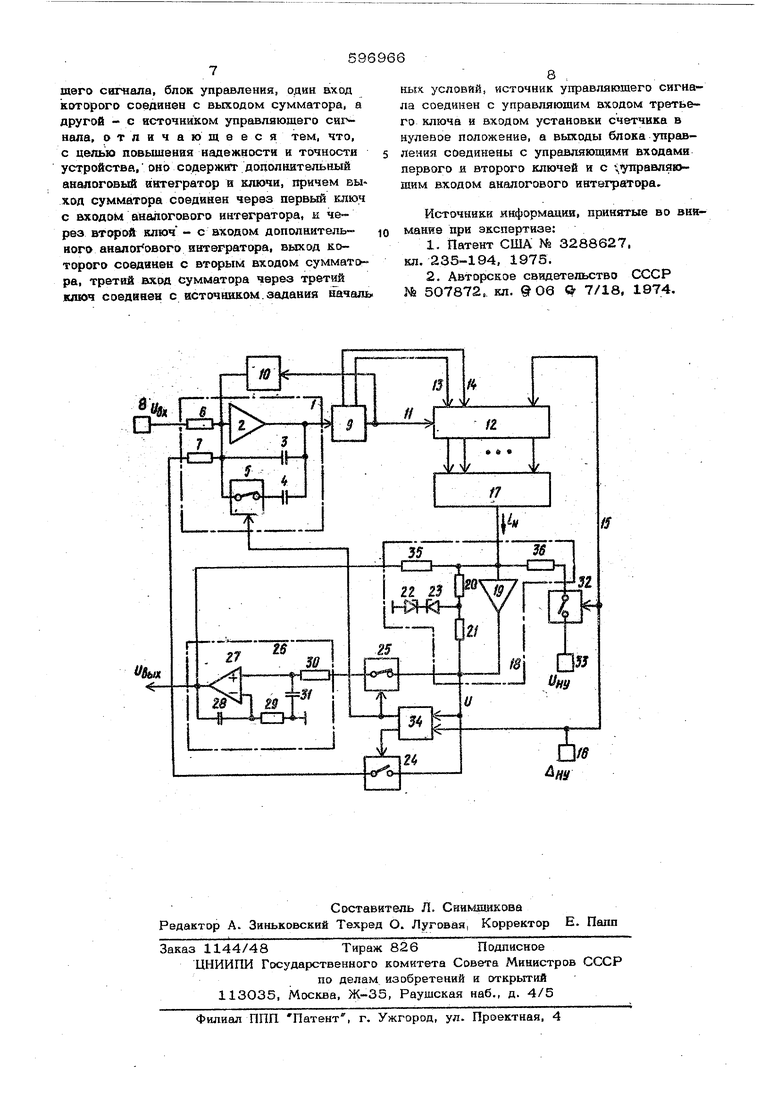

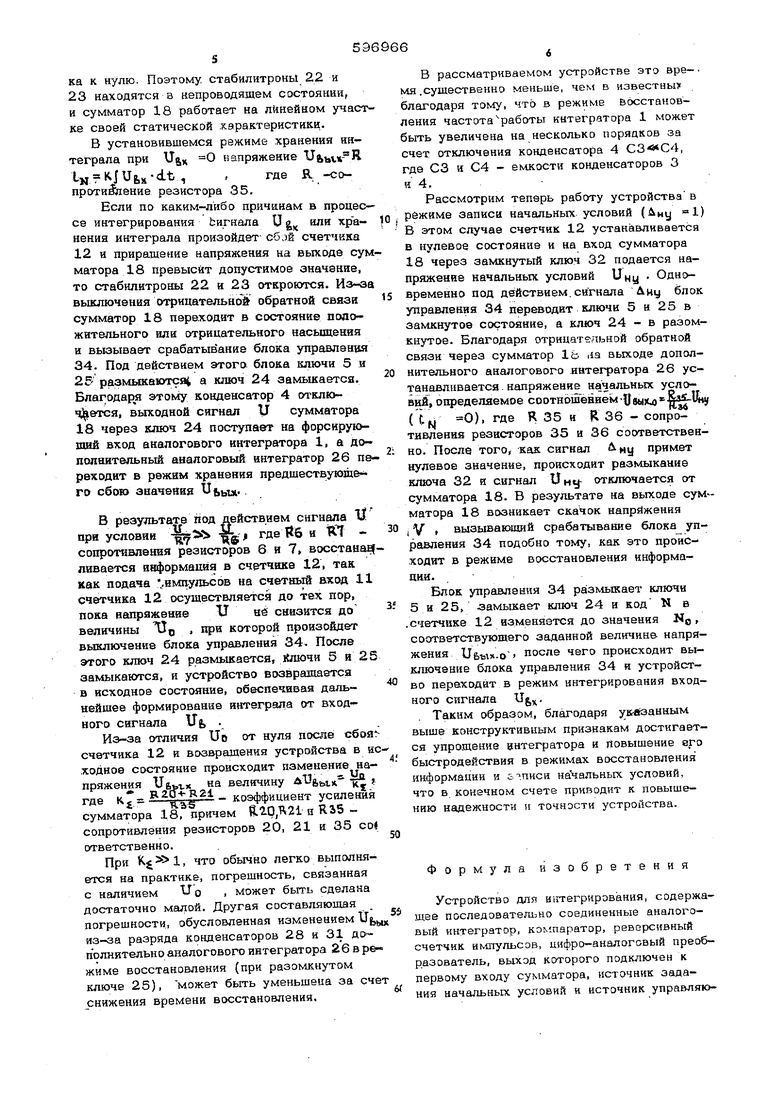

Для этого оно содержит .дополнительный аналоговьШ интегратор и ключи, причем выход сумматора соединен-i через первый ключ с входом аналогового интегратора, и через второй ключ - с входом дополнительного аналогового интегратора, выход которого соединен с вторым входом сумматора, третий вход сумматора через третий ключ соединен с источником задания начальных условий, источник управляющего сигнала со динен с управляющим входом третьего ключ и входом установки счетчнка В нулевое пол жение, а выходы блока управления соединен с управляющими входами первого и второго улючей и с управдяюшим входом аналоговог интег|затора. На чертежа приведена структурная электрическая схема устройства. Устройство для интегрирования содержит аналоговый интегратор 1, построенный на операционном усилителе 2, в цепь обратной связи KOTjoporo включены кондейсаторы 3 и 4, соединенные параллельно через ключ 5; «на аходе усилителя 2 включены резисторы 6 и 7, к первому из которых подсое динен источник входного сигнала 8 Uf . Выход усилителя 2 подключё к К компаратору 9, обеспечивающему сброс аналогового интегратсфа в начально положение через цепь обратной связи 1О. Импульсный выход компаратора подсоединен к счетному входзг 1 реверсивного счетчика импульсов 12. Входы управления реверсом (сложением вычитанием) 13 и 14 счетчика 12 соединены с потенциальными в оходами компаратора 9, а цепь 15 установки нуля счетчика 12 подключена к источнику 16 управляющего сигнала ( Дну ) Выходы счетчика 12 подключены к сетке резисторов цифро-аналогового преобразователя 17; соединенного с первым входом сум матора 18, построенного на операционном усилителе 19. Усилитель 19 охвачен нелинейной отрицательной обратной связью, образованной двумя последовательно включенными резисторами 20 и 21, точка соединения которы через встречно включенные стабилитроны 22 и 23 подключена к корпусу устройства. Выход сумматора 18 через ключ 24 соединен с входом аналог ового интегратора 1 и через второй ключ 25 - с неинвертирующим входом дополнительного аналогового интегратора 26, включающего в себя операционйый усилитель 27 с конденсатором 28 в цепи отрицательной обратной связи, резистор 29 и апериодическое звено (резистор 30 ис сонденсатор 31). Выход дополнительного аналогового интегратора 26 подключен к второму входу сумматора 18, к третьему входу которого через 32 подключен источник задания начальных условий 33 ( Uny ) Сумматор 18 подключен непосредственно к входу блока управления 34, соединенного по выходам с управляющими входами ключей 5, 24 и 25. Другой вход блока управления 34 подключен к источнику управляющего сигнала 16 ( Л ну ). Для рассматриваемого устройства харак терны следующие режимы работы: интегрирование; восстановление информации и запись начальных условий. В режиме интегрирования сигнал , ключ 32 разомкнут, и блокуправления 34 находится в состоянии, при котором ключа 5 и 25 замкнуты, а ключ 24 разомкнут. При наличии входного сигнала ( О) аналоговый интегратор 1 интегрирует Зтот сигнал, и на вход компаратора поступают импульсы с частотой, пропорционально U|,,{. При этом в зависимости от знака tJftx на потенциальных выходах компаратора 9, соединенных с входами управления- реверсом 13 и 14 счетчика 12, устанавливаются напряжения, настраивающие счетчик на сложение или вычитание импульсов. Возникновение импульсов на счетном входе 11 реверсивного счетчика импульсов 12 происходит в моменты времени, когда вапря жение на выходе усилителя 2 достигнет, уров ЕЯ срабатьшания компаратора 9, после чего под действием цепа обратной связи 1О осуществляется быстрый сброс аналогового интегратора (разряд включенных параллельно конденсаторов 3 и 4). В результат е-компаратор 9 выключается, и процесс интегрирования (заряда конденсаторов 3 и 4) под действием напряжения Ub повторяется. G помощью компаратора 9В счетчике 12 фиксируются величина и знак приращения ннтег рала входного напряжения бз; . т.е. осуществляется квантование ийтеграл,а входного сигнала по уровню. Преобразование цифрового кода N.y ,характеризуюшего интеграл Jtlftxi-t , в электрическое напрягкение (вьгходной сигнал интегратора) осуществляется с помощью цифро-аналогового преобразователя 17, сумматора 18 и дополнительного аналогового интегратора 26. При надлежащем выборе постоянной интегрирования Ги дополнительного аналогового интегратора 26 и постоянной, времени Т апериодического звена (ЗОи 31) в режиме, когда ключ 25 замкнут, интегратор 26 благодаря отрицательной обратной связи через сумматор 18 успевает следить за током Lji на выходе цифро-аналогового преобразователя 17 так, что динамическая ошибка на выходе сумматора 18 близка к нулю. Поэтому, стабилитроны 22 и 23 находятся в непроводящем состоянин, и сумматор 18 работает на линейном участ ке своей статической .кэрактеристики. В установившемся режиме хранения интеграла при и О напряжение XJbj, l-Kt R -сопротивдение резистора 35. Если по каким-либо причинам в процес се интегрирования Ьигнала U или хранения интеграла произойдет- сбэй счетчиха 12 и прирашение напряжения на выхода сум матора 18 превысит допустимое аначенне, то стабилитроны 22 ii 23 откроются. Из-з выключения отрицательней обратной связи сумматор 18 переходит в состояние положительного или отрицательного насыщения и вызывает срабатывание блока управления 34. Под действием SToroi блока ключи 5 и 2S размыкаются а ключ 24 замыкается. Благода|ет этому конденсатор 4 оа-клю« 9тся, выходной сигнал U сумматора 18 через ключ 24 поступает на форсирук ашй вход аналогового интегратора 1, а допопаительный аналоговый интегратор 26 пе реходит в режим хранения предшествующе го сбою значеиня tlf,i,tjt. . В результате под действием сигнала 11 при условии W& где вб и 1С сопроп впешя резисторов 6 и 7, восстаиад дивается информация в счетчика 12, так как подача .импульсов на счетньй аход 11 счетчика 12 осуществляется до те.х пор, пока вапряясенае XJ не снизится до величины tJj, , при которой произойдет выключение блока управления 34 После этого ключ 24 размыкается, Ключи 5 и 25 замыкаются, и устройство возвразаается в исходное состояние, обеспечивая дальнейшее формирование интеграла от входного сигнала 1Гь . Из-за отличия UD от нуля после cбoя счетчика 12 и возвращения устройства в к .ходное состояние происходит изменение наи бы-к на величину AUg,, - .- бьгх на величину it . пряжения ±... - коэффициент усиления кГ где rvj- - :g сумматора 18, причем ft.2.p, н RS5сопротивления резисторов 20, 21 и 35 со ответственно. При , что обычно легко выполняется на практике, погрешность, связанная с наличием UG , может быть сделана достаточно малой. Другая составляющая погрешности, обусловленная изменением U|,y из-за разряда конденсаторов 28 и 31 допЪлнительно аналогового интегратора 26 в режиме восстановления (при разомкнутом ключе 25), может быть уменьшена за сче снижения времени восстановления. В рассматриваемом устройстве это вре-. мя .сушественно меньше, чем в нзвестны благодаря тому, что в режиме восстановления частота работы интегратора 1 может быть увеличена на несколько порядков за счет отключения конденсатора 4 , где СЗ и С4 - емкости конденсаторов 3 и 4. Рассмотрим теперь работу устройства в режиме записи начальных условий (Лиц 1) В этом случае счетчик 12 устанавливается в нулевое состояние и на вход сумматора 18 через замкнутый ключ 32 подается напряжение начальных условий Uny Одновременно под действием, сигнала Лму блок управления 34 переводит ключи 5 н 2 5 в замкнутое состояние, а ключ 24 - в разомкнутое. Благодаря отрицательной обратной связи через сумматор 1Ь лз выходе дополнительного аналогового интегратора 26 устанавливается, напряжение начальных условий, определяемое соотношением-{fj y с 0), где R 35 и R 36 - сопротивлення резисторов 35 и 36 соответственно. После того, как сигнал му примет нулевое значение, происходит размыкание ключа 32 и сигнал UHIJ- отключается от сумматора 18. В результате на выходе сумматора 18 возникает скачок напряжения i V вызываюншй срабатывание блока управления 34 подобно тому, как это происходит в режиме восстановления информации. Блок управления 34 размыкает ключи 5 и 25, .замыкает ключ 24 и код И в счетчйке 12 изменяется до значения NO соответствующего заданной величине напряжения XJfetiDi.o после чего происходит выключение блока управления 34 и устройство переходит в режим интегрирования входного сигнала И, Таким образом, благодаря у тзаиным выше конструктивным признакам достигается упрощение интегратора и повышение его быстродействия в режимах восстановления информации и ь-.писи начальных условий, что в конечном счете приводит к повышению надежности и точности устройства. Формула изобретения Устройство для иятегриров1ания, содержаш.ее последоватеж но соединенные аналоговый интегратор, компаратор, реверсивный счетчик икшульсов, цифро-аналоговый преобразователь, выход которого подключен к первому входу сумматора, источник задания начальных условий и источник управл5пошаго сигнала, блок управления, один аход которого соединен с выходом сумматора, а другой - с источником управляющего сиз нала, ртличающееся тем, что, с целью повышения надежности и точностн устройства, оно содержит дополнительный аналоговьШ интегратор в ключи, причем БЫ« ход сумматора соединен через первый ключ с входом аналогового интегратора, и через второй ключ - с входом дополнительного аналог ового интегратора, выход которого соединен с вторым входам сумматора, третий вход сумматора через третий ключ соедввен с всточником. задания вачаль

8

условий, источник управляюшего сигнала соединен с управляющим входом третьего ключа и входом установки счетчика в нулевое положение, а выходы блока управления соединены с управляющими входами первого и второго ключей и с управляюжим входом аналогового интегратора.

Источники информации, принятые во вняманйе при экспертизе:

1.Патент США Ns 3288627, кл. 235-194, 1975.

2,Авторское свидетельство СССР J 507872. кл. СЮв Q 7/18, 1974,

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой интегратор | 1980 |

|

SU866563A1 |

| Аналого-цифровой интегратор | 1979 |

|

SU813456A2 |

| Аналого-цифровой интегратор | 1973 |

|

SU507872A1 |

| Аналого-цифровой интегратор | 1977 |

|

SU732905A1 |

| Аналого-цифровой интегратор | 1977 |

|

SU682908A2 |

| Аналого-цифровой интегратор | 1978 |

|

SU805345A1 |

| Интегратор | 1978 |

|

SU748438A1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Гибридное интегрирующее устройство | 1985 |

|

SU1316008A1 |

| Интегратор | 1986 |

|

SU1401485A2 |

Авторы

Даты

1978-03-05—Публикация

1976-01-19—Подача