1

Изобретение относится к телеграфной свзи, а именно к устройствам, предназна енным для синхронизации сигналов. Известно устройство для синхронизации сигналов в многоадресных системах связи с временным раацелением каналов, содержащее последовательно соединенные блок для вьщеления сигналов синхронизации, фазовый дискриминатор, реверсивный счетчик, управитель с генератором и управляемый делитель, выходы которого подключены к второму входу фазового дискриминатора.

Однако известное устройство характеризуется значительным временем, затрачиваемым на фазирование.

Целью изобретения является ускорение фазирования по сигналам различных каналов. Для этого в устройство введены кольцевой регистр, блок для перезаписи кода, формирователь импульсов перезаписи и продвижения и делитель, причем выходы и установочные входы каждого разряда управляемого делителя через блок для перезаписи кода соединены с установочными входами

и выходами соответствующих разря,цов кольцевого регистра, а управляющие входы блока для перезаписи кода и шина продвигающих импульсов кольцевого регистра соединены с соответствующими выходами формирователя импульсов перезаписи и продвижения, подключенного к выходу генератора через делитель.

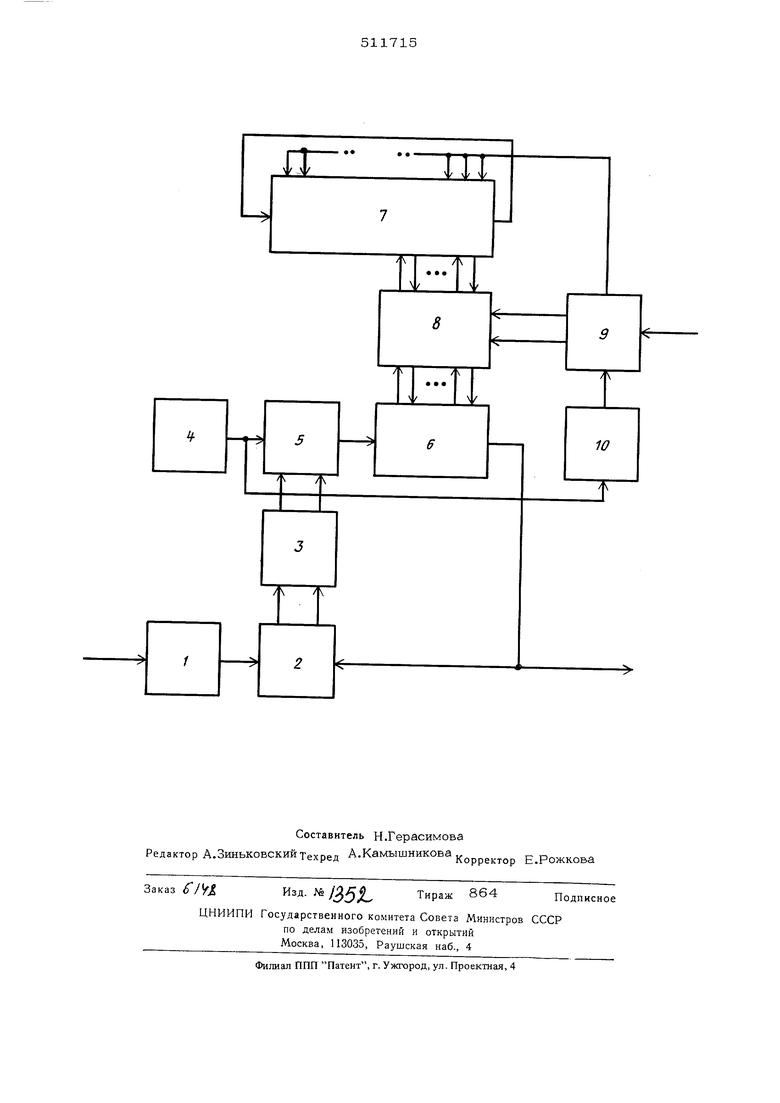

На чертеже приведена структурная электрическая схема устройства.

Устройство для синхронизации сигналов, содержит блок 1 для выделения сигналов синхронизации, фазовый дискриминатор 2, реверсивный счетчик 3, генератор 4, управитель 5, управляемый делитель 6, кольцевой регистр 7, блок 8 для перезаписи кода, формирователь 9 импульсов перезаписи и продвижения и делитель 10.

Компоненты 1, 2, 3, 4, 5, 6 устройства образуют известный тактовый синхронизатор. Выходы и установочные входы каждого разряда управляемого делителя 6 через блок 8 соединены с установочными входами и выходами соответствующих разрадов кольцевого регистра 7. Входы, предназначенные для управления режимом перезаписи код

и шина продвигающих импульсов кольцевого регистра 7 соединены с соответствующими выходами формирователя 9, один из входов подключен через делитель к выходу геvi:p,--ropa -4, ;:,7ори;: -- к оли:;у канальной сикхрокизаднп (не приведен).

Устройство работает следующим образом,

В устройстве происходит запоминание фаоьл опорного сигнала унравляемого делителя 6 в конце каждого временного канала и восстановление ее в начале этого же канала через цикл работы.

Пусть за время приема информации от одного и абонентов в соответствующем вре менном канале устранилось рассогласование между опорным и входным сигналами. При этом межау эталонным сигналом на выходе делителя 10 и опорным на выходе унравляемого делителя 6 устанавливается онреде денный фазовый сдвиг. Этому фазовому сдвигу соответствует определенный код управляемого делителя 6 в моменты появления импульсов на выходе делителя 10. Этот код в конце канального интервала заносится в кольцевой регистр 7 импульсом записи кода, вырабатываемым формирователем 9 и привязанным но фазе к эталонному сигналу, поступающему с вьгхода делителя Ю.

Установка фазы опорного сигнала в начале временного канала производится в обратном порядке импульсов, устанавливающим код в управляемом делителе 6. Этот импульс также совпадает но фазе с эталониым сигналом.

Про.авижение кода в кольцевом регистре 7 производится пачкой импульсов, следующей в промежутке времени между записывающим импульсом, и импульсом, устанавливающим код.

Число импульсов в пачке равно числу элементов кода. Выбор длины кольцевого регистра 7 производят с учетом количества каналов и требуемой точности запоминающей фазы.

формула изобретения

Устройство для синхронизации сигналов в многоадресных связных системах с временным разделением каналов, содержащее последовательно соединенные блок для выдления сигналов синхронизации, фазовый дискриминатор, реверсивный счетчик, управитель с генератором и управляемый делитель, выходы которого подключены к второму входу фазового дискриминатора, отличающееся тем, что, с целью ускорения фазирования по сигналам различных каналов, в него введены кольцевой регистр, блок для перезаписи кода, формирователь импульсов перезаписи и продвижения и делитель, причем выходы и установочные входы каждого разряда управляемого делителя через блок для перезаписи кода соединены с установочными входами и выходами соответствующих разрядов кольцевого регистра, а управляющие входы блока для перезаписи кода и щина продвигающих импульсов кольцевого регистра соединены с соответствующими выходами формирователя импульсов перезаписи и продвижения, подключенного к выходу генератора через делитель.

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации сигналов | 1975 |

|

SU552719A2 |

| Устройство синхронизации сигналов | 1981 |

|

SU1021005A2 |

| Устройство для синхронизации равнодоступных многоканальных систем связи | 1975 |

|

SU563736A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1987 |

|

SU1478363A1 |

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1982 |

|

SU1030986A1 |

| Устройство синхронизации сигналов | 1975 |

|

SU536611A2 |

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1987 |

|

SU1469562A1 |

| Устройство поэлементной синхронизации | 1985 |

|

SU1319301A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

8

f

Авторы

Даты

1976-04-25—Публикация

1974-01-28—Подача