Изобретение относится к радиосвязи и может использоваться в многоканальных синхронноадресных системах связи с временным делением каналов.

Известно устройство цикловой синхронизации, содержащее последовательно соединенные регистр сдвига, дешифратор, узел фазирования, распределитель 1. .

Однако такое устройство не обеспечивает достаточной точности синхронизации, . . .

Наиболее близким к изобретению по технической сущности является устрой9ТВО цикловой и канальной синхрони- . зации для равнодоступной многоадресной системы радиосвязи, состоящее из фазового дискриминатора, формирователя тактовых импульсов, генератора, дешифратора сигнала.цикловой синхронизации, распределителя каналов,. переключателя и блока уплотнения. Устройство содержит также блок незав СИМОЙ синхронизации, включенный межд тактовым входом и выходом дешифратор сигнала цикловой синхронизации, тактовьим и пусковыми в содами и промежуточным выходом распределителя каналов, тактовым входом блока уплот нения, входом фазового дискриминатор и соединенный по коммутируемым входам с выходами генератора и формирователя тактовых импульсов, блок запоминания фазы, включенный между выходом переключателя и тактовым входом распределителя каналов, и последовательную цепь, состоящую из формирователя управляющих импульсов, счетчика декоррелированных сигналов цикловой синхронизации и генератора автономных сигналов цикловой синхронизации, включенную между выходом дешифратора сигнала цикловой синхронизации и пусковым входом распредедителя каналов 2,

Однако это устройство не обеспечивает достаточной точности синхронизации, так как выделение импульсов синхронизации обеспечивается лишь при полном совпадении комбинации, записанной в регистр, с комбинацией, на которую настроен дешифратор. Поэтому при искажении одного символа в синхронизирующем сигнале теряетея информация, используемая для фазовой автсупод стройки.

Цель изобретения - повышение точности синхронизации.

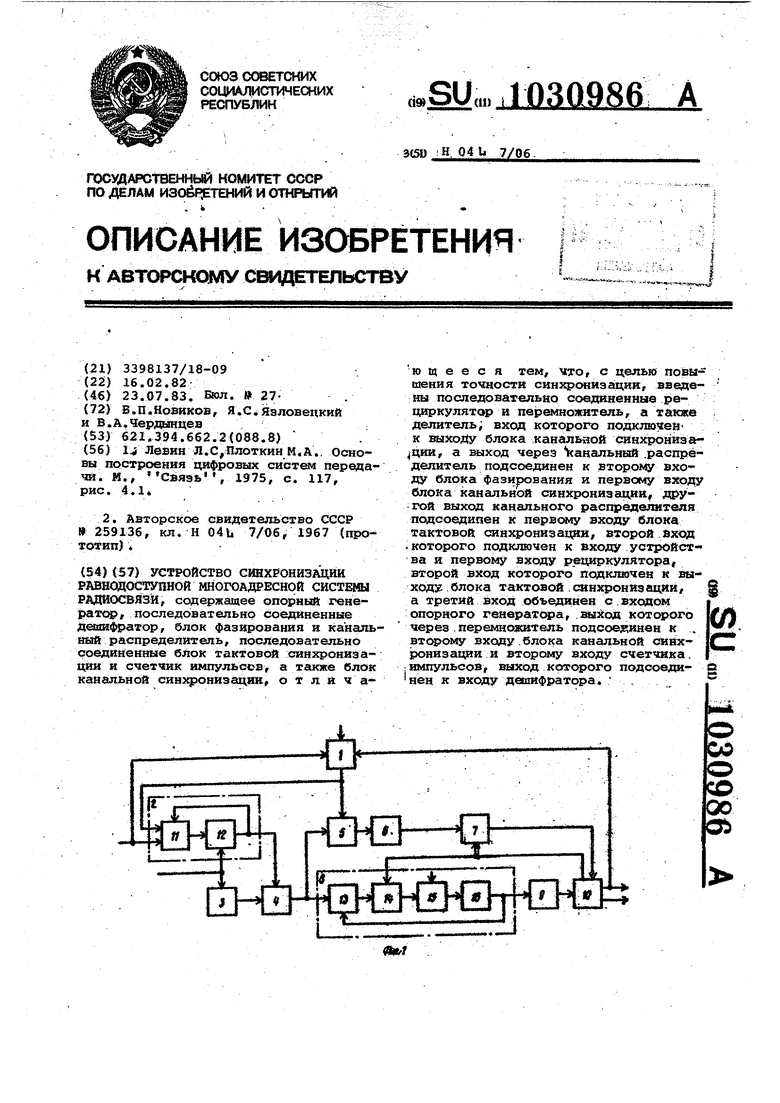

Для этого в устройство синхронизации равнодоступной многоадресной системы радиосвязи, содержащее опорный генератор,- последовательно соединенные дешифратор, блок фазировани и канальный распределитель, последовательно соединенные блок тактовой синхронизации и счетчик импульсов, а также блок канальной синхронизации,

введены последовательно соединенные рециркулятор и перемножитель, а также делитель, входкоторого подключен к выходу блока канальной синхронизации, а выход через канальный распределитель подсоединен к второму входу блока фазирования и первому входу блока канальной синхронизации, другой выход канального распределителя подсоединен к первому входу блока тактовой синхронизации, второй вход которого подключен к входу устройства и первому входу рециркулятора, второй вход которого подключен к выходу блока тактовой синхронизации, а третий вход объединен с входом опорного генератора, выход которого через перемножитель подсоединен к второму входу блока канальной синхронизации и второму входу счетчика импульсов, выход которого подсоединен к входу дешифратора.

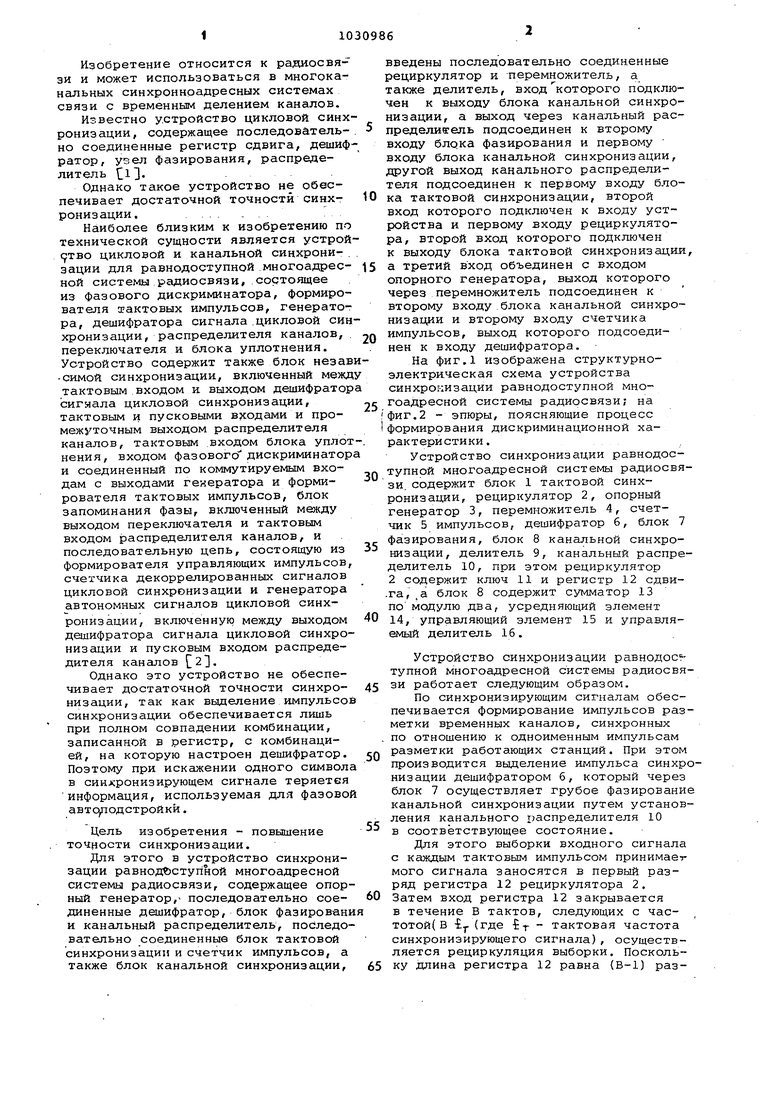

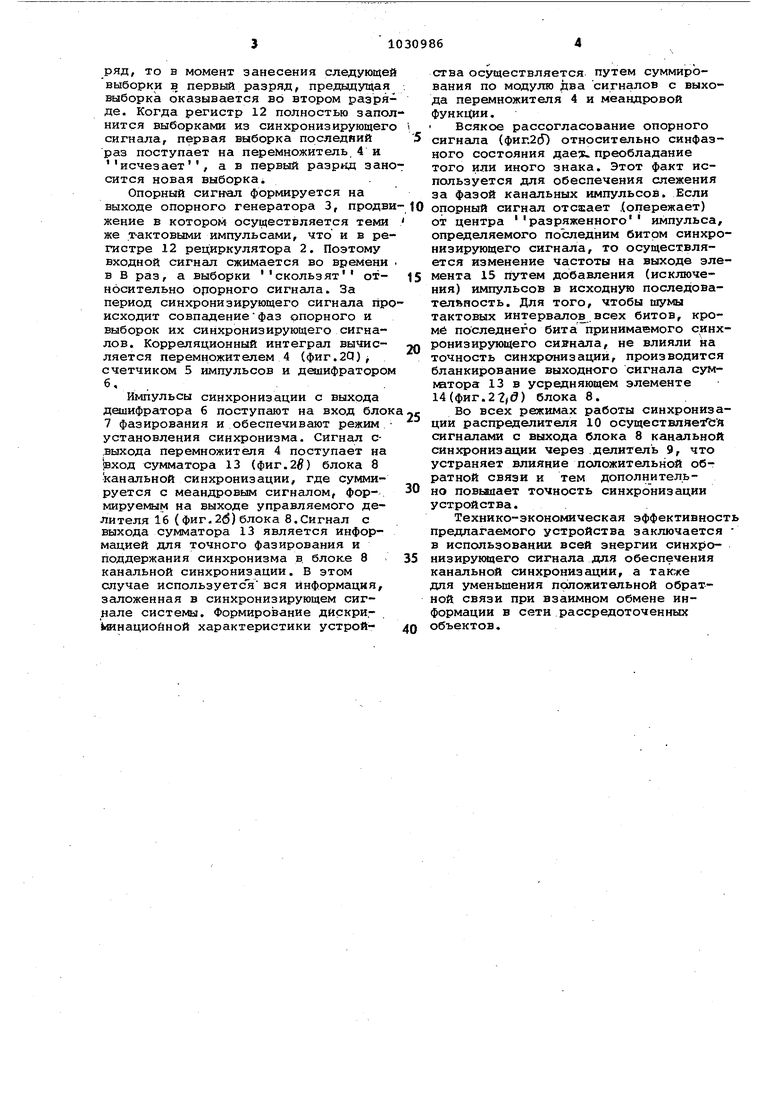

На фиг,1 изображена структурноэлектрическая схема устройства синхронизации равнодоступной многоадресной системы радиосвязи; на фиг.2 - эпюры, поясняющие процесс формирования дискриминационной характеристики .

Устройство синхронизации равнодоступной многоадресной системы радиосвязи. содержит блок 1 тактовой синхронизации, рециркулятор 2, опорный генератор 3, перемножитель 4, счетчик 5 импульсов, дешифратор б, блок 7 фазирования, блок 8 канальной синхронизации, делитель 9, канальный распределитель 10, при этом рециркулятор 2 содержит ключ 11 и регистр 12 сдвига,,а блок 8 содержит сумматор 13 по модулю два, усредняющий элемент 14, управляющий элемент 15 и управляемый делитель 16.

Устройство синхронизации равнодос тупной многоадресной системы радиосвязи работает следующим образом.

По синхронизирующим сигналам обеспечивается формирование импульсов разметки временных каналов, синхронных по отношению к одноименным импульсам разметки работающих станций. При этом производится выделение импульса синхронизации дешифратором б, который через блок 7 осуществляет грубое фазирование канальной синхронизации путем установления канального распределителя 10 в соответствующее состояние.

Для этого выборки входного сигнала с каждым тактовым импульсом принимает мого сигнала заносятся в первый разряд регистра 12 рециркулятора 2. Затем вход регистра 12 закрывается в течение В тактов, следующих с частотой ( В -Е (где тактовая частота синхронизирующего сигнала), осуществляется рециркуляция выборки. Поскольку длина регистра 12 равна (B-l) разряд, то в момент занесения следующе выборки в первый разряд, предьщущая выборка оказывается во втором разря де. Когда регистр 12 полностью запо нится выборками из синхронизирующег сигнала, первая выборка последйий раз поступает на перемножитель.4 и исчезает, а в первый разркд зан сится новая выборка. Опорный сигнал формируется на выходе опорного генератора 3, продв жение в котором осуществляется теми же т-актовыми импульсами, что и в ре гистре 12 рециркулятора 2. Поэтому входной сигнал сжимается во времени в В раз, а выборки скользят относительно опорного сигнала. За период синхронизирующего сигнала пр исходит совпадениефаз опорного и выборок их синхронизирующего сигналов. Корреляционный интеграл вычисляется перемножителем 4 (фиг.20) счетчиком 5 импульсов и доиифраторо 6v . Импульсы синхронизации с выхода дешифратора б поступают на вход бло 7 фазирования и обеспечивают режим установления синхронизма. Сигнал с.выхода перемножит едя 4 поступает на (ВХОД сумматора 13 (фиг.2) блока 8 канальной Синхронизации, где суммируется с меандровым сигналом, формируемым на выходе управляемого делителя 16 (фиг.2б) блока 8.Сигнал с выхода сумматора 13 является информацией для точного фазирования и поддержания синхронизма в блоке 8 канальной синхронизации. В этом случае используете вся информация, заложенная в синхронизирующем сигнале системы. Формирование дискри, данациойной характеристики устройства осуществляется путем суммирования по модулю два сигналов с выхода перемножителя 4 и меандровой функции. Всякое рассогласование опорного сигнала (фиг.2(5) относительно синфазного состояния даедг. преобладание того или иного знака. Этот факт используется для обеспечения слежения за фазой канальных импульсов. Если опорный сигнал отстает .(опережает) от центра разряженного импульса, определяемого последним битом синхронизирующего сигнала, то осуществляется изменение частоты на выходе элемента 15 путем добавления (исключения) импульсов в исходную последовательность. Для того, чтобы шумы тактовых интервалов всех битов, кроме последнего бита принимаемого синхронизир5пощего сигнала, не влияли на точность синхронизации, производится бланкирование выходного сигнала сумN&Topa 13 в усредняющем элементе 14(фиг.22() блока 8. Во всех режимах работы синхронизации распределителя 10 осуществляез я сигналами с выхода блока 8 канальной синхронизации через делитель 9, что устраняет влияние положительной обратной связи и тем дополнительно повьяаает точность синхронизации устройства. Технико-экономическая эффективность предлагаемого устройства заключается в использования всей энергии синхронизирующего сигнала для обеспечения канальной синхронизации, а таюке для уменьшения положительной обратной связи при взаимном обмене информации в сети рассредоточенных объектов.

Режин

сикдк)эмыи отставания

IKXUff

AfXUff

„J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1987 |

|

SU1478363A1 |

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1987 |

|

SU1469562A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство для синхронизации равнодоступных многоканальных систем связи | 1975 |

|

SU563736A1 |

| Устройство для приема дискретной информации | 1987 |

|

SU1501298A1 |

| УСТРОЙСТВО ЦИКЛОВОЙ и КАНАЛЬНОЙ СИНХР011ИЗАЦИИ | 1970 |

|

SU259136A1 |

| Устройство для синхронизации многоканальных равнодоступных систем связи | 1977 |

|

SU681566A2 |

| ПРИЕМОПЕРЕДАЮЩАЯ АППАРАТУРА ШИРОКОПОЛОСНЫХ ПСЕВДОСЛУЧАЙНЫХ СИГНАЛОВ | 1979 |

|

SU1840119A1 |

| Устройство синхронизации многоканальных равнодоступных систем связи | 1978 |

|

SU758550A1 |

| Устройство синхронизации многоканальных равнодоступных систем связи | 1978 |

|

SU745012A1 |

УСТРОЙСТВО СШХРОНИзХцИИ РАВНедОСИПНОЙ МНОГОАДРЕСНОЙ СИСТЕШЛ РАДЩОСВЯЗ, содержащее опорный генератс, последовательно соединенные дшоифратор, блок фазирования и канальНЁ1й распределитель, последовательно соединенные блок тактовой синзфонизации и счетчик импульссв, а также блок канальной синхронизации, отличающееся тем, что, с целью повышения точности синхронизации, вв едены последовательно соединенные рещфкулятор и перемножитель, а также делитель; вход котсфого подключен к выходу блока .канальгюй синхрониза ции, а выход через kaнaльн&Iй .распределитель подсоединен к второму входу блока фазирования и. первому входу блока канальной синхронизации, другой выход канального расп1ределителя подсоединен к nepscaay входу блока тактовой синзфоннзацни, второй.вхсщ которого подключен к входу устройства и первому ВХОДУ рехщркулятора, второй вход которого подключен к выходу блока тактовой.синхронизации, а третий вход объ цинен с.входом опорного генератора, . которого через . перемнс«китель подсое;Е;инен к , входу .блока канальной сйийхрониза191и и второму входу счетчика. ; ттульсов, выход которого подсоединен к входу дешифратора. ; . 00 о х эо зь

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Левин Л.С,Плоткин М.А., Основы построения цифровых систем переда11 чи | |||

| И., 1975, с | |||

| Аппарат для испытания прессованных хлебопекарных дрожжей | 1921 |

|

SU117A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| УСТРОЙСТВО ЦИКЛОВОЙ и КАНАЛЬНОЙ СИНХР011ИЗАЦИИ | 0 |

|

SU259136A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1983-07-23—Публикация

1982-02-16—Подача