1

Изобретение относится к запоминающим устройствам.

Известно оперативное запоминающее уст ройство с одновременным обращением к множеству ячеек памяти, содержащее накопитель, входы которого подключены к блоку записи-регенерации и адресному блоку, а выход - к блоку усилителей считывания, регистры чисел, входы которых соединены через элементы И с выходами блока усили- телей считывания, регистры маски, выходы которых подключены к входам блоков формирования масок.

Недостатком известного устройства является невысокая скорость работы.

Для увеличения быстродействия устройство содержит элементы ИЛИ, дополнительные элементы И, дополнительные регистр маски и регистры чисел, входы которых подключины соответственно к выходам одних доиопгнительных элементов И и к выходам одного из блоков формирования маски, а выходы через последовательно соединенные другие дополнительные элементы И и элементы ИЛИк входам блока записи-регенерации.

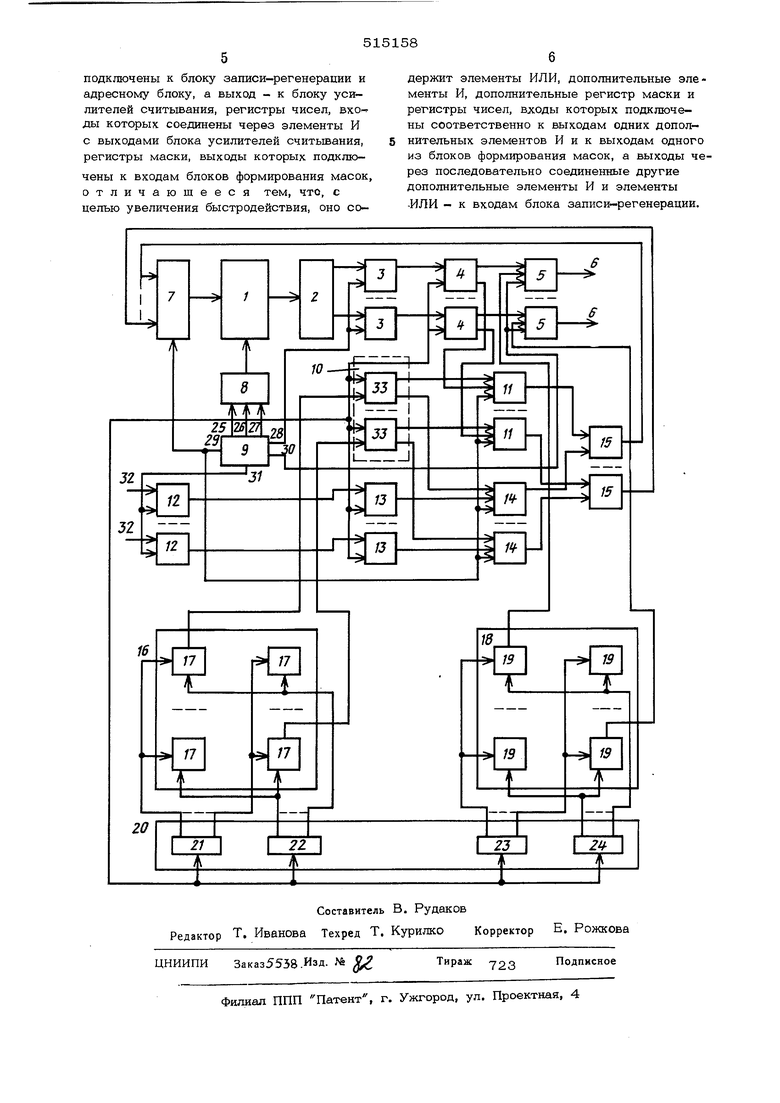

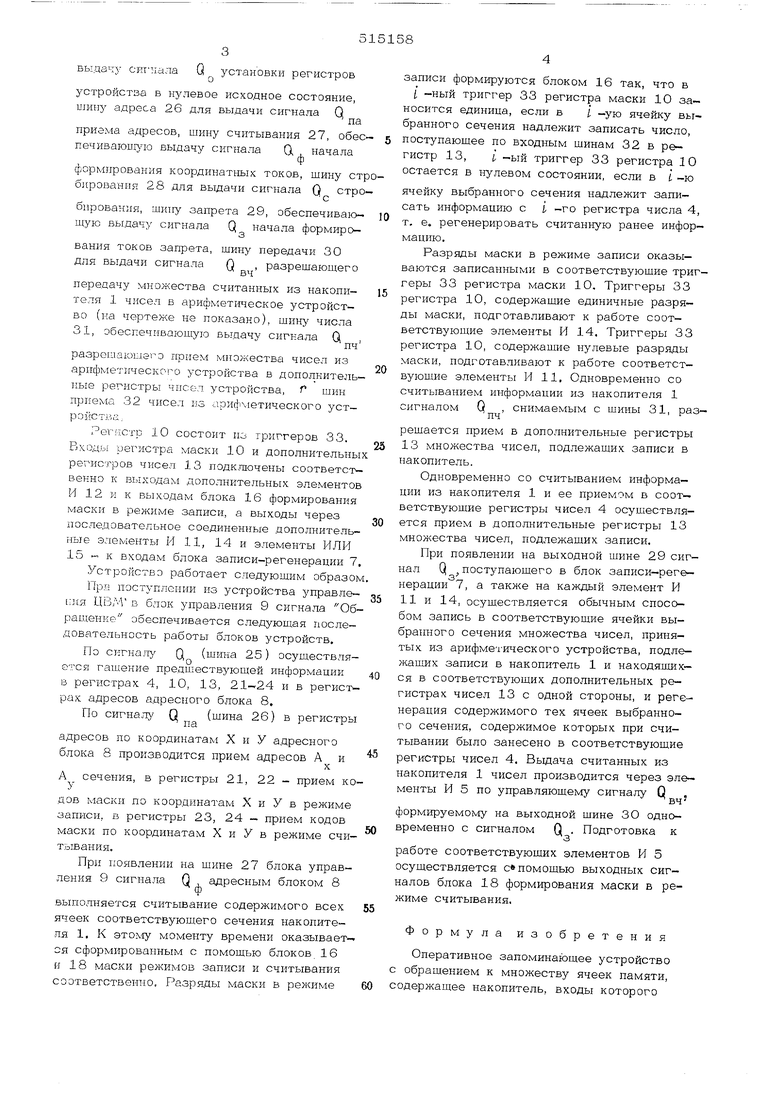

На чертеже изображена блок-схема предлагаемого устройства.

Устройство содержит накопитель 1, блок усилителей считывания 2, f элементов И 3 ( Г - разрадность ячеек памяти накопителя 1), регистры чисел 4, элементов И 5, щины выдачи чисел б, блок записи-регенерации 7, адресный блок 8, обеспечивающий выбор сечения накопителя, к которому производится обращение, блок управления 9, дополнительный регистр маски 10, 2 Л дополнительных элементов И 11 и 12, дополнительные регистры чисел 13, f дополнительных элементов И 14, Г эле ентов ИЛИ 15, блок 16 формирования маски в режиме записи, содержащий элементы И 17 блок 18 формирования маски в режиме считывания, содержащий элементы И 19, блок регистров 20, содержащий регистры маски 21 и 22 соответственно по координатам X и У для режима записи и регистры маски 23 и 24 соответственно по координатам X и У для режима считывания.

Кроме того, устройство содержит шину 25 начальной установки, обеспечивающую выдачу сигнала Q установки регистров устройства в нулевое исходное состояние, шину адреса 26 для выдачи сигнала О приема адресов, шину считывания 27, обес печиваюпг чо выдачу сигнала Q начала фОрмирования координатных токов, шину ст бирования 28 для выдачи сигнала Q стро бирования, шину запрета 29, обеспечиваюшую выдачу сигнала Q начала формирования токов запрета, шину передачи 30 для выдачи сигнала Q , разрешающего передачу множества считанных из накопителя 1 чисел в арифметическое устройство (на чертеже не показано), шину числа 31, обеспечивающую Bbiaa4v сигнала Q разрешающего поием множества чисел из арифметического устройства в допол пительные регистры чисел устройства, f шин приема 32 чисел из ариф| 1етического устройства. Регистр 10 состоит из триггеров 33. Вхо.цы регистра маски 10 и дополнительны регистров чисел 13 подключены соответственно к выходам дополнительных элементов М 12 к к выходам блока 16 формирования маски в режиме записи, а выходы через последовательное соединенные дополнительные элементы И 11, 14 и элементы ИЛ1-1 15 - к входам блока записи-регенерации 7 Устройство работает следующим образо Прн поступлении из устройства управлечия ЦВМ в блок управления 9 сигнала Об ращение обеспечивается следующая последовательность работы блоков устройств. По сигналу Q (щтина 25) осуществляется гашение предшествующей информации в регистрах 4, 10, 13, 21-24 и в регистрах адресов адресного блока 8. По сигналу Q (шина 26) в регистры адресов по координатам X и У адресного блока 8 производится прием адресов А и А сечения, в регистры 21, 22 - прием ко дов маски по координатам X и У в режиме записи, в регистры 23, 24 - прием кодов маски по координатам X и У в режиме считывания. При появлении на шине 27 блока управления 9 сигнала Q адресным блоком 8 выполняется считывание содержимого всех ячеек соответствующего сечения накопителя 1, К этому моменту времени оказывается сформированным с помощью блоков 16 и 18 маски режимов записи и считывания соответственно. Разря.ды маски в режиме записи формируются блоком 16 так, что в / -ный триггер 33 регистра маски 10 заносится единица, если в / -ую ячейку выбранного сечения надлежит записать число, поступающее по входным шинам 32 в регистр 13, i -ый триггер 33 регистра 10 остается в нулевом состоянии, если в i -ю ячейку выбранного сечения надлежит записать информацию с I -го регистра числа 4, т, е. регенерировать считанную ранее информацию. Разряды маски в режиме записи оказываются записанными в соответствующие триггеры 33 регистра маски 10. Триггеры 33 регистра 10, содержащие единичные разряды маски, подготавливают к работе соответствующие элементы И 14. Триггеры 33 регистра 10, содержащие нулевые разряды маски, подготавливают к работе соответствующие элементы И 11, Одновременно со считыванием информации из накопителя 1 сигналом Q , снимаемым с щины 31, разпчрешается прием в дополнительные регистры 13 множества чисел, подлежащих записи в накопитель. Одновременно со считыванием информации из накопителя 1 и ее приемом в соответствующие регистры чисел 4 осуществляется прием в дополнительные регистры 13 множества чисел, подлежащих записи. При появлении на выходной щине 29 сигнал Q поступающего в блок записи-регенерации 7, а также на каждый элемент И 11 и 14, осуществляется обычным способом запись в соответствующие ячейки выбранного сечения множества чисел, принятых из арифмечического устройства, подлежащих записи в накопитель 1 и нах:одящих- ся в соответствующих дополнительных регистрах чисел 13 с одной стороны, и регенерация содержимого тех ячеек выбранного сечения, содержимое которых при считывании было занесено в соответствующие регистры чисел 4. Выдача считанных из накопителя 1 чисел производится через элементы И 5 по управляющему сигналу Q , формируемому на выходной щине ЗО одновременно с сигналом Q . Подготовка к работе соответствующих элементов И 5 осуществляется с помощью выходных сигналов блока 18 формирования маски в режиме считывания. Формула изобретения Оперативное запоминающее устройство с обращением к множеству ячеек памяти, содержащее накопитель, входы которого

подключены к блоку записи-регенерации и адресному блоку, а выход - к блоку усилителей считывания, регистры чисел, вко-лы которых соединены через элементы И с выходами блока усилителей считывания, регистры маски, выходы которых подключены к входам блоков формирования масок, отличающееся тем, что, с целью увеличения быстродействия, оно содержит элементы ИЛИ, дополнительные элементы И, дополнительные регистр маски и регистры чисел, входы которых подключены соответственно к выходам одних допол- нительных элементов И и к выходам одного из блоков формирования масок, а выходы через последовательно соединенные другие дополнительные элементы И и элементы -ИЛИ - к входам блока записи-регенерации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с блокировкой неисправных ячеек памяти | 1981 |

|

SU1014033A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1287238A1 |

| Генератор псевдослучайных чисел | 1976 |

|

SU693408A1 |

| Устройство для формирования гистограммы случайных чисел | 1986 |

|

SU1388901A1 |

| Устройство для формирования видеосигнала | 1990 |

|

SU1741124A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU949721A1 |

| Логическое запоминающее устройство | 1977 |

|

SU674101A2 |

| Буферное запоминающее устройство | 1990 |

|

SU1833918A1 |

| Устройство для контроля хода программ ЭВМ | 1987 |

|

SU1430960A1 |

| СПОСОБ СЛЕЖЕНИЯ ЗА ОБЪЕКТОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2153235C2 |

Авторы

Даты

1976-05-25—Публикация

1974-10-07—Подача