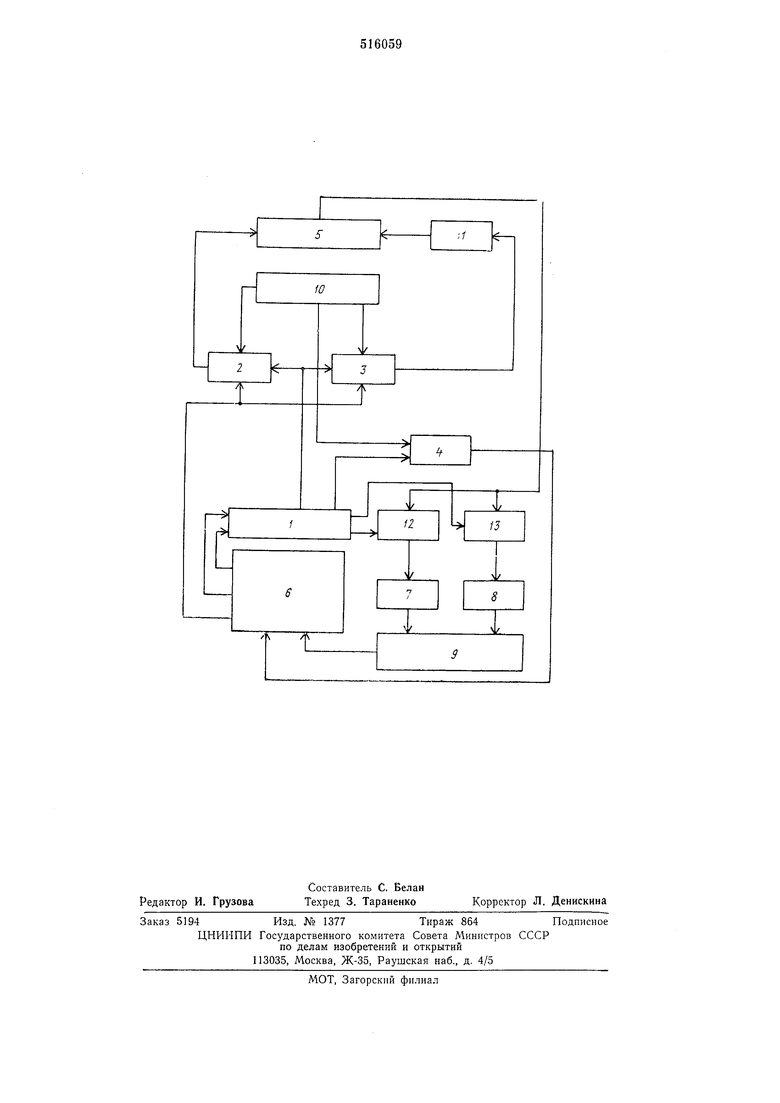

разру7да сумматора 2 присоединен к днскрнминптог)) 5 непосредственно, а р.1)1ход зкакогкяч) )Г13ряда сум;агора 3 - через 1пшорт(}) 11 Выход днск)нмннатора 4 соединен с б,локом (5 управления, а выход днскримннатора 5 - с логическими элементами 12 и 13, вторые входы которы-х связаны с измерителем 1. Выходы элементов 12 и 13 подключены к днфро-аналоговым преобразователям 7 и 8 кодов коордннат X и у, выходы которых соединены с регистрирующим блоком 9, связанным с блоком 6 управления. Выходы блока управления соединены с измерителем 1 и сумматорами 2 н 3. В эквинотенцкальную область входят узлоliiiie точки с равными нотендналами (с yчcтo i прннятого донуека). Достаточными условиями онределеиия точек области являются раiseHCTBo 31-гакоп потенцна; а уз. точкп и заданного уровня Sign .4 . Sign /1S, неравенство знаков разностей Sigп.4.,--(Л, ,,-(Л,,), -код потенциала узловой точки; -код заданногч) уро15ня искомоГ области;-коды верхнего н ппжпего урошш искомой области. Измерение потенциалов узловых точек проводится последовательно вдоль одной из icoординат, например ;с. В сумл аторы 2 и 3 от задатчика 10 подаются инвертироваиные значения кодов уровня искомой области: в сумматор 2 код - {/4 5-ЬДЛ , ), а в сумматор 3 код - (Л, ДЛ ). Код знакового разряда SignЛ,. подается па первый вход дискрн:.ипатора 4, на вход которого от измерителя 1 поступает ;од знакового разряда нотеинна.та уз.товой точки Sign.4 ,. . При разных знаках на входах дискршшнатор 4 выдает пулевой уровень и K0.:j, потенциала узловой точки не передается в су.мматоры 2 и 3. Блок G управления выдает команду па измерение и преобразование в цифровой код поте1П1,иала следующей узловой точки. При созпаденин знаков уровня об;гасти н потенциала уз.ювой очки SigпЛs --Sign.4,. (первый п|;нзпак нрннадлежностн точки к экнтютепцна.чькой области) дискрилишатор 4 подает единичпый уровень, который поступает в блок 6 управления. Блок управлення вырабатывает команду на перепись кода потенциала узловой точки из измерителя 1 в су.мматоры 2 и 3. В сумматоре 2 образуется разность Л ,. - (Л. +ДЛ . ), а в сумматоре 3 - разность А 1--(Л -АЛ ). Знаковые разряды этнх разностей подаются на дискриминатор 5, причем знаковый разряд из сумматора 3 предварительно инвертируется инвертором П. Если потенциал узловой точки укладывается в поле допуска задашюго уровня облает, т. е. Л,, ,. Л,, -ДЛ,, , то па входы дискримииатора 5 подаются одипакозые знаки (учитывая налнчне инвертора 11) н дискрпминатор 5 выдает единичный уровень, символизирующий второй признак принадлежпости точки к искомой эквинотенциа.тьной облаетн SignL4 ,-(Л ,-f ДЛ, ) 7- Sign,,. - (Л 5 -ДЛ ). Единичный уровень открывает логические элементы 12, 13 и на цифроаналоговые преобразователи 7, 8 поступают коды координат узловой точки х и у. Преобразователи 7 и 8 выдают паиряжения, иропорциональные этим кодам, отрабатываемые регистрирующим блоко1М 9. Пишущая каретка блока 9 устаиавливается в соответствующем положенин относительно координатных осей графика и отпечатывает символ точки эквипотенциальиых областей. Регистрцрующий блок дает в блок 6 управления сигнал «отработка, по которому блоком управления выдается команда па измерение потенциала следующей узловой точки. Если же нотенциал узловой точки выходит за нределы ноля допуска, т. е. Л ,. Л +ДЛ нлн, Л . , то на входы дискримииатора 5 подаются сигналы разной полярности, и на выходе дискриминатора 5 возникает нулевой уровень. Логические элементы 12 и 13 закрываютея. Блок унравления 6 дает команду на измереппе и анализ потенциала следуюпдей узловой точки. Поиск точек области вдоль координаты аналогичен описапному. Фор м у л а изобретения Уетройство для построепия эквипотенциальных областей, еодержащее цифро-аналоговые преобразователи, подключенные через региетрирующий блок к первому входу блока управления, одип из выходов которого соедииен с первыми входами сумматоров, другие выходы блока унравлеиия подключены к входам измерителя потенциалов, первый выход которого соединен с вторыми входами сумматоров, задатчик уровня эквипотенциальных областей, первый и второй выходы которого подключены к третьим входам сумматоров, отличающееся тем, что, с целью упрощения устройства и увеличения его быетродействия, оно содержит последовательно соединенные )п1вертор и первый дискриминатор знака, другой вход которого подключен к выходу первого су.мматора, выход второго сумматора подключен к входу инвертора, логические элементы, выходы которых соединены с входами цифро-аналоговых нреобразователей, причем первые входы логических элементов подключены к второму и третьему выходам измерителя потенциалов, вторые входы - к выходу первого дискриминатора знака, второй дискриминатор знака, выходом соединенный с вторым входом блока управления, а входы второго дискримииатора знака подключены к четвертому выходу измерителя потенциалов и к третьему выходу задатчика уровня эквипотенн.пальпых областей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой генератор функции | 1977 |

|

SU711556A1 |

| Частотный дискриминатор | 1985 |

|

SU1396241A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1322475A1 |

| Устройство для интегрирования функций | 1982 |

|

SU1070570A1 |

| Устройство для определения потенциала и напряженности поля короны постоянного тока | 1973 |

|

SU474821A1 |

| Устройство для интегрирования функций | 1984 |

|

SU1242993A1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ СИГНАЛОВ С ДВУХКРАТНОЙ ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 1991 |

|

RU2007886C1 |

| Устройство для преобразования координат | 1987 |

|

SU1460720A2 |

| Устройство для отображения векторных диаграмм на экране электронно-лучевой трубки | 1988 |

|

SU1541663A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

Авторы

Даты

1976-05-30—Публикация

1975-01-20—Подача