.Из :;бр--:-::-ение относится к области ,вычис-пттепънс, тек-плкн,

Извзстан фз -глЕцкональный преобреаователь содер-лашгсей регистр аг тумента, выходы .. которого соединены с п ;рвыми «ходами . але« мептол. И вь Х;оды которых соадинень чеPBS psr-ьето элреса и дцресный KOMMjTaTup со зходгм: : блока памяти, аыхс.цы которого и входы регистра аргумента соединены соотвотс. JSi-Ho с выходами и вхацами преобра- зивателй,

Недостатком таких функщк.кальных преобраэова.телей является ни. быслродейст:ВИР выборке табличных значаний фукк- ийй ,i3 ):.ока памяти в СБЯЙИ fc TSMj что . фстрмчг.рование ацресов табличных значений .«.а-1й осу:щестз 1яется в результате выпод- т.гания ., ряцз/ последозательных сравнений :-..одного аргумента со значениями ,аргумвнтае сооги тствующкми .смене mafa а,цресов таблич- гых :значенкй функций.

Ц-г.гь изо1:;ретения - повышение быстро.viOHCihiiH преобразователя.

Оост -р;очная цель достигается тем, что фуй:-.дй1,;нагАньгй преоб|эазоватсль содер-,

жит дешифратор и . Выходы. рвгис М ра aprjivieHTa с.оединены со входами дешиф раторт, выходы которого через шифратор соединены со вторыми входами элементов И.

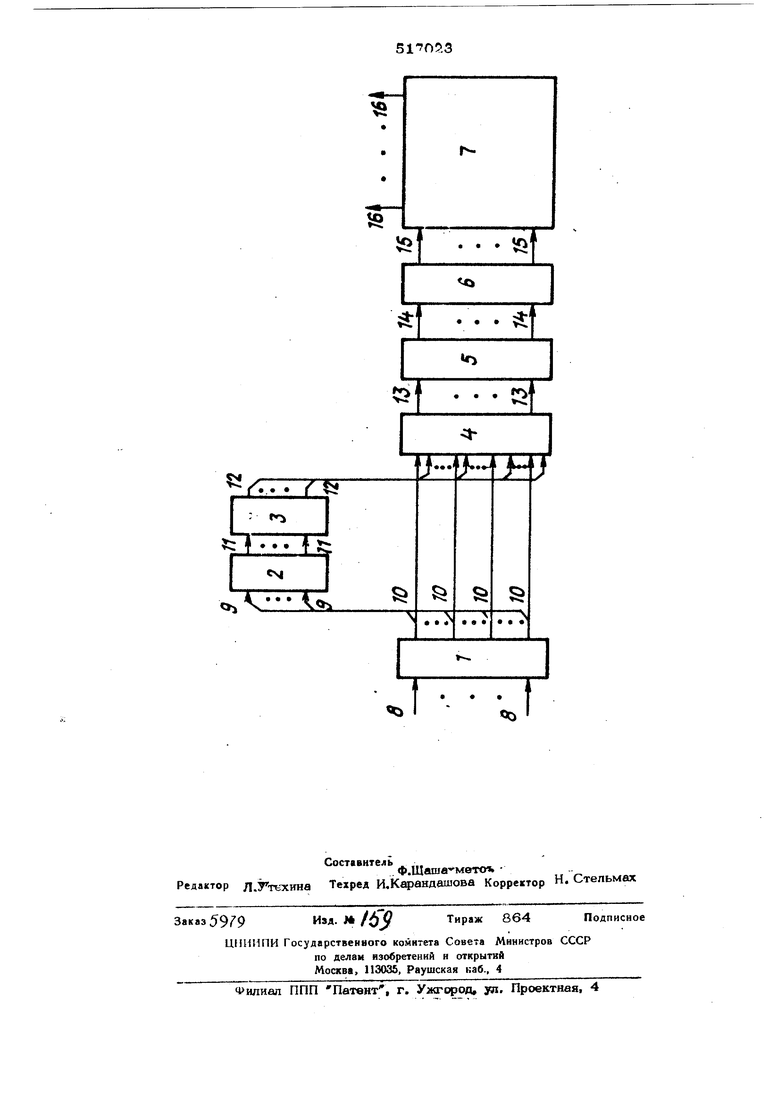

Блок-схема лреобразователя изображена на чертеже,

а Преобразователь родержит регистр .аргумента 1, дешифратор 2, шйфратор 3, элементы И 4, регистр адреса 5, .алресны коммутатор 6 ,-,: и блок памяти 7,

На чертеже обозначены: .8 - входы првр& разователя} 9 - входы дешифратора;, 10 первые входы элементов И| 11, 12 входы а выходы шифратора; 13«-16 - выхо ды соответственно элемй1тов И, регистра адреса, адресного ко:(«мутаторая .блока пемяти,

: Входа. 10 эяаментов И 4 подключены X выходим аргумента Г выходы.id. к регистр адреса 5, а входьг 12 к выходам шг..ратор 3, входы 11 которого че рез дешифратор 2 подключены к выходам. 9 регистра аргумента 1. Выходы 14 регисгра адреса 5 через г адресный коммуи. гатор;6 подключены к входам 15. блока памяти 7 Входами функционального npeo разователя являются входы 8 региоргра apry мента 1, а выходами - выходы 16 блока памярги 7. В блоке памяти 7 хранятся табличные значения вычисляемой ф}нкции, рассчитаннвге заранее для узловых значений аргумента т ( 1 ). . рти значения расаолагаготся в блоке памяти .о постоянно-переменн1лм шагом по адресам таким , .что дорес некоторой ячейки ггамяти Является а гументом Jсоответствующим ,трь-1У значению функции, которое хранится в данной ячейке. При этом диапазон изменения аргумента, например од) узловыми значениями ,f,(f-iij) разбивается на поддиапазоны. 0,Х,), ,),.. ...,1х.,, ).)j..., Х,, внутри которых шаг рас. положения узловых значений аргумента А; постоянен и равен соответственно Н Нр,..., Н д .. , а при. переходе из одного подциана зона в другой . удваивается, т. е. 1 - h, f qR kf - минимальньтй шаг, равный целой степени Р основания системы счисления (в ранном случае целой степени 2), т. е. К, 2 Величина k.. .и значения аргумента Х, ( Ti 18 R ) рассчитываются, исходя из здцанной погрешности приближения функцииf( X ) и порядка m интерполяционного многочлена, например, по следующей методике, Из равенства остаточного члена интерполяционного полинома Ньютона , fn -го nopsyuca заданной погрешности получим: L 1 ёг .;,-fna)/, fx)l где ,. . . p( f77Ti f - ; I ) / Vfcl . f -- Затем no значению || рассчитыве гся аиаченне loggK.lt , где J Q, С означает ближайшее целое н меньшее Q , и тем самым минимальный i узловых значений аргумен ;та.для подаиапазона , Л ). ЭначвйивТ . : .- . .Xj и другие, значения определяютсяв;рвз5ф хатв решения уроквевяб . / 1Л.. 0 Ч2:и Ггт;у« (;Щ Полученные .так UN, обрпаог/ значения Л, , 1, R .представляют собой, обшем случае, полноразрядные значения аргумента X , соответствующие смене (кратно целой степени 2) шага расяюложения -yairioBli объединйг-отся.загем в кножост во { Х, Г l7R 1 . Суммарное оборудог лигие .дешифратора 2, шифратора 3 и блока пвм.нти 7 от величины и кол.ччествд цодциапазоиеЬ рвзбиения аргумента Л С целью миннмнзаяни этого оборудования множество I Xf., 1, R ожет быть преобразовано в. {( , l)j)3$R таким образом, чтобы каждый из его элементов представлялся количеством разряпов, меньшим,чвм рааряднэсть регистра аргументя,., кроме того, для обеспечения заданной погрешности вычисления удовлетворял из условий; а)X X для функций (или участкой функций) с мояотонно-убывекмцей: f{) . при ступенчатом интерполирован НИИ (или монотонно-убывающей ) при интерполировании пордцка т О ) б)Xf, f, для функций (или участка функций) с монотонно возрастаюшей f( при ступенчатом интерп0ли{)ованяи (или с монотонно-возрастающей , / интерполировании nopjuuca ). Наиболее показательно рассмотреть задачу минимизации суммарного оборуаования, когда Б качестве дешиф|ватора 2 „ я шифратора 3 использован дополнительный блок памяти. Итак, необходимо минимизировать .где У и Уд ,- объемы блоков памяти 7 и дополнительного соответственно. Объем в битах дополнительного блока.паVg равен . V i ; где k - максимальнь Й из элементов . множества К.., , из кото ры есть значение разрядности соответствующих элементов множества /х . f I t R - разрадность ячеек дополн TenbSoroj блока ламяти,. . При обьеме дополнительного блока памяти, определяемом формулой (Д), объем блока памяти 7 минимален. Число узлов для каждого поддиапазона определяется отисхиением Jr .+f t f0,K при ДХ, Х,-0, ДЛ2 Х2-Д,..., ДХг ,... R 1- Rтах блока памяти 7 При этом обьем равен V 5 чис-;:о уллов где j -CV k ;. 2 1ФИ постоянно-переменном uiars, равное чнс; пу ячеек памяти, закк-гых табличными фуни .l-JUWePiC раэряпность блока памяти , . 7.„ Преобразование множества f„ ,„ -j в мвожес во Х , - f, 3 J. выполняется ; Б направлении уменьилгнмя k до . К I п сопровожпается уменьшением . V i како при этом объем блока памяти 7 увеi личивается за счет увеличения по,вднапааонов ; АХ в связи с необходимостью выполнен ния одного из условий а ( б). При этом гиожет иметь место дополнительное сокрашение V за счет умевьшения величины R , а следовательно и f . Величина R уменьшается до f , Tai ; как увеличение величины подциапааонсда при 1 фиксированной их сумме (О,1) воаможно ; лишь за счет сокращения их :1сла. В результате решения задачи мики- .мизации W получаем множество { X « : f-IDji каж,аый из элемецтов которого . : представляется |опреде«ен:яь м кодом груп-; пы старшкх разрядов регистра ергул1ента Ij К этой группе разрядов по.акл1Очены входы i дешифратора 2, .выходы которого через ши4ратор 3 подключены к входам элеменкэдв. I Й г4 таким образом, что входной код . ; дешифратора 2 соответствует .опреде.. числу младших разрядов регистра аргумента, j запрещаемых при передате через элементы И кода регистра аргумента 1 на вход ; ;регистра адреса 5. Рассмотрим пример. Hyci ь необходимо ; вычислить функцию . f С погрешI ностью не более - 2-1 при ступенча- iicM И1ггерполйрованки ( /71 О), Для этого I случая Б соответствии с изложенной метод :кой пЬл -чим: ) .,.;f-2- ;. р-ЬН,--Н,--2 . X, o.ioooiiiiibo

O.llOOiOllOtO

2 0,11100110000,

f

ОД11100110ОО,

0,11111001100,

f

ОД1111100110

2

0,1111111001,1

Kg 0,1 i 11-1111010 ;

X,.. U.illllllll01 }

.

I® Число, считанное из дополнительного

блока памяти, поступает на вход элементе

I , И 4 такшл образом, что его младший

S

) разряд поступает э мдацший разряд елэ ментов .И 4 и т. д. На входе элементов

53} И 4 будет результат логического со держимого регистра аргутчента 1 и числа считанного из дополнительного блока памяти. Число элементов И 4 равно разрядности дополнительного блока памяти (в - .

данном примере 4), .Содержимое остальных sinf)( Для вь числения стью, jHe Щ)ев1ышаюшей 2 , при ступеку том интерполировании и постоянноЦ шаге щ аргументу требуется обьем блока , 7 W -10 бит. при постояннопеременном ujsi W 14740 +.128 « 14868 .бит. Таким образом, ро втором случае, требуется в 1,4 раза меньший сум- марный збьем памяти. |СоотБетствье; кодЬв на входе дешифратора 2 и выхоае mratqjaTOpa 3 будет следующим:. старших paapstaoB регистра 1 пересыпается непосредственно .в регистр адреса 5. . Таким образом, при вычислении Si «4-х при Ле to.O.lOOlO) содержимое регист-i 1 пересылается в. регистр ад ра аргумента реса 5 без изменения,, при Х€ .0,1ОО1О„, 0,11О10) при пересылке блокируетсямйа.аший рааЕЙД содержимого аргумента .1, Х€ 0.11010, Э2 О11101 блокируе-Гся два младших разряда, при jfe О-ИЮ. o.iiiii yтри и npia Х€ I O.11111-,1)J ч . четыре мдадшкх разряда. Ячейки памяти . блока 7, не испольауемьш при вычисленпях Sm могут быть использованы при других вычислениях. Устройство работает следующим образом. Аргумент 7t при с гупенчат6м интерт полировании (или старшие разряды аргуме та при линейном или параболитнческом ин- терполирсшании) со входов 8 фушсционально го пр,еобразоватёля поступает на регист р аргумента 1. Затем по сигналу управления соответственно коду группы отаринх разрядов регистра 1 через 2 на - выходе шифратора 3 устанавливается onpeW, деленное состояние, соответственно которому аяемевты И блокнрткгг передачу о: , деленной группы младших разрядов регистра аргумента 1 в регистр дяреса 5.Соответстре но состоянию регистра а,ареса 5 из блока памяти 7 выбирается табличное значение функции и поступает на выходы 16 функционального гфеобразователя (рри интерполировании порядка t организуется эыбор ка еще Ifl соседних табличных значений 1ФУНКЦИИ с последующим интерполированием). Таким образом, данное устройство позволяет с высоким быстродействием опре ® ь значение функции по за,цанному аргументу. rVUyTOUTV Ф о р м у л а р е т е н и я - Функциональный преобразователь, содер жаший. регистр аргумента, выходы которо: го соединены с первыми ,Е 2 рда|ии элемен-, тов . выхояь которых соедине11ы через регистр адреса и адресный коммутатор со входами блока памяти, выходы которого и входы регистра аргумента соединены соответственно с выходами и входами преоб; разователя, отличающийся тем, что, с целью повьшения быстродействия преобразователя, он содержит дешифратор и шифратор; причем выходы регистра аргумен{ та соединены со входами дешифратора, вы- , I-ходы которого через шифратор срединены со вторыми входами элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования адресов табличных функций | 1974 |

|

SU518770A1 |

| Интерполятор | 1983 |

|

SU1129622A1 |

| Устройство для вычисления стандартных функций | 1980 |

|

SU942032A1 |

| Цифровой функциональный преобразователь | 1977 |

|

SU742947A1 |

| Интерполятор | 1984 |

|

SU1206805A1 |

| Цифровой Т-генератор функций | 1987 |

|

SU1423999A1 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1185329A1 |

| Интерполятор функций двух аргументов | 1984 |

|

SU1247893A1 |

| Цифровой Т-генератор функций | 1985 |

|

SU1256006A1 |

| Устройство для формирования адресов табличных функций | 1980 |

|

SU932496A1 |

Авторы

Даты

1976-06-05—Публикация

1974-07-01—Подача