(54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ АДРЕСОВ ТАБЛИЧНЫХ ФУНКЦИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU955082A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU983707A1 |

| Цифровой функциональный преобразователь | 1986 |

|

SU1339554A1 |

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

| Функциональный преобразователь | 1988 |

|

SU1541629A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1035604A1 |

| Устройство для управления тиристорным преобразователем | 1990 |

|

SU1777217A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ | 1988 |

|

SU1755650A1 |

1

Изобретение отнсюится к вычнспител) ной технике, в частности к устройствам для фсфмщ ования адресов табличных функпий, и может быть ноюльзовано щт nbci poeHmi специализированных вычислителей.

Известно устройство для восгфоизведевня функций одной пер« 4енкой, соде жашее регистр аргумента, блок памяти и регистр результата (1.

Недостатком устройства является боль шой объем памяти для представления табличных значений функции.

Известно также устройство, содержащее сумматор, блок памяти, регистр вр хтгмента, устройство сдвига, последова тельно соединенное с регистром аргумента 2.

Недостатке данного устройства является большой объем аппаратуры и, в частности, памяти.

Наиболее близким по своей технической сущности к предлагаемому является устройство для фор 4ирования табличных функций, содержащее регистр аргумента.

выходь которого соединены с первыми информационными шинами устройства, вто. рые информационные шины которого подключены к первым входам счетчика , выходы которого соединены с входами блока памяти, выходы которого через регистр результата связаны с первыми входЕц га сумматора, выходы которого поп ключены к вторым входам счетчика ещр са З.

Недостатком известного устройства является большой объем оборудоваввя из-за фрагментации информатге.

Цель изобретения - уменьшение объема оборудования, необходимого для воо произведения табличных значений фупкцяй, и увеличение быстродействия устройства.

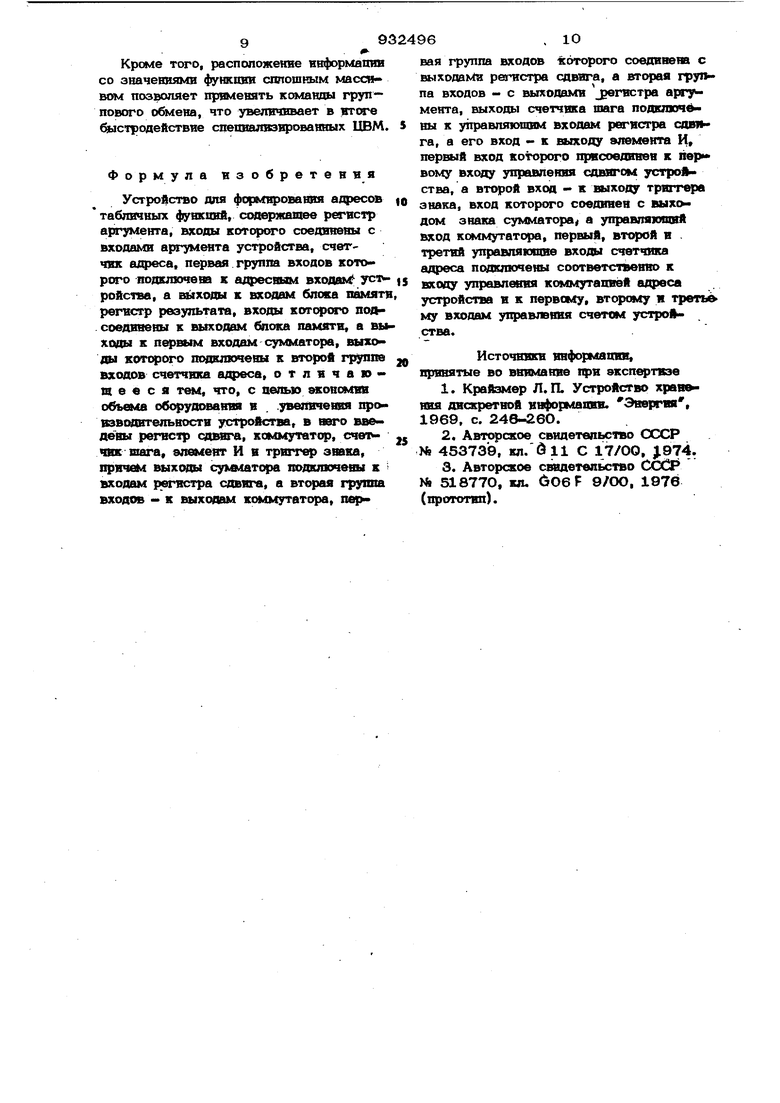

Поставпен1шя цель достигается том, что в устройство для формфоваиия адресов табличных функций, содержащее р гистр аргумента, выходы которого совгдинены с входами аргумента устройства, счетчик адреса, первая группа входов которого подключена к адресным входам устройства, а выходы к входам блока .памяти, регистр результата, входы кото.рого соединены к выхошм блока памяти, а выходы к первым входам сумматора, выходы которого подключеиы к группе входов счетчика адреса, введены регистр сдвига, коммутатор, счетчик шага, элемент И и триггер знака, причем выходы сумматора подключены к входам регистра, а вторая гругат входов - к выходам коммутатора, первая группа вхо дов которого соединена с выходами р&гистра сдвтЕга, а втсфая группа входов с выходами регистра аргумента, шлхооы счетчика шага подключены к упрешпяюшвм входам perwcipa сдвига, а его к выходу эдгамёнта И, первый вход кото рого присоедивеи к первому входу управ леввя савшчяй устройства, а второй вхоа к выхооу тршггера знака, вход соединен с выходсял иака q viMaTopa, а управляющий вход коммутатора П(вый, второй и третий управпякиове входы счет чика адфеса подключены соответственно к входу утравп&тя коммута1ШеЙ афеса устройства и к ne{mt)MS( второму и третье му входам уяравле&вя счетом устройетва В хфеялагасмом устройстве для форм мщ)овавия адфесов табличных фувклнй зшг чен футяяЛ xpatofFC в блоке памяти махх авлмв с постояиш -11ер амеввым шагом по ша чсевию артумента в постоянным ( по адресв л Здесь А.,, г «, соответствует смеве шага а{)гуме8та этом для ксокдой вз фуикш1й дтшзон из| неввя аргумента например, 0,1}, уэловыкш звачеюшмв А.Г 1,Р разбивается ва поодвшшэовыуЭ, А), СА, А г), ... AJJ,..., . рц,, l, ввутрв которых шаг по аргум в ту табличных эваченвй фуяковй постояв вый в Н, Н, Huf ...f Нм, а 1ФВ переходе вз одного поддватзоав в фугой удваивается. Шаг в подавала зоне взмёвеввя ajnryMeBTa задается как Н . 41 где }} минимальный шаг, раввый целой степени Р основания системы счвсленвя ( в давном случае целой степени 2), ,-ll- V(2) Велвчвиа значения А, h, рассчитываются, исходя вз заданной погрешности приближения функций f (Х) . Напрюдер, для функции с монотонно убывающим модулем производной ()()/ по следуюпюй методике. Из равенства остаточного члена интерполяционного полинома Ньютона нулевого порядка заданной погрешности получаем 11Чо1)1(3) Затем по значению fl определяется значение P-pfCogv-mt I ГД® означает ближайшее целое, не меньшее q , в тем самым минимальный шаг HI fi , по аргументу табличных значений функняв {(У для поддиапазона Со, Значение А в {футе значения А Гт Р1Я1ределяются в результате решения уравнений tl llirn.ft /Г(/5 - Нгг--1,к (4) ояучеввые таким образом значеввя прейставявют в общем случае оразрядвые звачеввя а{я умёнта. iecTBo узлов для каждого из поддианов ощэедеяают как , 6А;, uAj-Aj-A Ь А «.«., «I-AH. {Я1 атом обь&л в битах таблвпы сива) зт1юш(й каждой вз функций в , - количество звачений схшой вз фувкцвй щя постоявно ер мевномравное колвчест ву ячеек naMsiТВ, занятых табличными значениями этой .фуйкцив, 8-Д1о|- €С - разрядность ячеек памяти. ля реалвзапвв постоянно14ер«леиноага взмевенвя аргумента необходимо ить того, зваченвя аргумента ,R , соответствующее смене иапазона, и коды узлов Ау,7, кстоопределяются как +1 +1, (5) Дв7- код, соответствующий адресу расположения нулевого узла аргумента IB блоке памяти, для чего необходим объем памяти в битах, равный Выигрыш в объеме памяти при посто но переменном шаге по сраввению с по тояннь1М шагом оцеттается для каждой КЗ функций отношением г.. С.)г « ( 4j f« 2 R 4O iqFCTb, например, необходямо вычяо ,л1ггь функцюо S-tVi KX , X (ОД) с noiw решвостью ве более . ««а- . В соответствии с методикой для з даввых исходных даввых рассчитаны aBaWifflaf t -2-. Р-Ц, , ifClRse Ар7-KOOOOOOOOOOO А ЮДОООИШООа А ЮДЮОЮНОЮг АЗ ОД 1100110000А4 -ЮДЩООНООО Ау «ЮДЦЦООНООа А Ч)Д1111111111 1о-lOOOlllllOOj. 1 -11101111 1 110101, Т -llOl l4-lla Is-I ДА -ОДОООЦШОО, ДАа.-О.ОО111011ИО ДА, Ч),ООО1101О11О, ДА4 «O.OOOOllOlOOOa. ДА5 Ч),ООООО11010О | AAg -0,ООООО11ОО1Ь А -10001111101 А2 -1О1О11О11О1 А4 -1О11О10ОО11 ГД4 -1О1101100О1 Ау -1О11011О101 ICY- VIi + V t-J 4+Is - 1457 V-101457-14570 бит.лУ-йер 1OO бит. Ic-2-2048, Vc Ie t -2O48O би 2O480, . , 14670 Как видно, 9ков(ия оборудования в предлах емом устройстве достигается аа счет того, что иескольким значевиям аргумевта (с учетом заданной точности ) соответствует одва ячейка памяти с табличным значением функции. Это по воляет, в отличне от прототипа, таблич ные функции упаковьтать плотно по адр сам одно за другим (т. е. устраняется фрагментация памяти), образуя нетферы ный массив информатти. Коэффипиевт эко номии оборудования vдается формулами (6) и (7). На чертеже изображена тнкпиовальвая схема устройства для формировавия адресов табличных фушспий. Устройство регвстр 1 аргу мента, коммутатор 2, сумматсф 3, регистр 4 сдвиге, счетчюс 5 шага, 8Пв мевт И 6, триггер 7 знака, счбтчшс 8 адреса, блок 9 памяти, регвстр 1О ре эультата, входы 11 аргумевга ycrpoi ства, адресные входы 12 устройспа, первые и вторые входы счетчвса афеса соответственно 13 и 14 первый, вто-рой, третий, четвертый, пятый управляю шве входы устройства, соответствевво |15 19, первый, второй и третий управляющие вхошл счетчика адреса, соответственно 2О - 22. Счетчик 8 адреса может быть выполнев, вапря«(ер, яа триггерах, как р в живвый счетчик, у которого управляющий вход вход , второй управляющий вход вход +2, а третий управляющий вход - вход -2. Счетчик афеса обеспеч1шает прием внфсфмашт по одвому вз двух вапрйвле ввй: или с адресных входов 12 усгроАс ва, или с выходов сумматора, т. в. crei чик 8 адреса может работать как регистр. Регистр сдвига может б1йть построев, например, ва триггерах, шт на мгаме тах И, во в последнем случае ва его ш-ь хооах необхошмо поставить схемы с памятью, так как сумматор 3 преотьлагается комбинапнонного типа. Рассматрвваем работу устройства фор М1фования ислолвительвых адресов та& личных фувкций ва примере реалвэашш . функции с монотонно убывающим модзглем тфоизвоавой. В исходвом состоя ВИИ счетчик 5 шага обвулев, счетчик 8 адреса тоже, состояние остальных 9Л«девгов произвольво. В устройстве для форм1фовавия адресов табличных фувкоий аргумевт X по входам 11 аргумевта пересылается ва регистр 1 аргумевта. На счетчик 8 а/феса по адресным входам 12 устройства пересылается а ресная часть команды функция, означающая вычисление функции от аргумевта Х« Содержиь4ое- счетчика 8 адреса является исполнительным адресом, по которому находится в памяти первое yrtnoBoe значение A-f, соответствующее поддиапазону CO,AI кзменетгя аргумента. По содержимому счетчика 8 адреса из блока 9памяти на регистр 10 результата выбирается первое узловое значение аргумента AI , которое поступает на первую группу входов сумматора 3. Одновременно на вторую группу входов сумматора 3 с выходов коммутатора 2, по сигналу логической 1 с управляющего входа 16 устройства, поступает содержимое регис ра 1 аргумента, и на сумматоре 3 вычисляется разность (х-А), при этом значение знакового разряда сумматора 3 фиксируется триггером 7. Если знак (х-А) минус, на триггере 7 фиксируется логический О . На управляющий вход 15 устройства подает ся сигнал логическая 1, пй вход сче- чика 5 шага элемента И 6 поступает логический О , состояние счетчика не изменяется, счетчик обнулен. На третий управляющий вход 22 счетчика 8 ащ са с управляющего входа 19 устройства подается сигнал -2. Содержимое счет чина уменьшается на два - это всятопдательиый адрес, по которому из ока 9 памяти считывается значение аргумента Ад, последнее заносится аа регистр Ю результата и поступает на першле входы сумматора 3, где определяется разность (X-AQ), она передается и запоминается в регистре 4 саеяята. На первый управпяюшвй вход 29 сче-р чика 8 адреса поступает сигнал , из бл(жа 9 памяти считывается код узло вого значения аргумента АО. который поступает через регистр 1О результата на первые входы сумматора 3. На управляющие входы 16-19 устройства подают сигнал логический О . Коммутатс 2 пропускает на второй вход сумматора информацию с выходов регистра 4 сдвига, происходит сложение, инфо; мация с выходов сумматора передается на счетчик 8 адреса, по содержимому последнего из блока 9 памяти вабщлет ся значв П1е функции (х) которое заносится на регистр Ю результата. Если знак разности (х-А.) плюс, триггер 7 фиксирует логическую 1. На управляющий вход 15 устройства подают сипшл логическая 1, элемент И 6 выдает на вход счетчика 5 шага сигнал , содержимое счетчи ка увели гавается на единицу. На второй управляющий вход 21 счетчика 8 адреса подают сигнал +2, считывает ся значение аргумента А, которое через регистр Ю результата поступает на первые входы сумматора 3, при этом на вторые входы сумматора через кок мутатор 2 подают значение аргумента X . Определяется разность (х-Ду,). Если ее знак +, то он фиксируется триггером 7, как логическая 1, На управляющий вход 15 устройства подают логическая 1. С выхода элеменсигналв счетчик 5 шага выдается сигта И 6 нал и т. д. до полного перебора узловых значений A( ),или пока не будет найдена отрицательная разность (X-AJ,). в последнем случае на третий управл$по1Ш1й вход 22 счетчика 8 адреса поотупает сигнал -2. По содержимому счетчика из блока 9 памяти считывается зйаченве аргумента А и поступает через регистр 10 результата на первые входы сумматора 3, при этом на вторые входы сумматора через коммутатор 2 подается значение аргумента X . Опр&дёляется разность (х-А), в регистре 4 сдвига эта разность сдвигается на tb -1) разряде (содержимое счетчика 5 шага в данной случае равно Ь-1) н запомишется на его выходах. Далее на перклй згправпякжтй вход 2О счетчика 8 ащгеса яодается сигнал , считывается код узлсчвого значения аргумента Ау,, котофый передается через регистр 10 р зупьтата на первые входы сумматора 3. На утфавпяюшве входы 16-19 устройства подается сигнал логический О . Коммутатор 2 пропускает на вторью входы суммвтора 5 информашоо с выходов регистра 4 одвига. Происходит сложение, результат которого передается на счетчик 8 ащюса. По содержяь(ому последнего из блока 9 памяти выб фается значение функции fOl/ ааносется на регистр 10 результата. Для функций с монотонно-возрастаюшей производной (ii) процесс формированкя исполнительного адреса (содержимого счетчика 8 адреса) сгодится к описанному при определении знака разности (). Таким образом, использование в предлагаемсйл устройстве формирования адресов табличных функций с . постоянным шагом по а/фесам v постоянно-переменным щагом по аргументу дает экономию объема оборудовантга. Для элементарных тригонометрических функцийэкономия объема об14)удования приблизительно равна 2О-4О%. кроме того, распопоженве внформапив со значеви51мв функпви сплошиым масспн вом позволяет пршлевять команды группового обмена, что увеличивает в итоге стродействие сцетшлиэированных ЦВМ Формула изобретения Устройство для формфовашя адресов табличных функций, сопержащее регистр аргумента, входы соединены с входами аргумента устройства, счетчик адреса, первсм группа входов кото рого подключена к адресным входам уст ройства, а выходы к входам блока памяти регистр результата, входы которого попсоединены к выходам ока памяти, а BI ходы к первым входам сумматора, выхо ды которого подключены к второй группе входов счетчика адреса, отличающееся тем, что, с пелью «сонсмии объема оборудования и . .увеличешп щм юводительности устройства, в него введены регистр сдвига, коммутатор, сче1 чвк шага, алемеш И и трип знака, причем выходы суъал&гарл подключены к входам регистра сдвига, а вторая группа входов - к выходам коммутатора, первая группа входов которого соединена с выходами рег истра сдвига, а вторая rpyiv па входов - с выходами регистра аргу мента, выходы счетчика шага подклжп ны к управляющим входам регистра сдвига, а его вход - к выходу алемента И, первый вход которого присоедииен к hepw вому входу управлення сдвигом ycrpoJ ства, а второй вход - к выходу триггера знака, вход которого соединен с выходом знака сумматора а управляющий вход коммутатора, первый, второй и третий управляющие входы счетчика адреса подключены соответственно к восолу управления коммутацией адреса устройства и к первому, вторюму и треть0 му входам управления счетом устройства. Источники информации, принятые во внимание при экспертизе 1.Крайзмер Л. П. Устройство хранения дискретной информашт. Энергия, 1969, с. 24в-2бО. 2.Авторское свидетельство ОССР № 453739, кл. б11 С 17/00, J.974. 3.Авторское свидетельство СССР № 51877О, кл. (лОбР 9/ОО, 1976 (прототип).

Авторы

Даты

1982-05-30—Публикация

1980-07-11—Подача