ннк импульсов калибрюванной частоты через вентили подключен ко входам третьего и четвертого блоков сдвига, другие входы которых соединены соответственно с выходами Элементов задержек управляемых делителей частоты, а выходы - со счетными входами вычитающих счетчиков делителей.

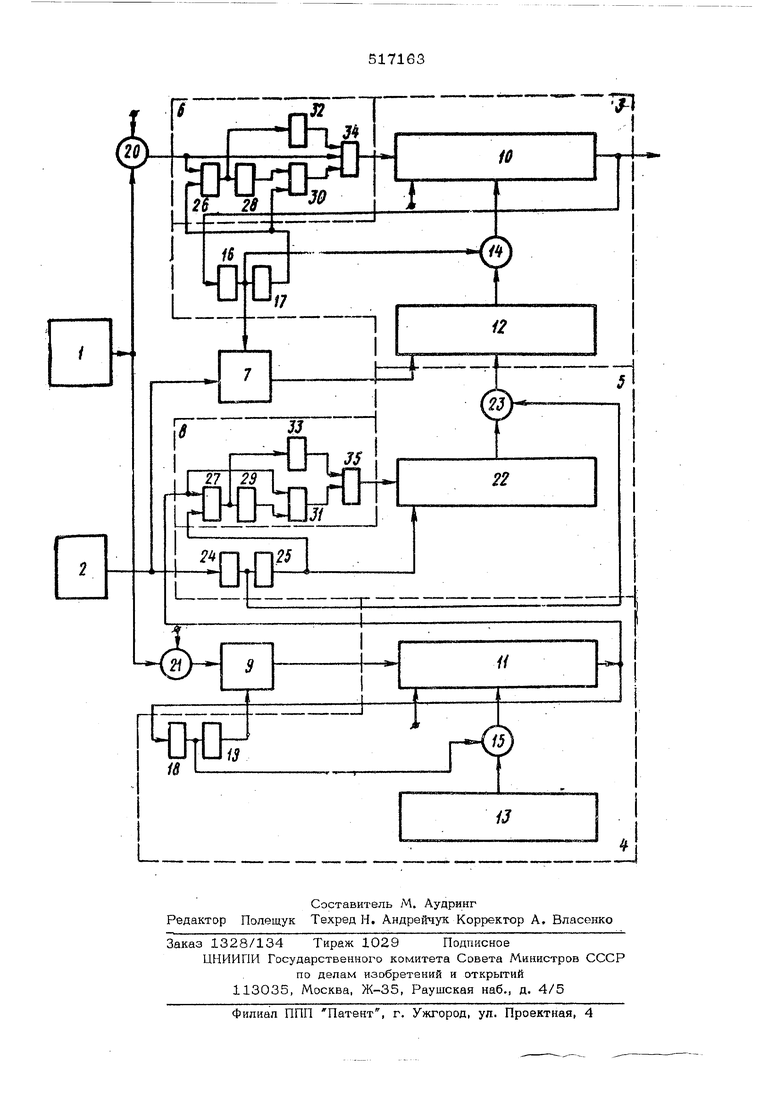

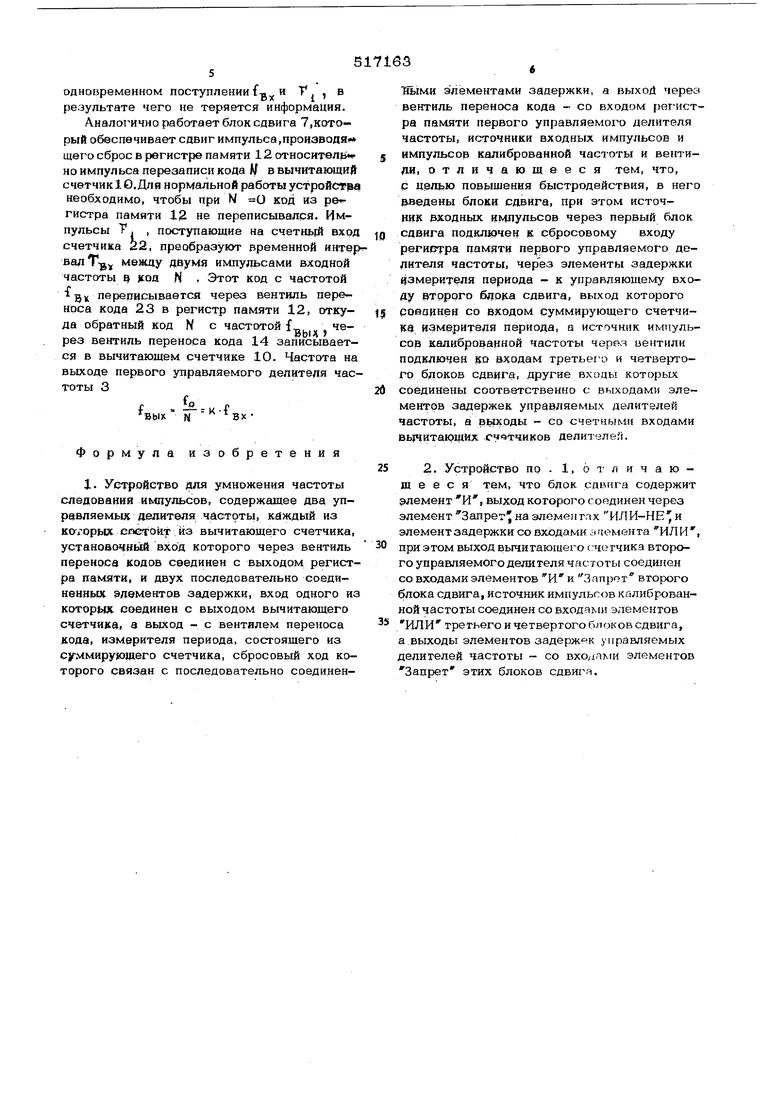

На чертеже изображена структурная схема устройства.

Устройство содержит источник калибров аиной частоты 1, источник входной частоты 2, управляемые делители частоты 3 н 4, измеритель периода S, блоки сдвига 6-9

Управляемые делители частоты содержат вычитающие счетчики 1О и И, регистры памяти 12 и 13, вентили переноса кодов 14 и 15, элементы задержек 16-19 и вентили 20 и 21,

Измеритель периода 5 содержит суммирующий счетчик 22, вентиль переноса кода 23 н элементы задержек 24 и 25. В блоки сдвига входят элементы И 26 и 27, элемент запрета на элементах ИЛИ-НЕ 28 и 29, И 30 и 31, элементы задержки 32 и 33, элементы или 34 и 35.

Устройство работает следующим образом.

Перед началом работы вычитающие счетчики 1О и 11 устанавливают в код 2 -1 ( И -число разрядов), суммирующий счетчик 22 и регистр памяти 12 - в нулевое состояние. Затем по сигналу Пуск , открывающему вентили 2 О и 21, на счетные входы вычитающих счетчиков 10 и11 начинают поступать через блоки сдвига 6 и 9 им. пульсы от источника импульсов калиброванной частоты 1 с частотой Q . Во втором управляемом делителе частоты 4 эта частота делится на коэффициент к,устанонуленный в регистре памяти 13. Первый счетный импульс { поступает через элемент ИЛИ- 34 блока сдвига 6 на счетный вход вычитающего счетчика 10. Этим импульсом ; счетчик переполняется и на его выходе появляется импульс, которь1й

через элемент задержки 16 поступает на управляющие входы вентиля переноса кода 14, через который в вычитающем счетчике 1О переплсывает обратный код числа N хранящегося в этот момент 6 регистре, памяти 12.

Затем импульс управления через элемент задержки 17 поступает на входы элементов И 26 и 30 блока сдвига 6. Если в этот момент на с первом входе блока сдвга 6 оказьшается импульс f Q , этот блок обеспечивает сдвиг по времени одновременно прищедших импульсов счета и управлени Срабатывает элемент И 26, и на его вы

ходе появляется сигнал, который попадает на элемент задержки 32 и элемент ИЛИ-НЕ 28, Задержанный элементом задержки 32 импульс затем поступает через элемент ИЛИ 34 на счетный вход вычитающего счетчика 10, Сигнал, поступающий на элемент 28, снимает управляющий сигнал :а его выходе, и импульс управления через элементы И 30 и ИЛИ 34 е счетчик 10 не проходит.

ЕСЛИ же сигнал управления и счетный импульс поступают на элемент И 26 одновременно, он не срабатывает, на выходе элемента ИЛИ-НЕ 28 имеется сигнал, элемент И ЗО подготовлен к срабатыванию, поэтому сигнал управления проходит на счетный вход вычитающего счетчика 10 через элементы И 30 и ИЛИ 34.

Благодаря блокам сдвига при одновременном поступлении сигналов управления и сченых импульсов сбоев в работе ij потерь информации не происходит.

Импульс, поступивший на вход вычитающего счетчика- 10, добавляет в него единицу, т.е. формирует дополнительный код числа N. Следуйщий импульс на выходе появляется через 2 -( N ) - N импульсов. Период следования импу-льсов на выходе первого управляемого делителя частоты 3 равен Nt о ,а д,у Го/Ь . Аналогично работает второй управляемый делитель частоты 4, на выходе которого Tj -fg/Я. Импульсы с частотой Т. поступают на счетный вход суммирующего счетчика 22 через блок сдвига 8.

Измеритель периода 5 работает следующим образом. Импульс входной частоты f-g ., пройдя через блок сдвига 7 на сбрсовый вход регистра памяти 12, переводит его в нулевое состояние. Одновременно этот импульс поступает на управляющий вход блока сдвига 8 (элемент И 27). Если импульс Т , поступает на счетный вхо блока сдвига 8 (элементы И 27 и 31), элемент И 27 через элемент ИЛИ-НЕ 29 запрещает срабатывание элемента И 31, а сигнал с элемента И 27, Задержанный элементом задержки ЗЗ, поступает через элемент ИЛИ 35 на счетный вход суммирующего.счетчика 22. Если же сИгналь,:На блок сдвига 8 поступают неодновременно, элемент И 27 не срабатывает;. элеме.нт И 31 подготовлен к работе сигналом на выходе элемента ИЛИ НЕ 29. Поэтому импульсы на счетный вход сум1«ирующего счетчика 22 поступают через элементу И 31 и ИЛИ 35. БлоЕ сдвига 8 сдвигает импульсы Т , при одновременном поступлении f-- и Т. , в результате чего не теряется информация. Анало1 ично работает блок сдвига 7,который обеспечивает сдвиг импульса,производя щего сброс в регистре памяти 12 относител но импульса перезаписи кода W в вычитающий счетчикЮ.Для нормальной работы устройства необходимо, чтобы при N 0 код из ре гистра памяти 12 не переписывался. Импульсы Т. , поступающие на cчeтш fй вход счетчика 22, преобразуют временной интер валТ-g между двумя импульсами входной частоты ц jcoa N , Этот код с частотой п реписывается через вентиль переноса кода 23 в регистр памяти 12, откуда обратный код N с частотой f,. через вентиль переноса кода 14 записывается в вычитающем счетчике 10. Частота на выходе первого управляемого делителя час тоты 3 b.K-t Формула изобретения 1. Устройство для умножения частоты следования импульсов, содержащее два управляемых делителя частоты, каждый из которых состоит из вычитающего счетчика, установоч Ь1й вход которого через вентиль переноса кодов сеединен с выходом регистра памяти, и двух последовательно соединенных элементов задержки, вход одного из которых соединен с выходом вычитающего счетчика, а выход - с вентилем переноса кода, измерителя периода, состоящего из суммирующего счетчика, сбросовый ход которого связан с последовательно соедннен fibiMH элементами задержки, а выхоД через вентиль переноса кода - со входом регистра памяти первого управляемого делителя частоты, источники входных импульсов и импульсов калиброванной частоты и вептиди, отличающееся тем, что, с целью повышения быстродействия, в него введены блоки сдвига, при этом источВЯК входных импульсов через первый блок сдвига подключен К сбросовому входу регистра памяти первого управляемого делителя частоты, черЪз элементы задержки Измерителя периода - к управляющему входу второго блока сдвига, выход которого ровпинен со входом суммирующего счетчика измерителя периода, а источник импульсов калиброванной частоты черея вентили подключен jso входам третьего и четвертого блоков сдвига, другие входы которых соединены соответственно с выходами элементов задержек управляемых делителей частоты, а выходы - со счетными входами вь1чнтающйх счетчиков делителей. 2- Устройство по 1 6 т л и ч а ю щ е е с я тем, что блок caLMira содержит элемент И, выход которого соединен через элемент Запрет на элемеигах ИЛИ-НЕ и элемент задержки со входами эг емента ИЛИ , при этом выход вычитающего счетчика вгорого управляемого делителя частоты соединен со входами элементов И и Запрет второго блока сдвига, источник импульсов калиброванной частоты соединен со входами элементов ИЛИ третьего и четвертого блоков сдвига, а выходы элементов задержек управляемых делителей частоты со элементов Запрет этих блоков сдвига.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой частотомер | 1975 |

|

SU783701A1 |

| Устройство умножения частоты следования импульсов | 1975 |

|

SU528695A1 |

| Устройство умножения частоты следования импульсов | 1975 |

|

SU525235A1 |

| Устройство для преобразования суммы частотно-импульсных сигналов в код | 1976 |

|

SU657441A1 |

| Устройство для преобразования разности частотно-импульсных сигналов в код | 1976 |

|

SU750728A1 |

| ЦИФРОВОЙ НУЛЬ-ОРГАНВСЕСОЮЗНАЯ, -.^.,-..J-ir--"!,.-!ШЕШ№'5=^/.^-^--- BHEfsHOrn^ | 1972 |

|

SU335685A1 |

| Умножитель частоты следования импульсов | 1979 |

|

SU809526A1 |

| Устройство цифрового задания частоты следования импульсов | 1976 |

|

SU641455A1 |

| Устройство для преобразования частоты в код | 1977 |

|

SU696604A1 |

| Генератор случайных двоичных чисел | 1985 |

|

SU1282118A1 |

Авторы

Даты

1976-06-05—Публикация

1974-04-22—Подача