(54) Ц11ФР080Й ИНТЕГРАТОР ДЛЯ ВОСПРОИЗВЕДЕНИЯ

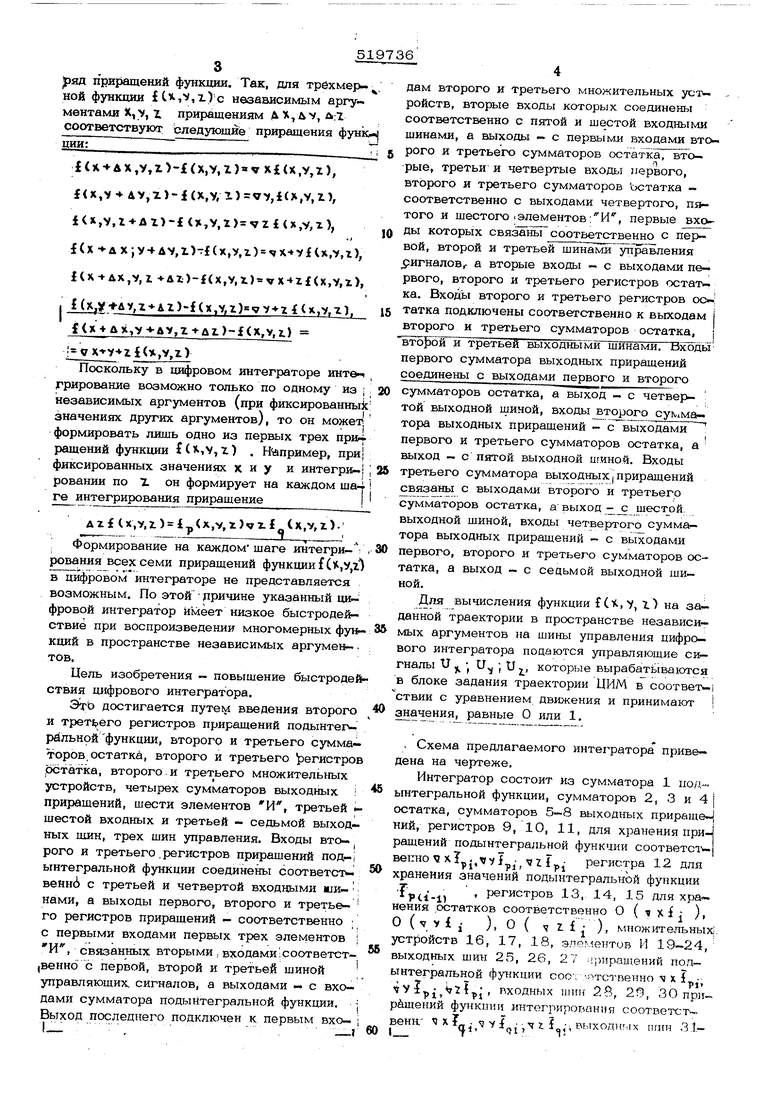

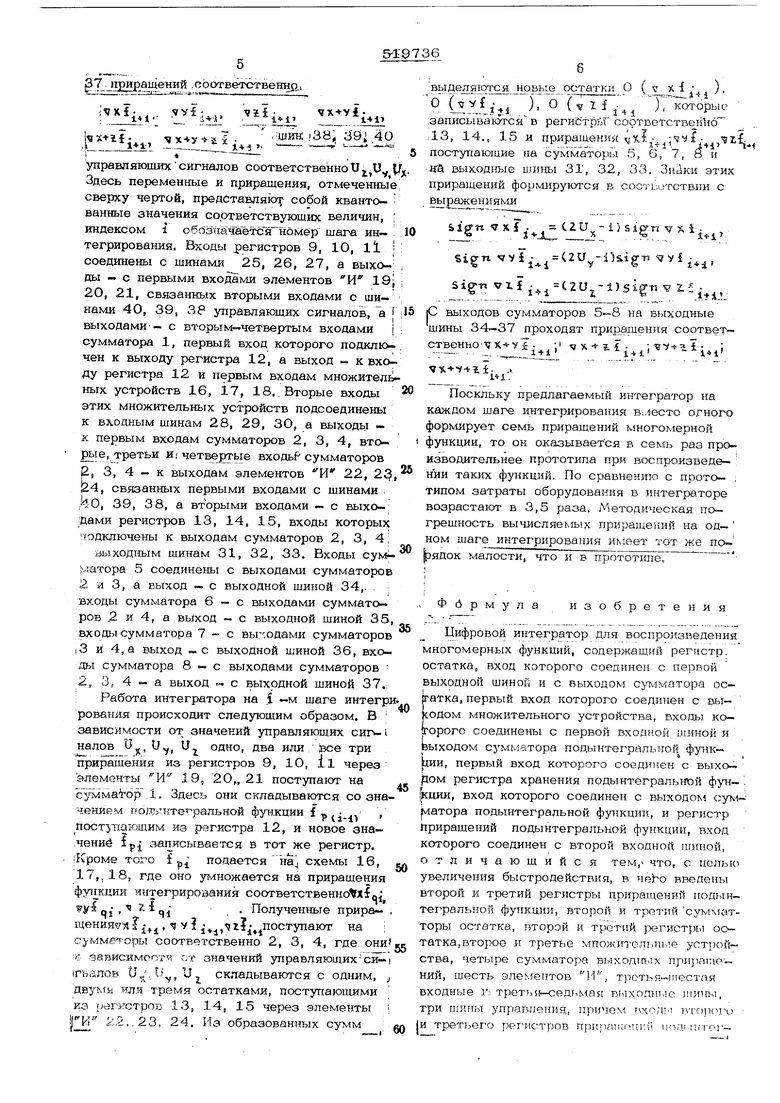

МНОГОМЕРНЫХ ФУНКЦИЙ яд приращений функции. Так, для трбхмерной функции f независимым аргументами X,v, 1 приращениям А ii,uv, Л:1 соответствуют следующие приращения фун1ы Ции; |(,y,z)-f (x,y,z),y,z), ,v Ay,z)-i(x,v,x)vy,f(;i,v,r), f i,y,i + Az)-f ()i,y, (x,v,z), l(x -«-uXiy-tAV,.),y,r) U,y,z), l(x + AX,y, 1 +Ai)-f(x,y,i) (x,y,z), I (X,,)-f(x.Y,t)S7-y-«-Zf X,y,Z). f (,,)-f (X,V,r) jsgX- Y- Zi,y,Z) Поскольку в цифровом интеграторе инте-i Грирование возможно только по одному из независимых аргументов (при фиксированный значениях других аргументов), то он может формировать лишь одно из первых трех при ращений функции (X,V, Z) . Например, при фиксированных значениях х и у и интегр№ ровании по Т. он формирует на каждом ща- ге интегрирования приращение Azf (x,y,z.) ,v,z)v7.f (x,v,z). Формирование на каждом шаге интегри- рования всех семи приращений функции fCit.VjZl в цифровом интеграторе не представляется возможным. По этой дричине указанный цифровой интегратор имеет низкое быстродействие при воспроизведении многомерных фу№ кций Б пространстве независимых аргумен-. тов. Цель изобретения - повышение быстродей ствия цифрового интегратора. ЭуЬ достигается путем введения второго и третьего регистров приращений подынтег- рйльнойфункции, второго и третьего сумма- торов, остатка, второго и третьего регистро остатка, второго.и третьего множительных устройств, четырех сумматоров выходных i приращений, шести элементов И, третьей шестой входных и третьей - седьмой выходных шин, трех шин управления. Входы второго и третьего .регистров прирашений под-i ынтегральной функции соединены соответст веннА с третьей и четвертой входными шинами, а выходы первого, второго и третье- го регистров приращений - соответственно ; с первыми входами первых трех элементов И, связанных вторыми ., входами ;соответст,венн6 с первой, второй и третьей шиной управляющих сигналов, а выходами - с входами сумматора подынтегральной функции, Выход последнего подключен к первым вхо- дам второго и третьего множительных уст ройств, вторые входы которых соединены соответственно с пятой и шестой входными шинами, а выходь - с первыми входами второго и третьего сумматоров остаткаТ то- рые, третьи и четвертые входы иервого, второго и третьего сумматоров схзтатка соответственно с выходами четвертого, пя того и шестого Iэлементов , первые которых связа1ш соответственно с первой, второй и третьей управления ригналовг а вторые входы - с выходами первого, второго и третьего регистров остат ка. Входы второго и третьего регистров ос-; татка подключены соответственна к выходам второго и третьего сумматоров остатка, вто}эой и третьей вь1ходнь1ми шинами, ВходьТ первого сумматора выходных прирашений соединены с выходами первого и второго сумматоров остатка, а выход - с четвер той выходной шиной, входы второго тора выходных прирашений - с выходами первого и третьего сумматоров остатка, а выход - с пятой выходной цгиной. Входы третьего сумматора выходных | прирашений связань с выходами второго и третьего сумматоров остатка, а выход с шестой выходной шиной, входы четвертого сумматора выходных прирашений - с выходами первого, второго и третьего сумматоров остатка, а выход - с седьмой выходной шиной. Для вычисления функции fCi.,y, l) на заданной траектории в пространстве независимых аргументов на шины управления цифрового интегратора подаются управляющие сигналы и и j и jj, которые вырабат э ваются в блоке задания траектории ЦИМ в соответ-i твии с уравнением движения и принимают | значения, равные О или 1. . Схема предлагаемого интегратора приведена на чертеже. Интегратор состоят из сумматора 1 под-. ынтегральной функции, сумматоров 2, 3 и 4 | остатка, сумматоров 5-8 выходных прираше-J НИИ, регистров 9, 10, 11, для хранения при-J ращений подынтегральной функции соответст-| векно ,tiv 1,чгГр регистра 12 для хранения значений подынтегральной функции , регистров 13, 14, 15 для хра Г.-А1 /f нения .остатков соответственно О ( ч Xi ; ), 0(vyfj ), 0( ij 1 i ), множительных; устройств 16, 17, 18, элементов И , выходных шин 25, 26, 27 ::)ирац.ений подынтегральной функции COOT :ггственно х i 4vl,, входных шин- 28, 29, 30 прлрешений функции интегрирования соответст вена ч я у I ч z. f , выходных ишн 31- р7 приращений .ооответственно., mi - . .щив; 138, 39| 4О ,.1. V X управляющих сигналов соответственно Uj,U V Здесь переменные и приращения, отмеченные сверху чертой, представлякх - собой кванто- ванные значения со.ответствующих величин, ; индексом i оббзначаетсяГнбмёр шага ин тегрирования. Входы регистров 9, 1О, ll I соединены с шинами 25, 26, 27, а выходы - с первыми входами элементов И 19 20, 21, связанных вторыми входами с шинами 40, 39, 38 управляющих сигналов, Ъ f выходами-- с вторым-четвертым входами | сумматора 1, первый вход которого подклк чен к выходу регистра 12, а выход к входу регистра 12 и первым входам множительных устройств 16, 17, 18..Вторые входы этих множительных устройств подсоединены к входным шинам 28, 29, ЗО, а выходы - к первым входам сумматоров 2, 3, 4, вторьте, третьи И; четвертые входьР сумматоров 2, 3, 4 - к выходам элементов И 22, 2, 4, связанных первыми входами с шинами ko, 39, 38, а вторыми входами - с выхо-: Дами регистров 13, 14, 15, входы которых :одключены к выходам сумматоров 2, 3, 4; выходным шинам 31, 32, 33. Входы сумИатора 5 соединены с выходами сумматоров 2 и 3, а выход с выходной шиной 34,- . : входы сумматора 6 с выходами сумматоров 2 и 4, а выход с выходной шиной 35, Bxooiji сумматора 7 - с вышдами сумматоров |3 и 4, а выход -с выходной шиной 36, входы сумматора 8 - с выходами сумматоров 2, 3, 4 - а выход - с выходной шиной 37.: : Работа интегратора на i -м шаге интегри рованля происходит следующим образом. В зависимости от, значений управляющих сиг-1 налов и, и.у, и одно, два или все три : ркращения из регистров 9, 1О, 11 через элементы И 19, 20„ 21 поступают на cyMMHirdpM. Здесь они складываются со значением пошз;нте: ральной функции fp/.jy , пост тштящим из регистра 12, и новое значение fpi записывается в тот же регистр. |Кроме того f д подается на4 схемы 16, 17,, 18, где оно умножается на приращения .11ии интегрирования соответственно Х „ Полученные прира, Ч ,поступают на щения Я сумматоры соответственно 2, 3, 4, где они - зависимоот:« ст значений управляющих си-i ipKanoB tJr;;, , J 7 складываются с одним, j ДБуьлн иля тремя остатками, поступающими КЗ регистров 13, 14, 15 через элементы 11Ё -2-23, 24. Из образованных сумм LV...)выдел:я1отся нрвь1е сжтаткн О ) J, которые :записыва1 эт-ся в регийтрьГ соогветствен11б ,13, 14., 15 и приращения ,,Z,, поступающие на сумматоры 5, 6, 7, 8 и да выход 1ые шины 31, 32, 33, этих приращений формируются в COOTI,S:::TCTBJTH с выражениями blgtt X f j.j 1) Sign V s i ., SigTi 7Vi.-. ,(2U,,-i)s. vi -s . . . j,.j t2U,-i)sig:-n Zi jC выходов сумматоров 5-8 на выходные шины 34-37 проходят прирашення соответЧ.1 - ственно т ;| л Поскльку предлагаемый интегратор на каждом шаге интегрирования В;лесто огного формирует семь приращений многомерной функции, то он оказывается в семь раз производительнее прототипа при воспроизведе- : НИИ таких функций. По сравнению с прото- ; типом затраты оборудования в интеграторе возрастают в 3,5 раза. Методическая погрешность вычисляемых приращений на од ном шаге интегрирования имеет тот же поЬядок малости, что и в прототипе. Фбрмула изобретени.я Цифровой интегратор для воспроизведения многомерных функций, содержащий регистр, остатка, вход которого соединен с первой выходной щиной и с выходом сул-1матора остатка, первый вход которого соединен с выКодом множительного устройства, входы ко- горого соединены с первой входной щиной и Ьыходом cjMiMaTOpa пода1нтегральной функЬии, первый вход которого соединен с выхо- ром регистра хранения подынтегральной фун . кции, вход которого соединен с выходом сум рлатора подынтегральной функции, и регистр Приращений подынтегральной функции, вход которого соединен с второй входной тиной, отличающийся тем, что, с целью увеличения быстродействия,, в чеЬо введень второй к третий регистры приращений подынтегральной функции, второй и третийсумл1атторы остатка, второй и третий }х-;гистры остатка, второе .и третье ..пг.111г1е устройства, четьтре сумматора выходтпл х npi paiae НИИ, шесть элементов И, третья-шестая входные 5j Третьsf-седьмая BFiixo.iHr-.re IHMIM, три ип-пты управления, причем ivrf)i(MX 1и третьего регистров npjqiaiKf n-ii. и рально функции соединены соответственно с третьей к четвертой входными шинами, а выходы первого, второго и третьегчэ I регист, ров приращений соединень соотв етственно cj цepвымиJaxoдaми первых трех элементов ИГ соединенных вторыми эходами соответственно с первой, второй и шиной управК лякших сигналов, а выходами с входами су 1матора подынтегральной функции, выход (Которого соединен с первыми входами |втр- I рого и третьего множительных устройств, BTopbie входы которых соединены cooTBeTeiwj венно с пятой и шестой i входными . шинами, i i а выходы - с первыми входами второго и третьего сумматоров остатка, вторые, тре- тьи и четвертые входы первого, второго и : третьего сумматоров , остатка соединены со ответственно с выходами четвертого, пятого; и шестого элемнтов И, первые входы ко- j торых соединены соответственно с первой, второй и третьей шинами управления , а вторые входы - с ыходашПтерврго, i второго и третьего регистров остатка, входы второго и третьего регистров, остатка .соединены соответственно .с выхо71ами BTOfK i.i25 го и третьего сумматоров остатка, второй 15 20 и третьей I выходными шинами, входы перво-. госумматора выходных прирашендй / Ьоедйнены с выходами первого и второго сумма торов остатка а выход - с четвертой выходной шиной, входы второго сумма ра вы- , ходных прирашений соединены с / ыходами первого и третьего сумматоров остатка/ а ; выход - с пятой выходной шиной, входы тре-; тьего сумматора-выходных прирашений соединены с выходами второго и третьего сум- , маторов остатка, а выход - с шестой выход;ной шиной, -входы четвертого сумматора вы-, (ХОДНЫХ приращений соединены с выходами {первого, второго и третьего сумматоров осг1татка, а выход - с седьмой выходной шиной. ; Источники инфор1иации, принятые во вн№мание(при экспертизе:i - 1. Каляев А. В, Введение в теорию i ровых интеграторов, Киев, Наукова думка,; .1964 г. 2. Пьявченко Н. О., Макаревич О. Б. Материалы объединенной юбилейной научнотехнической конференции. Министерство оборонь1,Т96й г.

J И U

fe Ш 27

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегратор для однородных цифровых интегрирующих структур (оцис) с плавающей запятой | 1973 |

|

SU510727A1 |

| Устройство для моделирования нейрона | 1987 |

|

SU1479944A1 |

| Цифровой интегратор | 1977 |

|

SU732920A1 |

| Цифровой интегратор | 1979 |

|

SU903875A1 |

| Интегро-арифметическое устройство | 1977 |

|

SU746602A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Цифровой интегратор | 1975 |

|

SU650084A1 |

| Цифровой интегратор для решения краевых задач | 1984 |

|

SU1211712A1 |

| Цифровой интегратор | 1985 |

|

SU1365081A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

Авторы

Даты

1976-06-30—Публикация

1974-08-14—Подача