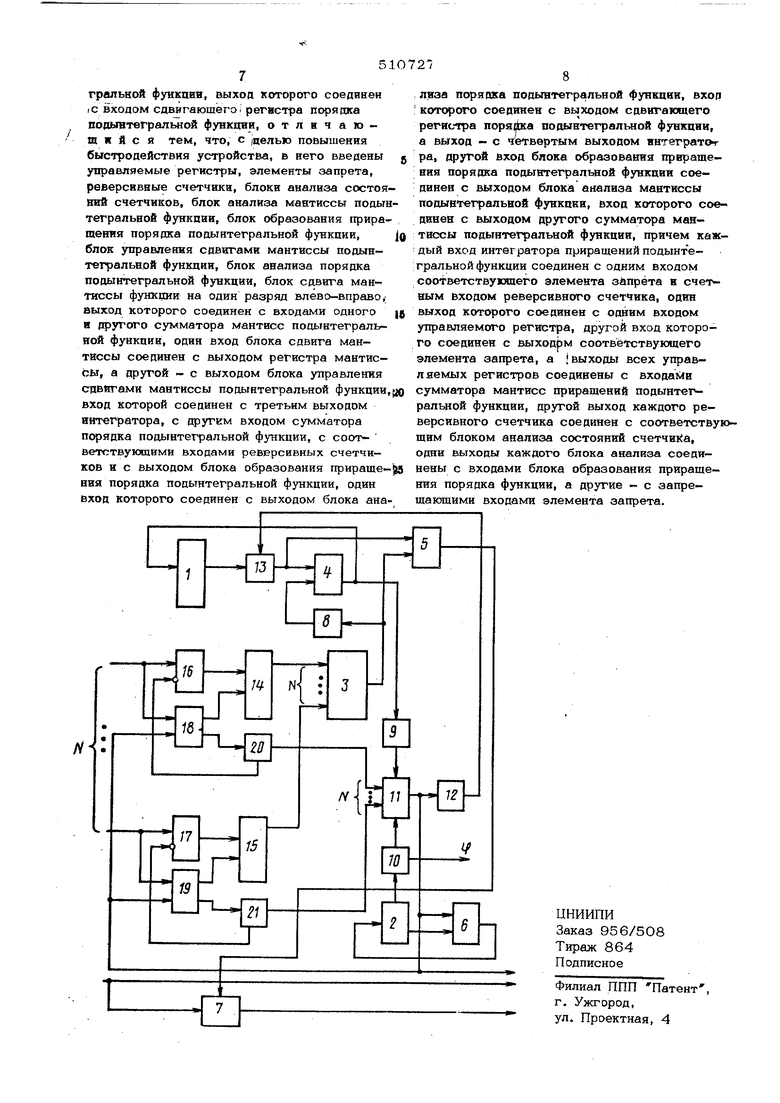

С целью повышения быстродействия цифрового интегратора; с плавающей заиятоЙ в предлагаемое устройство введеяы управляемые . регистры, элемеиты запрета, реверсив ные счетчики, блоки анализа состояний сче чиков, блок анализа мантиссы подынтеграл ной функции, блок образования приращения порядка подынтегральной функции, блок упрйбПения Сдвигами мантиссы подынтегральной функции, блок анализа порядка подын- тегральной функции, блок сдвига мантиссы функции на один разряд влево-вправо, выход которого соединен с входами одного и другого сумматора мантисс подьгнтегральной функции, один вход блока сдвига мантиссы соединен с выходом регистра мантиссы, а другой - с выходом блока управлешга сдвигами мантиссы подынтенгральной функции, вход которого соединен с третьим выходом интегратора, с другим входом сумматора порядка подынтегральной Фзгнкции, с соответствующими входами реверсивных счетчикор и с выходом блока образования приращения порядк а подынтегралт йой функции, один вход которого сое дивен с выходом, блока анализа порядка подынтегральной функцг , вход которого соединен с выходом сдвигающего регистра порядка подынтегральной функции, а выход - с четвертым выходом интегратора, другой вход блока образования приращения порядка поды тегральной функции соединен с выходом бло ка анализа мантиссы подьгнтегральной функции, вход которого соединен с выходом дру гого сумматора мантиссы подынтегральной функции, причем каждый вход приращений подынтегральной функции интегратора соединен с одним входом соответствующего элемента запрета и счетным входом реверсивного счетчика, один; выход которого соединен с одним входом управляемого регистра, другой вход JcoToporo соединен с выходом соответствующего элемента запрета, а выходы всех управляемых регистров соединены с входами сумматора мантисс при- ращений подынтегральной функции, другой выход каждого реверсивного счетчика соединен с соответствующим блоком анализа состояний счетчика, одни,выходы каждого блока анализа соединены с входами блока образования приращения порядка функции, а другие - с запрещактаими входами элемента запрета. На чертеже показана блок-схема предлагаемого устройства. Интегратор содержит регистр 1 мантиссы подынтегральной функции длиной п раз рядов, регистр 2 порядка функции длиной Q: разрядов, сумматор 3 мантисс приращений, сумматоры 4 н 5 мантисс подынтегральной функции, сумматор о порядка функции, множительной блок 7, биок 8 задержки, блой 9 анализа маитиЬсы подынтегральной функции, блок 10 анализа порядка фугощни, блок 11 образования приращения порядка функции, блок 12 управления сдви1-ами мантиссы функции, блок 13 сдвига мантиссы функсиа на один разряд влево-вправо, управляемые регистры 14 и 15, элементы запрета 16 и 17, реверсивные счетчики 18 и 19, блоки 20 и 21 анализа состояний счетчиков. Вычисления в цифровом интеграторе прог изводятся по формулам Ypfi lcp-Ypi + jI vYpoii+j), Yp(4l) Ypi- VYpvfЬi), .l)Yp(i44j)pVYc f +i}, где Yp() - среднее значение функции на данном шаге интегрирования; 7Yp) (4i) - квантованное нрирашевие подынтегральной функции, VYoCni) - квантованное прираще- ние переменной интегрирования, V2,{f-t-d)- приращение интеграла на данном щаге интегрирования, W- число входов приращений подынтегральной функции. В данном цифровом интеграторе подЬгнтегральная функция Ypi -представлена в виде мантиссы в дополнительном модцФициро- ; ванном коде и порядка, приращения7Ур1|)(о/), Ya ( + i)- в вице мантисс и одноразрядных приращений, порядка. Работает интегратор следующим образом. На входы интегратора на ( i )-ом шаге интегрирования поступают приращения подынтегральной функции в виде одноразрядных приращений порядковУПо (J + i) и УПр) { +d ) и квантованных мантисс VMc(i) и VMpv)(-i-H),()4,2,...,N). Приращения порядков УП р ) (1 + 1 ) приращений подынтегральной функции поступают на счетчики 18 и 19, где образуются новые значения разностей порядков 1,) (н)/ в результате чего перестраиваются управляемые регистры 14 и 15, на выходе блоков анализа состояний счетчиков 18 и 19 появляются потенциалы соответствующие новым состояниям счетчиков, которые подготавливают элементы запрета 16 и 17. При прохождении мантисс приращений VMpV () + 0 через управляемые регистры 14 и 15 мантиссы задерживаются в них на величину (п - L i ( i + i )) определяемую, состоянием счетчиков 18 и 19, а мантисса подынтегральной функции Мр (J ) в эт время задерживается на ц разрядов в регистре 1. В результате мантиссы прирашений сдвигаются вправо относительно мантиссы функции на величину разностей порядковLi ( ЙО npi - hp:V ( |vl ). Величина U (i),. с помощью блока , образования приращений порядка функции всегда поддерживается положительной. Если величина ;L т (f+i) больше длины управляемого регистра, то с помощью элементов запрета 16 и 17 прохождение мантисс VMp О (Ы) на регистры 14 и 15 запрещается посредством подачи на запрещающие входы элементов запрета 16 и 17 сигналов с выходов блоков 20 и 21, соответствующих значениям разностей порядкА Lf ( i + 1 ), большим длины управляемого регистра. На выходе управляемых регистров 14 и 15 приращения подынтегральной функции 1 имеют лорядок функции Hpi. Следователг но, все слагаемые поступают на входы сум маторов 3i и 5 и через блок 8 на входы сумматора 4 в одном порядке. Блоки 2О и 21 вьфабатывают также сигналы о состояниях счетчиков 18 и 19, при одном из которых в блоке 11 образования приращения порядка УПр ( i + i ) формируется vnp (l-bl ) +i ,а при другом в том же блоке 11 - отрицательное приращение УПр ( -( + 1 ) -1. Блок 9 анализа мантиссы подынтегральной функции вырабатывает сигналы Mp(i + i)i V Mp(Ui)-i ( + )-2. Первый поступает на вход блока 11 образования приращения порядка функции в качестве одного из управляющих сигналов при формировании Vrtp ( 4 J) 1 , второй - при формировании УПр .(+i) -1. Блок 10 анализа порядка подынтеграль ной функции вырабатывает сигналы . Первый поступает на вход блока 11 образования приращения порядка функции в качестве одного из управляющих сигналов пр формировании УПр ()- , второй на выход интегратора как сигнал переполне ния tp . Блок 11 образор-:лия приращения поряд ка функции по результатам анализа посту пающих сигналов вырабатывает сигнал УП rt1p () равный +1, - 1 нли О, Эти игналы поступают на вход бяока 12 утфав- ення сдвигами мантиссы функции, н« сумматор 6, на выход интегратора в качестве выходаого приращения порядка функцегн vnp () ива реверсивные счетчюси 18и 19. БЛОК 12 управления сдвнгамн вырабаты вает сигналы сдвига мантиссы подынтегральной фунции вправо при УПр (- +0 влево прнУП р ( ) - - 1 . Эти сигваиы поступают на блок 13 сдвига на один разряд влево-вправо мантиссы функции, кроме того, по ним происходит сдвиг (нормализация). В данном шаге происходит сдвиг мантиссы по сигналам, выработанным в пр дыдущем шаге ин: егрнрования. Приращение порядка V П р ( М 1 ) поступает на сумматор 6, где складывается с порядком функции, находящимся в регистре 2. На выходе сумматора 6 формируется новое значение порядка П р ( i + 1 ) функции, которое записывается в регистр 2. Сигнал V П р { + О с выхода блока 11 поступает на реверсивные счетчики 18 и 19и на один зыход интегратора. Приращение порядка V П о ( -i - i) переменной интегрирования поступает непосредственно на другой выход интегратора. На третий выход интегратора с выхода множительного блока выдается мантисса :приращения интеграла. Формула изобретения Цифровой интегратор для однородных цвфровых интегрирующих структур с плавающей запятой, содержащий сдвигающий регистр мантиссы подынтегральной функции, сдвигающий регистр порядка подынтегральной функции, сумматор порядка подынтегральной функции, сумматор мантисс приращений подынтегральной функции, множительный блок, блок задержки, сумматоры мантисс подынтегральной функции, выход одного сум- матора мантиссы подынтегральной функцин соединен с одним входом множительного блока, другой вход которого соединен с одним, входом и с первым выходом интегратора, а выход - с вторым выходом интегратора, причем выход сумматора мантисс приращений подынтегральной функции соединен с одним входом одного сумматора подьтнтегральной функции и с входом блока задержки, выход которого соединен с одним входом другого сумматора подынтегральной функцин, выход которого соединен с входом сдвкгаюшего регистра мантиссы подынтегральной функпии, а выход сдвигающего регистра порядка подынтегральной функции соединен с одним входом сумматора порядка подынто-

тральной функции, выход которого соединен Iс входом сдвигающего; регистра порядка подынтегральной функции, отличаю - ш к и с я тем, что, с щелью повышения быстродействия устройства, в него введены управляемые регистры, элементы запрета, реверсивные счетчики, блоки анализа состояний счетчиков, блок анализа мантиссы подынтегральной функции, блок образования приращения порядка подынтегральной ф нкции, блок управления сдвигами мантиссы подынтегральной функции, блок анализа порядка подынтегральной функции, блок сдвига мантиссы функции на один разряд влево-вправо, выход которого соединен с входами одного и другого сумматора мантисс пооьгнтегральной функции, один вход блока сдвига мантиссы соединен с выходом регистра мантиссы, а другой - с выходом блока управления сдвигами мантиссы подынтегральной функции вход которой соединен с третьим выходом интегратора, с другим входом сумматора порядка подынтегральной функции, с соответствующими входами реверсивных счетчиков и с выходом блока образования приращения порядка подынтегральной функции, один вход которого соединен с выходом блока анализа порявка подынтегральной функции, вход которого соединен с выходом сдвигакяцего регистра nopHtbca подынтегральной функции, а выход - с четвертым выходом интаграточра, другой вход блока образования прирашения порядка подынтегральной функции соединен с выходом блока анализа мантиссы подынтегральной функции, вход которого соединен с выходом другого сумматора мантиссы подынтегральной функции, причем каждый вход интегратора приращений подынтегральной функции соединен с одним входом соответствующего элемента зйпрёта и счет ным входом реверсивного счетчика, один выход которого соединен с одним входом управляемого регистра, другой вход которого соединен с выходрм соответствующего элемента запрета, а j выходы всех управляемых регистров соединены с входами сумматора мантисс прирашений подынтегральной функции, другой выход каждого реверсивного счетчика соединен с соответствующим блоком анализа состояний счетчи1 а, одни выходы каждого блока анализа соединены с входами блока образования приращения порядка функции, а другие - с запрещающими входами элемента запрета.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегратор с плавающей запятой | 1975 |

|

SU590774A2 |

| Цифровой интегратор | 1976 |

|

SU651371A1 |

| Цифровой интегратор | 1975 |

|

SU661572A1 |

| Цифровой интегратор | 1975 |

|

SU650084A1 |

| Устройство для автоматического преобразования мантиссы и порядка | 1976 |

|

SU734677A1 |

| Вычислительное устройство цифровой интегрирующей структуры | 1977 |

|

SU703840A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ЦИФРОВОЙ МОДЕЛИ | 1967 |

|

SU223472A1 |

| Параллельный цифровой интегратор с пла-ВАющЕй зАпяТОй | 1977 |

|

SU828199A1 |

| Интегроарифметическое устройство | 1987 |

|

SU1515162A2 |

| РЕШАЮЩИЙ БЛОК ДЛЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО | 1972 |

|

SU355631A1 |

Авторы

Даты

1976-04-15—Публикация

1973-07-17—Подача