(54) УСТРОЙСТВО ДЛЯ ПОИСКА ОПЕРАНДОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поиска операндов | 1974 |

|

SU506856A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство для интерпретации выражений языков программирования | 1982 |

|

SU1078432A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Многопроцессорная вычислительная система | 1979 |

|

SU751238A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| МАКРОПРОЦЕССОР | 2001 |

|

RU2210808C2 |

| Устройство микропрограммного управления | 1987 |

|

SU1539776A1 |

Изобретение относится к вычислительной технике и может быть использовано при проектировании электронных цифровых вычислительных машин.

Известны устройства 1 для поиска операндов, содержащие регистр адреса, элементы И, счетчик адреса, коммутатор и схе.му сравнения.

Известные устройства имеют низкое быстродействие и требуют наличия в системе команд ЦВМ специальных ко.манд обмена между сверхоперати1вной памятью (СОП) и оперативным запоминающим устройством (ОЗУ) и между СОП и исполнительными бло-ками машин, затрудняют программирование на машинном языке и построение ЦВМ по модульному принципу.

Устройство 2 является паиболее близким по сущности техническим решением и содержит регистр адреса, узел фиксации трасс обмена, узлы подготовки адреса, каждый из которых содержит триггер запуска, первый элемент И, второй элемент И, вход регистра адреса соединен с первым входом устройства, первая группа входов узла фиксация трасс обмена соединена с первой группой входов устройства, а группа выходов соединена с группой выходов устройства, единичный вход триггера запуска каждого узла подготовки адреса соединен с соответствующим входом второй группы входов устройства, первый вход первого элемента И соединен со вторым входом устройства, первый вход второго элемента И соединен с третьим входом устройства.

Целью изобретения является повыщение быстродействия устройства и расширение его функциональных возможностей. Поставленная цель достигается тем, что

каждый узел подготовки адреса устройства содержит счетчик, схему сравнения, третий элемент И, лервый вход счетчика соединен с выходом первого элемента И, первый вход схемы сравнения соединен с выходом счетчика, второй вход соединен с выходом регистра адреса, а выход соединен со вторыми входами второго и первого элементов И, выход второго элемента И соединен с соответствующими входами второй группы входов узла фиксации трасс

обмена, первый вход третьего элемента И соединен с единичным выходом триггера запуска, второй вход соединен с четвертым входом устройства, а выход - со вторым входом счетч;:ка, выход первого элемента И соединен с нулевым входом триггера запуска.

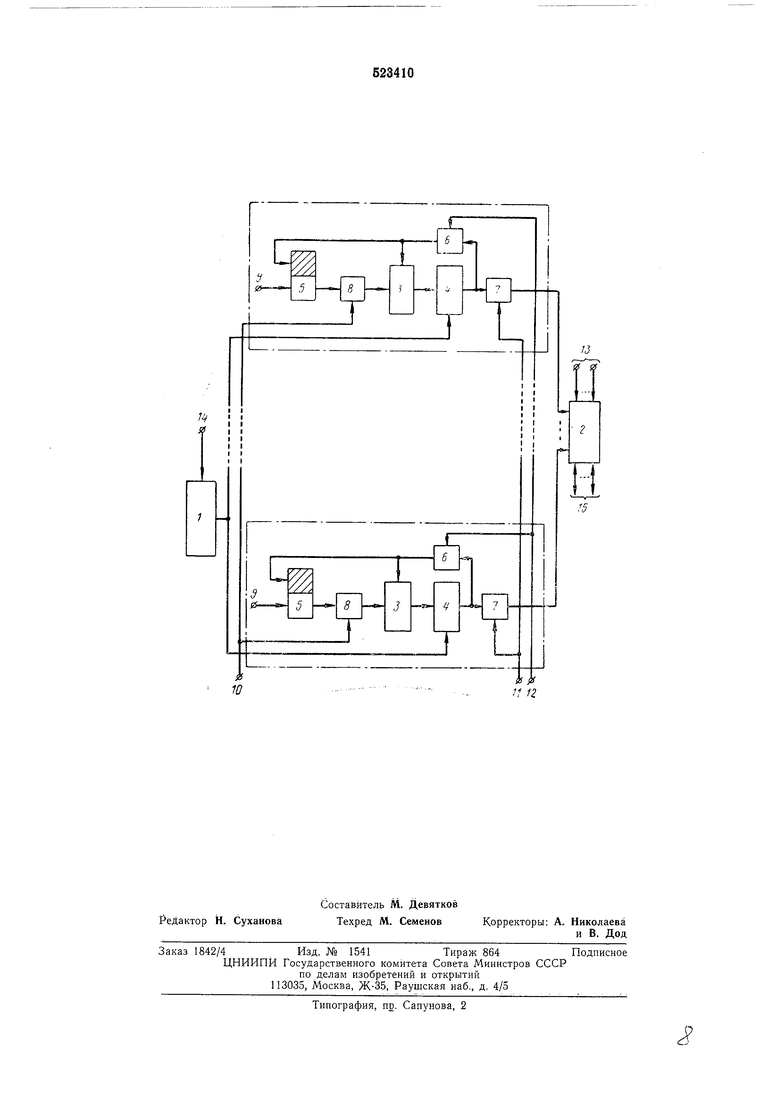

На чертеже представлена схема устройства.

Устройство содержит регистр 1 адреса, узел

2 фиксации трасс обмена, узлы подготовки адреса, кал-сдый из которых содержит счетчик 3,

схему 4 сравнения, триггер 5 запуска, элементы И 6-8.

Устройство также имеет следующие входы и выходы: группа входов 9 устройства (входы запуска узлов подготовки адреса), счетный вход 10, входы 11 и 12 синхронизирующих сигналов, другая группа входов 13 (группа входов узла фиксации трасс обмена), четвертый вход 14 устройства (вход регистра адреса) и группа выходов 15 устройства (группа выходов узла фиксации трасс обмена).

Устройство работает следующим образом.

При приеме кода очередной команды из памяти команд в центральное устройство управления код относительного адреса команд поступает на вход 14 и заносится в регистр 1 адреса. Центральное устройство управления выбирает свободный п-ый узел подготовки адреса, закрепляет его за текущей командой и устанавливает адрес между п-ым узлом подготовки адреса и иаполнительным блоком - источником операнда.

По сигналу из центрального устройства управления на 1входе 9 п-го узла подготовки адреса триггер 5 запуска фиксирует момент запуска этого узла и разрешает прохождение счетных импулысов со входа 10 устройства через элемент И 8 на счетчик 3. Счетные импульсы поступают на элемент И 8 с -частотой выборки команд из памяти команд в центральное устройство управления и в интервалах времени от момента формирования адреса очередной команды до начала выполнения этой команды. Наращивание числа в счетчике 3 может происходить теми же сигналами, что и наращивание числа в счетчике команд машины.

Схема 4 сравнения сравнивает содержимое счетчИка 3 с кодом из регистра 1 адреса. Сигнал на выходе схемы 4 сравнения является признаком обнаружения операнда п.-ым узлом подготовки адреса.

Схема 4 сравнения не вырабатывает сигналов сравнения нулевых кодов, т. е. наличие всех нулей в поле с относительного адреса t-ой команды является признаком того, что t-ая команда При своем выполнении не использует операнда, задаваемого кодом в поле кода относительного адреса команд. При наличии сигнала сравнения со схемы 4 сравнения, управляющего (синхронизирующего) сигнала на входе И устройства и сигнала запроса исполнительного блока машины на одном из входов 13 узла 2 фиксации траос обдМена устанавливает трассу обмена и формирует на соответствующем выходе 15 сигнал выбора трассы обмена.

Сброс счетчика 3 и триггера 5 запуска осуществляется каждый раз -после завершения поиска операнда сигналом с элемента И 6. Управляющие сигналы на входах 11 и 12 устройства устанавливают необходимую временную последовательность срабатывания элементов узлов подготовки адреса.

Разрядность счетчика 3 определяется длиной кода относительного адреса команды.

Длина этого кода задает интервал из команд, в -котором появившийся результат должен быть Использован в качестве операнда, т. е. если длина кода относительного адреса команды равна 4, то результат текущей команды может быть использован не более, чем через 15 последующих команд. В противном случае, а также при многократном использовании результата одной команды, этот результат должен отсылаться в память мащины.

Таким образом, изобретение позволяет исключить сверхоперативную память и команды обмена с этой памятью и тем самым снизить время рещения задач, а также позволяет повысить уровень мащинного язьика программирования, поскольку адресуется не аппаратура (регистры, ячейки памяти), а команды программы -безотносительно к месту их нахождения в памяти.

Формула изобретения

Устройство для поиска операндов, содержащее регистр адреса, узел -фиксации трасс обмена, узлы подготовки адреса, каждый из которых содержит триггер запуска, первый элемент И, второй элемент И, вход регистра адреса соединен с первым входом устройства, первая группа входо-в узла фиксации трасс обмена соединена с первой группой входов устройства, а группа выходов соединена с группой выходов устройства, единичный вход триггера запуска каждого узла подготовки адреса соединен с соответствующим входом второй группы входов устройства, первый вход первого элемента И соединен со вторым входом устройства, первый вход второго элемента И соединен с третьим входом устройства, отличающееся тем, что, с целью повышения быстродействия, каждый узел подготовки адреса содержит счетчик, схему сравнения, третий элемент И, первый вход счетчика соединен с выходом первого элемента И, пер-вый вход схемы сравнения соединен с выходом счетчика, второй вход соединен с выходом регистра адреса, а выход соединен со вторыми входами второго и первого элемента И, выход второго элемента И соединен с соответствующ-ими входами второй груипы входов узла фиксации тра-сс обмена, первый вход третьего элемента И соединен с единичным выходом триггера запуска, второй вход соединен с четвертым входом устройства, а выход со вторым входом счетчика, выход первого элемента И соединен с нулевым входом триггера запуска.

Источники информации, принятые во внимание прИ экспертизе.

Г

Авторы

Даты

1976-07-30—Публикация

1972-03-16—Подача