1

Изобретеине относится к ъычкспктепъ-ной TexHHJce и, в частности к системам ав ToxiaTHHSCKoro синтеза тестов контроля работоспособности и диагностики неисправностей сложных цифровых объектов, узлов, бло- ков и устройств средств вычислительной техники и автоыатию, построенных на иите- гральяьк схе:лах.

Известны системы, содержанзде ЦВМ., соединенную двусторонними связями с блоком сопря}кения, регистр входного вектора, выход которого соединен со входо;-. образна объекта, а вход через коммутатор подключе к блоку сопряжения, устройства коммутации соединенные с соответствующими входами и выхода:-.и1 образца объекта.

Для современных цифровых объектов разработка тестов, обладающих гарантировап- ной полнотой (т.е. способностью обнаруживать заданный класс неисправностей объектов) или заданной точностью диагностики является чрезвычайно сложной задачей.

Известные системы автоматизации решения этой задачи можно разделить на две категории.

К первой категории относятся системы, целиком базирующиеся на универсальньк ЦВМ общего назначения и не содержащие каких-либо специальных аппаратных средств. В таких системах задачи, связанные с создание,; тестов, решаются на стандартно;.: оборудовании ЦВМ с помо.щь.о соответствуюшего комплекса программ. Наиболее эффект.гшные методы синтеза тестов о использоБанием подобных систем основываются ufi програ:-/ л1но.1 моделировании задахп-юхо объекта GO и всех его модификаций O)02,,0 соответствующих неисправностям 1,2,...,К псевдослучайных входных послецова: ЗХ1Ы1ОСТЯХ, рассматриваемьтх как потенциальные тесты. Эти послсдовате.льносги генерируютс.я сгтециа.льной программой, н ка;кдая из тшхХ- прикла.дывается ко входа;-,; ыоц.&

лей объективов о к

В результате .уюделгрования этих объектов на послеаовате.иьности , вычисляются их выходные реахсции Уд Л к на эту последовательность.

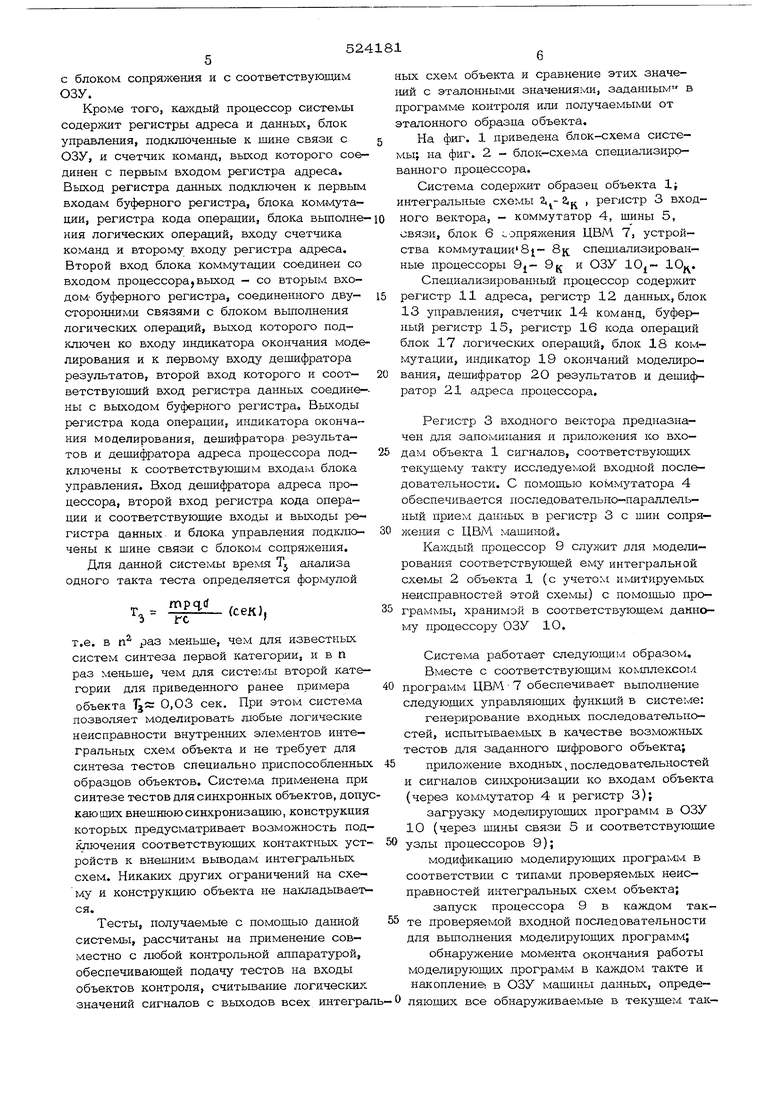

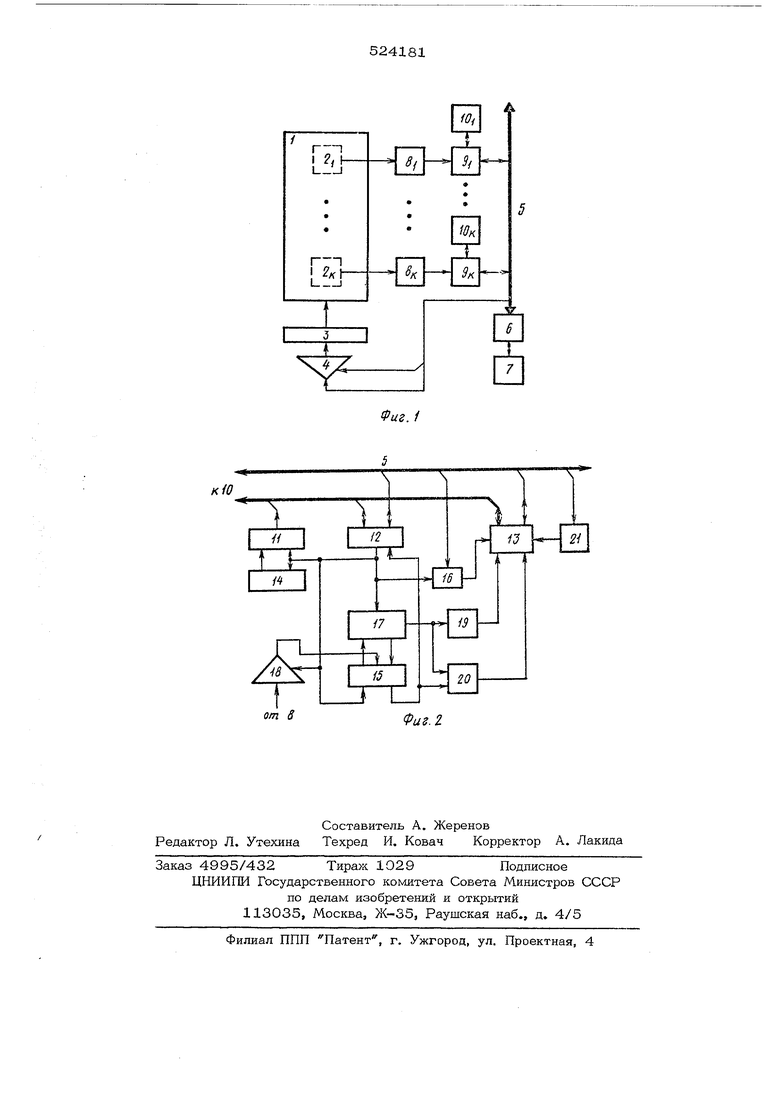

Реакции у |, Y,.-.,V, сравниваются с реакцией v с целью составления списка та мексправюсти (...анные выбираются из ОЗУ 10); ои.щее управление- процессом синтеза тес та, составпелие списков неисправностей, об наруживаемых из исследуемых входных последовательностей, вывод тестов и других данных. Перед началом работы ко1 шлексу пропра:лм ЦВМ 7 задается исходная ннформация, определяющая объект, для которого производится построение тестов. Эта инфор мация включает; перечень типов интегральных схем объекта с указанием, какая из этих схем подключена к каждому процессору 9; перечень всех входов объекта, входов синхронизации,, входов установ1Ш в исходно (в си:утоличес1ШХ или физических состояние (в си;утоличес1ШХ или физических адресах выходов регистра 3; входную последовательность приведения объекта в исходное состояние и последовательность сигналов цикла синхронизации. Кроме того, машина должна содержать заранее введенные библиотечнъю данные, в том числе модели (моделирующие програм мы) всех типов интегральных; схем, спис1сн их наиболее вероятных неисправностей, данные, характеризующие контрольную аппаратуру и, в частности, возможные законы фор мирования псевдослучайньгх входных последовательностей и т.д. Работа системы начинается с загрузки моделирующих программ в ОЗУ 1О процессоров 9, соответствующих тем типам интегральных схем, которые подключены с помощью устройств 8 к этим процессорам. Эти нрограммы извлекаются организующей программой из внещне .;.мяти ЦВМ 7 и передаются через шины связи 5 и регистры 12 процессоров в ОЗУ Ю. После загрузки программ в ОЗУ засылаются данные, модифицирующие эти программы в соответствии с типами неисправностей интегральных схем на которых будет исследоваться входная последовательность, рассматриваемая как возможный гест объекта. В моделирующую программу каждого процессора вводятся одновременно Г неисправностей (где Г- разрядность слова ОЗУ 10). Таким образом, программа каждого процессора обеспечиьает параллельное моделирование Г модификаций интегральной схемы, соответствующих Г ее различным неисправностям. Организующая программа систек ш обеспечивает приложение ко входам объекта 1 последовательности приведения объекта в исходное состояние. В каждом такте i: этой последовательности система работает следующим образом. Входной сектор, соответствующий такту t , передается ЦВМ 7 через блок сопряжения 6 и коммутатор 4 в регистр 3, что обеспечивает приложение этого ра ко входам объекта 1 По окончаннм переходных процессов в объекте ЦВМ 7 с помощью сигналов, передаваемых по шинам связи Sj запускает выполнение моделирующих программ в процессорах 9. Калодый процессор 9 работает автономно, независимо от других, под управлением программы, находящейся в его ОЗУ 10. В начале выполне1гия программы каждого процессора значения сигналов, установившиеся на входах интегральной схемы объекта 1, с которой связан данный процессор, считываются с помощью блока 18 в регистр 15 к да- через регистр 12 записываются в ОЗУ Ю- Эти значения сигналов рассматриваются как значения входов моделей интегральной схемы. На основании этих значений входов и состоя1шя в такте t -1 моделирующая программа вычисляет состояние всех элементов каждой модели. Выч11сление строится как итеративный процесс. Он считается законченным, если состояние элементов каждой модели оказывается неизменным в двух еле- дующих одна за другой и терапиях. Конец вычисления фиксируется индикатором 19 процессора, по сигналу которого блок 13 унравления сигнализирует ЦВМ 7 об окончании выполнения его програмксы. По окончании въшолнения моделирующих программ всеми процессорами 9 сис-темы организующая программа ЦВМ 7 подготавливает вектор входной последовательности, соответствующий такту1+1 и описанный процесс повторяется. По окончагши приложения последовательности приведения объекта в исходное состояние образец объекта 1 оказывается в известном начальном состоянии. В соответствующее начальное состояние приводятся также модели интегральных схем, реализуемые программами процессоров 9 (если в эти модели не внесены неисправности, то они находятся в том же состоянии, что и соответствующие интегральные схемы объекта). Затем ЦВМ 7 начинает процесс генерирования и исследования входных последовательностей, рассматриваемых в качестве возможных тестов. При этом работа системы в каждом такте 1 любой такой последовательности скдадывается из описанных действий, выполняемых в такте t последовательности приведения объекта в исходное состояние, и ряда дополнительных. Дополнительными действиями процессоров 9 являются сравнение полученных в результате вычисления значений выходов моделей интегральных схем, преобразованных в соответствии с типами проверяемък неисправностей, с фактическими значениями въьходных с блоком сопряжения и с соответствующим ОЗУ. Кроме того, процессор системы содержит регистры адреса и данных, блок управления, подключенные к шине связи с ОЗУ, и счетчик команд, выход которого сое динен с первым входом регистра адреса. Выход регистра данных под1шючен к первым входам буферного регистра, блока коммутации, регистра кода операции, блока выполне ния логических операций, входу счетчика команд и второму входу регистра адреса. Второй вход блока коммутации соединен со входом процессора,выход - со вторым входом- буферного регистра, соединенного двусторонними связями с блоком выполнения логических операций, выход которого подключен ко входу индикатора окончания моде лирования и к первому входу дешифратора результатов, второй вход которого и соот- ветствуюший вход регистра данных соединены с выходом буферного ре1 истра. Выходы регистра кода операции, индикатора окончания моделирования, дешифратора результатов и дешифратора адреса процессора подключены к соответствующим входам блока управления. Вход дешифратора адреса процессора, второй вход регистра кода операции и соответствующие входы и выходы регистра данных и блока управления подключены к шине связи с блоком сопряжения. Для данной системы время Tj анализа одного такта теста определяется формулой г - РЧ- Ч- Тс Т.е. в п раз меньше, чем для известных систем синтеза первой категории, и в п раз меньше, чем для системы второй категории для приведенного ранее примера объекта 0,03 сек. При этом а ютема позволяет моделировать любые логические неисправности внутренних элементов интегральных схем объекта и не требует для синтеза тестов специально приспособленны образцов объектов. Система применена при синтезе тестов для синхронных объектов, допу кающих внешнюю синхронизацию, конструкция которых предусматривает возможность под ключения соответствующих контактных уст ройств к внешним выводам интегральных, схем. Никаких других ограничений на схему и конструкцию объекта не накладывается. Тесты, получаемые с помощью данной системы, рассчитаны на применение совместно с любой контрольной аппаратурой, обеспечивающей подачу тестов на входы объектов контроля, считывание логичесхшх значений сигналов с выходов всех интегра ых схем объекта и сравнение этих значеий с эталонными значениями, заданным в рограмме контроля или получаемьаш от талонного образца объекта. На фиг. 1 приведена блок-схема системы; на фиг. 2 - блок-схема специализированного процессора. Система содер ниит образец объекта It интегральные схемы з,- 2ц , регистр 3 входного вектора, - коммутатор 4, шины 5, связи, блок 6 сопряжения ЦВМ 7, устройства коммутации8 8{ специализированные процессоры 9({ и ОЗУ Ю. Специализированный процессор содержит регистр 11 адреса, регистр 12 данных, блок 13 управления, счетчик 14 команд, буферный регистр 15, регистр 16 кода операций блок 17 логических операций, блок 18 коммутации, индикатор 19 окончаний моделирования, дешифратор 2О результатов и дешифратор 21 адреса процессора. Регистр 3 входного вектора предназначен для запоминания и приложения ко входам объекта 1 сигналов, соответствующих текущему такту исследуемой входной последовательности. С помощью коммутатора 4 обеспечивается последовательно-параллельный прием данных в регистр 3 с шин сопряжения с ЦВМ машиной. Каждый процессор 9 слулшт для моделирования соответствующей ему интегральной схемы 2 объекта 1 (с учетом; имитируемых неисправностей этой схемы) с помощью программы, хранимой в соответствующем данному процессору ОЗУ 1О. Система работает следующдм образом. Вместе с соответствующим кo fflлeкcoм программ ЦВМ 7 обеспечивает выполнение следующих управляющих функций в системе: генерирование входных последовательностей, испытываемых в качестве возможных тестов для заданного цифрового объекта; приложение входнък последовательностей и сигналов синхронизации ко входам объекта (через коммутатор 4 и регистр 3); загрузку моделирующих программ в ОЗУ 10 (через шины связи 5 и соответствующие узлы процессоров 9); модификацию моделирующих программ в соответствии с типами проверяемых неисправностей интегральных схем объекта; запуск процессора 9 в каждом такте проверяемой входной последовательности для вьшолнения моделирующих программ; обнаружение момента окончания работы моделирующих программ в каждом такте и накопление в ОЗУ машины данных, опреде- дяющих все обнаруживаемые в текущем так-

niO

и

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Устройство для формирования тестов | 1974 |

|

SU477413A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА ДИАГНОСТИРОВАНИЯ ЦИФРОВЫХ УСТРОЙСТВ | 1994 |

|

RU2097827C1 |

| Устройство для управления режимамиОбМЕНА РЕзЕРВиРОВАННОй СиСТЕМы | 1979 |

|

SU849216A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| МОДЕЛИРУЮЩИЙ КОАП | 2013 |

|

RU2516703C1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1288704A1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

Составитель А. Жеренов Редактор Л. Утехина Техред И. Ковач Корректор А, Лакида

Заказ 4995/432Тираж 1029Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Авторы

Даты

1976-08-05—Публикация

1975-01-30—Подача