(54) ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1976 |

|

SU553682A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Логическое запоминающее устройство | 1981 |

|

SU972589A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Логическое запоминающее устройство | 1981 |

|

SU974413A1 |

| Устройство для мажоритарного декодирования | 1987 |

|

SU1517137A1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| Устройство автоматического выравнивания времени распространения при передаче дискретных сообщений по параллельным каналам | 1975 |

|

SU604160A1 |

| Устройство для ввода-вывода информации | 1983 |

|

SU1136173A1 |

1

Изобретение относится к ЗУ и может быть использовано, в частности для кодирования и декодирования информации,

Известны логические ЗУ (1, 2, 3) пассивного l, и активного типа 2, Однако в -таких устройствах нельзя проводить кодирование и декодирование информации.

Наиболее близким техническим решением к данному изобретению является логическое ЗУ, содержащее дешифратор, соединенный с регистром адреса и П -разрядным блоком памяти, регистр слова, управляющие блоки, подключенные к блоку , и управляющие шины ЕЗ.

Однако это устройство не позволяет кодировать и декодировать информацию.

Целью изобретения является расширение функциональных возможностей устройства за счет выполнения в нем кодирования и декодирования информации.

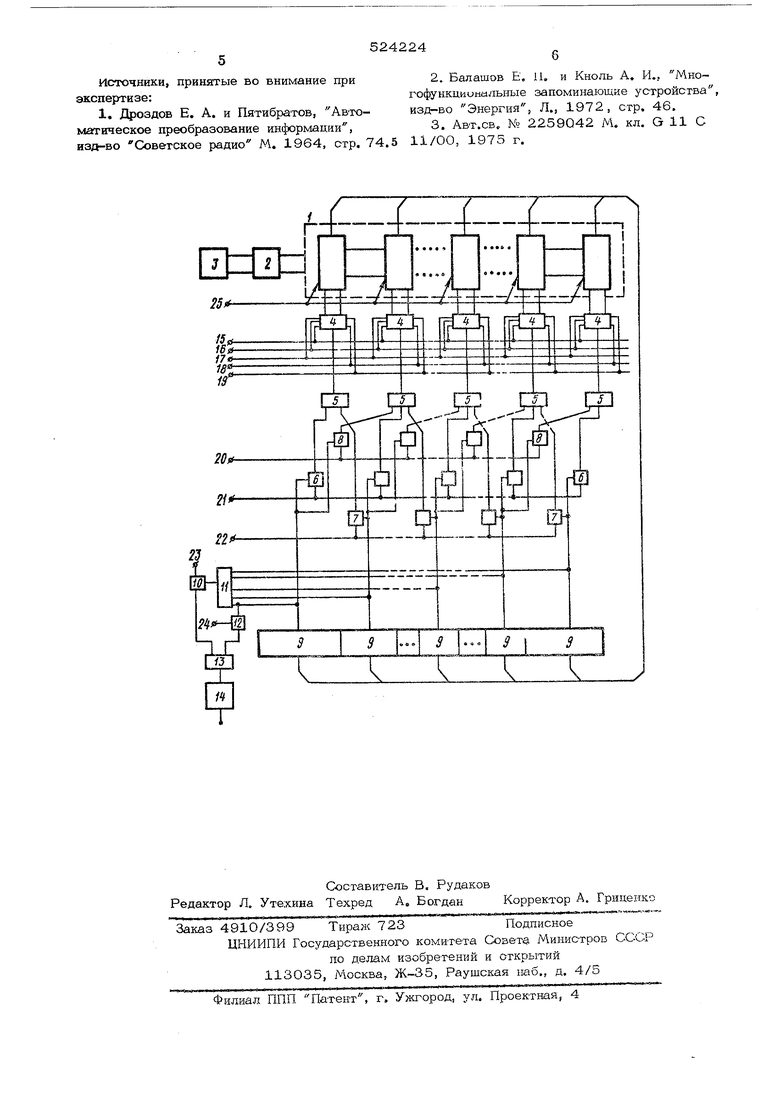

Поставленная цель достигается тем, что предложенное устройство содержит элементы И и ИЛИ и триггер Первый вход 1 -го разрядного элемента ИЛИ ( 1 - 1, 2,..., тг ) подключен к выходу i -го эпемен

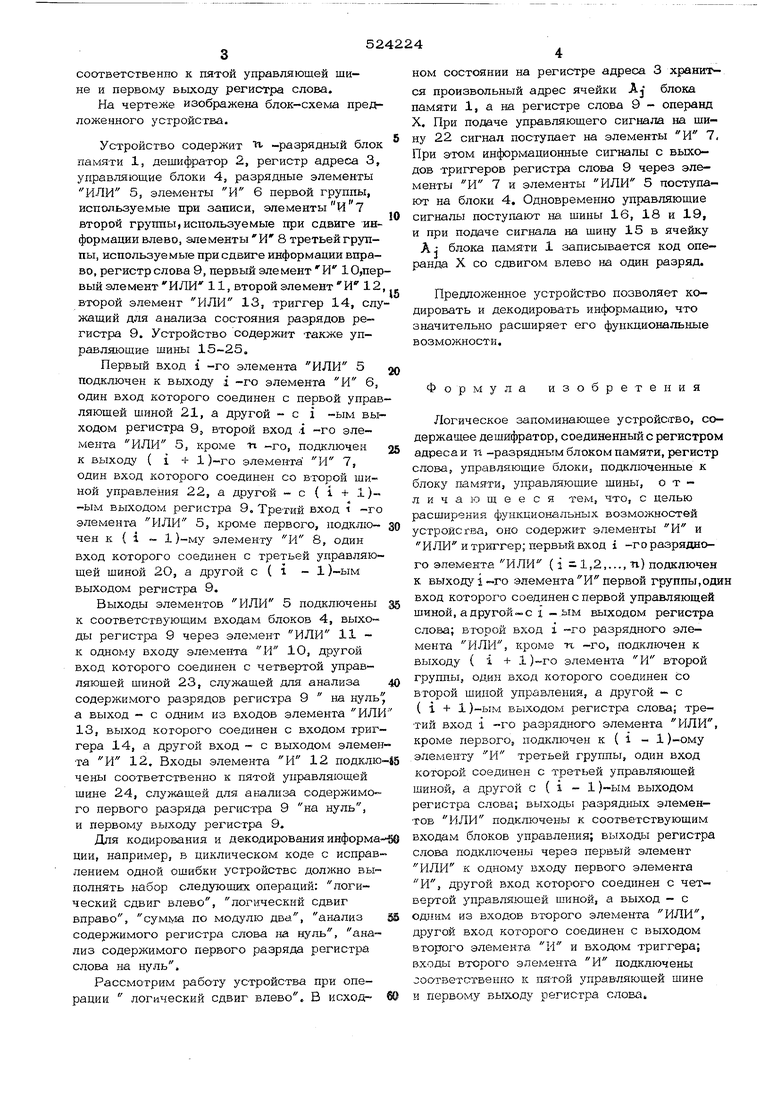

та И первой группы, один вход которого соединен с первой управляющей щиной, а другой - с i -ым выходом регистра слова Второй вход i -го разрядного элемента ИЛИ, кроме Т1 -го, подключен к выходу ( i + 1)-го элемента И второй группы, один вход которого соединен со второй шиной управления, а другой - с ( i + 1)-ым выходом регистра слова. Третий вход i -го разрядного элемента ИЛИ, кроме первого подключен к ( i - 1)-му элементу И третьей группы, один вход которой соединен с третьей управляющей щиной. а другой с ( i - 1) -ым выходом регистра слова. Выходы разрядных элементов ИЛИ подключены к соответствующим входам блоков управления. Выходы регистра слова подключены через первый элемент ИЛИ к одному входу первого элемента И, другой вход которого соединен с четвертой управляющей шиной, а выход - с одним из входов элемента ИЛИ, выход которого соединен со входом триггера, а другой вход - с выходом второго элемента И. Входы второго элемента И подключены соотвегственпо к пятой управляющей шине и первому выходу регистра слова. На чертеже изображена блок-схема пред ложенного устройства. Устройство содержит fi -разрядный блок памяти 1, дешифратор 2, регистр адреса 3, управляюш,ие блоки 4, разрядные элементы ИЛИ 5, элементы И 6 первой группы, используемые при записи, элементы И 7 второй группы,используемые при сдвиге ин формации влево, элементы И 8 третьей группы, используемые при сдвиге информации вправо, регистр слова 9, первый элемент И 10,пер вый элемент ИЛИ 11, второй элемент И 12 второй элемент ИЛИ 13, триггер 14, слу жащий для анализа состояния разрядов регистра 9. Устройство содержит также управляющие шины . Первый вход i -го элемента ИЛИ 5 подключен к выходу i го элемента И 6, один вход которого соединен с первой управ ляющей шиной 21, а другой - с i -ым вы ходом регистра 9, второй вход i -го элемента ИЛИ 5, кроме -п -го, подключен к выходу ( i -ь 1 )-го элемента И 7, один вход которого соединен со Второй шиной управления 22, а другой - с { i + 1)-ым выходом регистра 9. Третий вход i -го элемента ИЛИ 5, кроме первого, подключен к { i - 1)-му элементу И 8, один вход которого соединен с третьей управляющей шиной 20, а другой с { г - 1 )-ым выходом регистра 9. Выходы элементов ИЛИ 5 подключены к соответствующим входам блоков 4, выхо ды регистра 9 через элемент ИЛИ 11 к одному входу элемента И 10, другой вход которого соединен с четвертой управляющей шиной 23, служащей для анализа содержимого разрядов регистра 9 на нуль а выход - с одним из входов элемента ИЛИ 13, выход которого соединен с входом триггера 14, а другой вход - с выходом элемен та И 12, Входы элемента И 12 подклю чены соответственно к пятой управляющей шине 24, служащей для анализа содержимого первого разряда регистра 9 на нуль, и первому выходу регистра 9. Для кодирования и декодирования информа ции, например, в циклическом коде с исправлением одной ошибки устройстве должно вы полнять набор следующих операций: логический сдвиг влево, логический сдвиг вправо, сумма по модулю два, анализ содержимого регистра слова на нуль, анализ содержимого первого разряда регистра слова на нуль. Рассмотрим работу устройства при операции логический сдвиг влево. В исход™ ном состоянии на регистре адреса 3 хранится произвольный адрес ячейки Aj блока памяти 1, а на регистре слова 9 - операнд X, При подаче управляющего сигнала на шину 22 сигнал поступает на элементы И 7, При этом информационные сигналы с выходов триггеров регистра слова 9 через элементы И 7 и элементы ИЛИ 5 поступаЮт на блоки 4, Одновременно управляющие сигналы поступают на щины 16, 18 и 19, и при подаче сигнала на шину 15 в ячейку А.{ блока памяти 1 записывается код операнда X со сдвигом влево на один разряд. Предложенное устройство позволяет кодировать и декодировать ин(|юрмацию, что значительно расщиряет его функциональные возможности. зобретения Формула Логическое запоминающее устройство, содержащее дешифратор, соединенный с регистром адреса и п -разрядным блоком памяти, регистр слова, управляющие блоки, подключенные к блоку памяти, управляющие шины, отличающееся тем, что, с целью расширения функциональных возможностей устройсгва, оно содержит элементы И и ИЛИ и триггер; первый нход i -го разрядного элемента ИЛИ (i -1,2,...,п) подключен к выходу элемента И первой группы,один вход которого соединен с первой управляющей шиной, адругой с X - ь1м выходам регистра слова; вт-срой вход i го разрядного элемента ИЛИ, кроме TV -го, подключен к выходу ( i + 1)го элемента И второй группы, один вход которого соединен со второй щиной управления, а другой - с ( i + 1 ) выходом регистра слова; третий вход i -го разрядного элемента ИЛИ, кроме первого, подключен к ( 1 - 1 )-ому элементу И третьей группы, один вход которой соединен с третьей управляющей шиной, а другой с ( i - 1 )ым выходом регистра слова; выходь разряд1-1ых элементов ИЛИ подключены к соответствующим входам блоков управления; выходы регистра слова подключены через первый элемент ИЛИ к одному входу первого элемента И, другой вход которого соединен с четвертой управляющей шиной, а выход - с одним из входов Второго элемента ИЛИ, другой вход которого соединен с выходом второго элемента И и входом триггера; входы Второго элемента И подключены соо-тветственно к пятой управляющей шине к первому выходу регистра слова. Источники, прингггые во внимание при экспертизе: 1. Ш)0здов Е. А. и Пятибратов, Автомагическое преобразование информации. изд-во Совегское радио М. 1964, сгр. 74.5

ZIZZirZTIIT

/

/

W /5 .

ш

-irr.-uv 2. Балашов Е, И. и Кноль А, И., Многофункциинальиые запоминающие устройства, изд-во Энергия, Л., 1972, стр. 46. 3. Авт.св, № 2259Q42 М. кп. G 11 С .-.-L л г Oi г J-X j-N л е ил.. / Ч 11/00, 1975 г.

Авторы

Даты

1976-08-05—Публикация

1975-03-14—Подача