(54) ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1981 |

|

SU972589A1 |

| Устройство для табличной реализации многоместных логических функций | 1982 |

|

SU1019455A1 |

| Логическое запоминающее устройство | 1981 |

|

SU963099A1 |

| Арифметико-логическое устройство | 1979 |

|

SU943709A1 |

| Логическое запоминающее устройство | 1975 |

|

SU524224A1 |

| Логическое запоминающее устройство | 1977 |

|

SU733024A1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| Программируемый контроллер | 1989 |

|

SU1780086A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1439681A1 |

1

Изобретение относится к запоминающим устройствам.

Известно логическое запоминающее устройство, содержащее дешифратор адреса, блок памяти, соединенный информационными входами с выходами управляю.щих логических схем, регистр адреса, регистр слова, управляющие щины 1 ,

Недостатком этого устройства является невозможность выполнения операций кодирования-декодирования информации.

Наиболее близким к предлагаемому изоЬретению является логическое запоминающее устройство, содержащее регистр адреса, соединенный с дешифратором адреса, выходы которого подключены к блоку памяти, вторые входы блока памяти подключены к выходам управляющих j логических схем, каждая управляющая логическая схема подключена к выходу соответствующего первого элемента ИЛИ, выходы каждого элемента ИЛИ подключены к соответствующим трем выходам логической схемы преобразования содержимого регистра слова, включающей элемент Ипрямой записи, элементы И левого сдвига на один разряд, элементы И правого сдвига на один разряд, регистр слова, входы которого соединены с выходами соответствующих разрядов блока памяти, выходьг регистра слова подключены к входам лоп-гческой схемы анализа содержимого регистра слова, включающей элементы И анализа содержимого ре10гистра на О, элемент И анализа соде1 жимого старшего разряда регистра слова на О, выходы логической схемы анализа регистра слова подключены к второму элементу ИЛИ, выход которого подклюtsчен к входу триггера, управляющие швны, Это логическое запоминающее устройство может выполнять операции кодирования, декодирования информации в циклическом 20 коде с исправлением одной ошибки, погические операции 2 ,

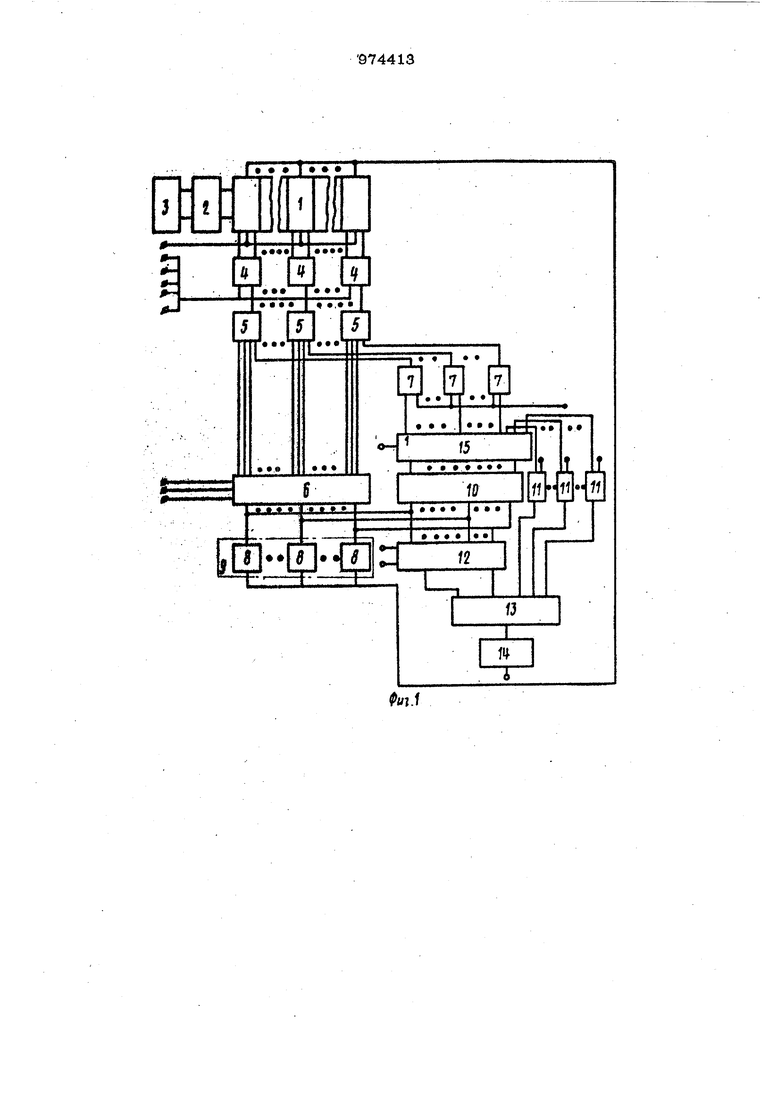

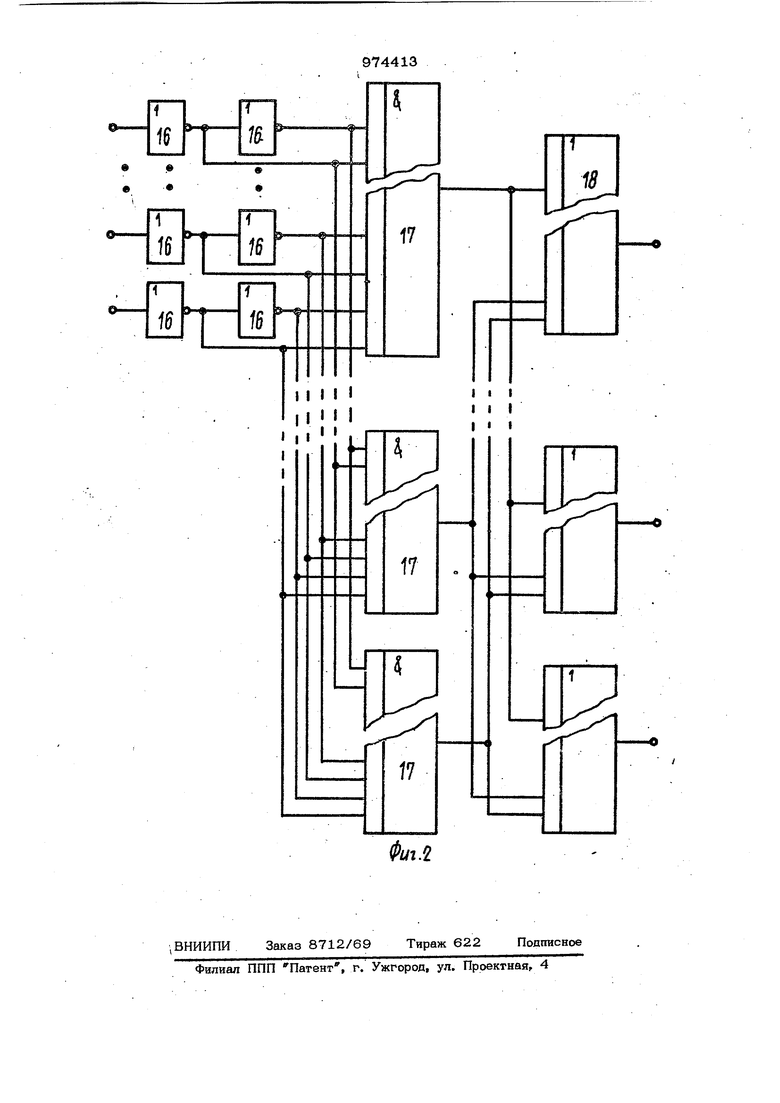

Недостатком известного устройства является низкое быстродействие при выполнении операции декодирования ни- формации в циклическом коде с исправлением 6 -ошибок. Цель изобретения - повышение бььстродействия при выполнении операции декодирования информации в циклическом коде с исправлением ошибок. Поставленная цель достигается тем, что в логическое запоминающее устройство, содержащее последовательно соединенные регистр адреса, дешифратор адреса и накопитель, группу логических блоков, группу элементов ИЛИ, преобразователь кодов, первый регистр, логичес кий блок, элемент ИЛИ и триггер, причем выходы накопителя подключены к входам первого регистра, выходы которого соединены с входами преобразователя кодов и логического блока, выходы которого подключены к одним из входов элемента ИЛИ, выход . которого соединен с входом триггера, одни из входов элемента ИЛИ группы подключены к выхода преобразователя кодов, а выходы соеди. нены с входами логических блоков груп пы, выходы которых соединены с одними из входов накопителя, управляющие входы лог ических блоков, накопителя и преобразователя кодов являются одними из управляющих входов устройства, введены группы элементов И, второй регистр и программируемая логическая матрица, входы которой подключены к выходам первого регистра, одни из выходов соединены с первыми входами элементов И первой группы, другие выходы програм мнруемой логической матрицы подключены к первым входам элементов И второй группы, выходы которых соединены с другими входами элемента ИЛИ, выходы элементов И первой группы подключены к другим входам элементов ИЛИ группы управляющие входы элементов И и второго регистра являются другими управля юхилми входами устройства. На фиг. 1 изображена структурная сх ма логического запоминающего устройства; на фиг. 2 - структурная схема прог раммируемой логической матрицы. Логическое запоминающее устройство (фиг. 1) содержит накопитель 1, дещифратор 2 адреса, регистр 3 адреса, группу логических блоков 4, группу элементо 5, преобразователь 6 кодов, первую груп пу элементов И 7, триггеры 8, образую щие первый регистр 9, программируемую лопетескую матрицу 10, вторую группу элементов И 11 логический блок 12, элемент И 13, триггер 14, второй регистр 15. Выхрд 1-го разряда регистpa 15 С 1 l-r(), где n , 1 -целые числа подключен к входу 1 -го элемента И 7, выход j -го разряда регистра 15 j()( , где зг- целое число 3 подключен к входу элемента И 11. Программируемая логическая матрица (фиг. 2) содержит элементы НЕ 16, элементы И 17, и элементы ИЛИ 18. Сущность формирования кодового многочлена циклического кода заключает ся в умножении информационной последовательностиP(...+ R, на и деление результата умножения на образующий полином (х). Полученный остаток соответствует проверочному многочлену. Декодирование - процесс определения кодового слова линейного кода по полученному набору - осуществляется в два этапа: вычисление синдрома полученного слова; определение по синдрому образующего смежного класса, который вычитается из полученного слова. Первый этап.сводится к получению Достатка (синдрома) от деления кодового многочлена, умноженного на X на образующий многочлен и выполняется аналогично операции кодирования информации. Наиболее труден второй этап исправ ления ощибок. Множество рщибок, вес которых не превыщает. покрывается множеством (x)j , состоящих из конечного числа полиномов Q.(x), , Сз(г(х),..., )- . Согласно разработанному алгоритму декодирования требуется вычислить веса разностей по модулю qfcx) и по виду этой разности произвести исправление ощибок той или иной конфигурации. Вес - это число ненулевых коэффициентов. Пример. Операция чтение полинома ощибки. в исходном состоянии на регистре 9 находится операнд X, который поступает на вход матрицы 10. На выходе матрицы 10 снимается выходной операнд У, который записьшается в регистр 15. Выполнение операции анализ i -го разряда регистр af. в исходном состо5шии операнд (п-1сч-у) находится в регистре 15. При подаче управляющего сигнала на управпяюший вход (Л -ого элемента И 11 информационный сигнал с j -го разряда регистра 15 проходит через данный элемент И 11 и элемент ИЛИ 13 на вход триггера 14 и устанавливает его значение, соответствующее значению информационного сигнала j -го разряда , регистра 15. Вьшолнение операции запись содержимого регистра накопитель. В исходном состоянии в регистре 15 содержится операнд У. При поступлении сигнала на управляющие входы элементов И 7 он поступает на эти элементы и информационные сигналы операнда У проходят через элементы И 7 и ИЛИ 5 на входы блоков 4 и при подаче соответствующей комбинации сигналов на управляющие входы этих блоков операнд У по адресу X, установленному на регистре адреса, записывается в накопитель 1. Технико-экономическое преимущество предлагаемого устройства заключается в повышении быстродействия устройства ino сравнению с прототипом. Формула изобретения Логическое запоминающее устройство содержащее последовательно соединенны регистр адреса, дешифратор адреса и накопитель, группу логических блоков, группу элементов ИЛИ, преобразователь кодов, первый регистр, логический блок, элемент ИЛИ и триггер, причем выходы 9 3« накопителя подключены к входам первого регистра, выходы которого соединены с входами преобразователя кодов в логвческого блока, выходы которого подшпочены к одним из входов элемента ИЛИ, выход которого соединен с входом триггера, одни из входов элементов ИЛИ группы подключены к выходам преобразователя кодов, а выходы соединены с входами логических блоков группы, выходы которых соединены с одними вз входов накопителя, управляющие входы логических блоков, накопителя н преобразователя кодов являются одними из управляющих входов устройства, отличающееся тем, что, с целью повыщения быстродействия устройства, в него введены группы элементов И, второй регистр и программируемая логичеокая матрица, входы которой подключены к выходам первого регистра, одни из выходов соединены с первыми входами элементов И первой группы, другие выходы программируемой логической матрицы подключены к первым входам алеме тов И- второй группы, выходы которых соединены с другими входами элемента ИЛИ, выходы элементов И первой ipyntnu подключены к другим входам элементов ИЛИ группы, управляющие входы элементов И и второго регистра являются дру гими управляющими входами устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 477464. кл. Gi Ц С 15/ОО, 1974, 2,Авторское свидетельство СССР № 524224, кл. G 11 С 15/00, 1в75 (прототип).

I I

I I I

I

I

I « I

:

W2.2

Авторы

Даты

1982-11-15—Публикация

1981-03-27—Подача