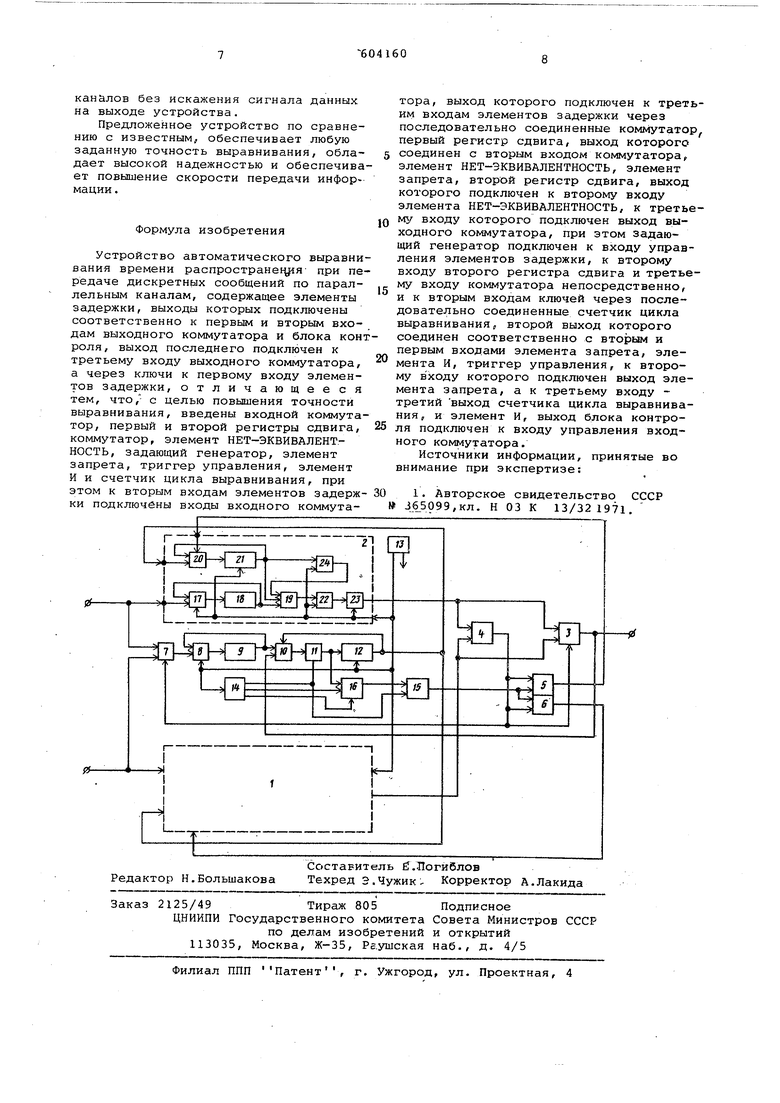

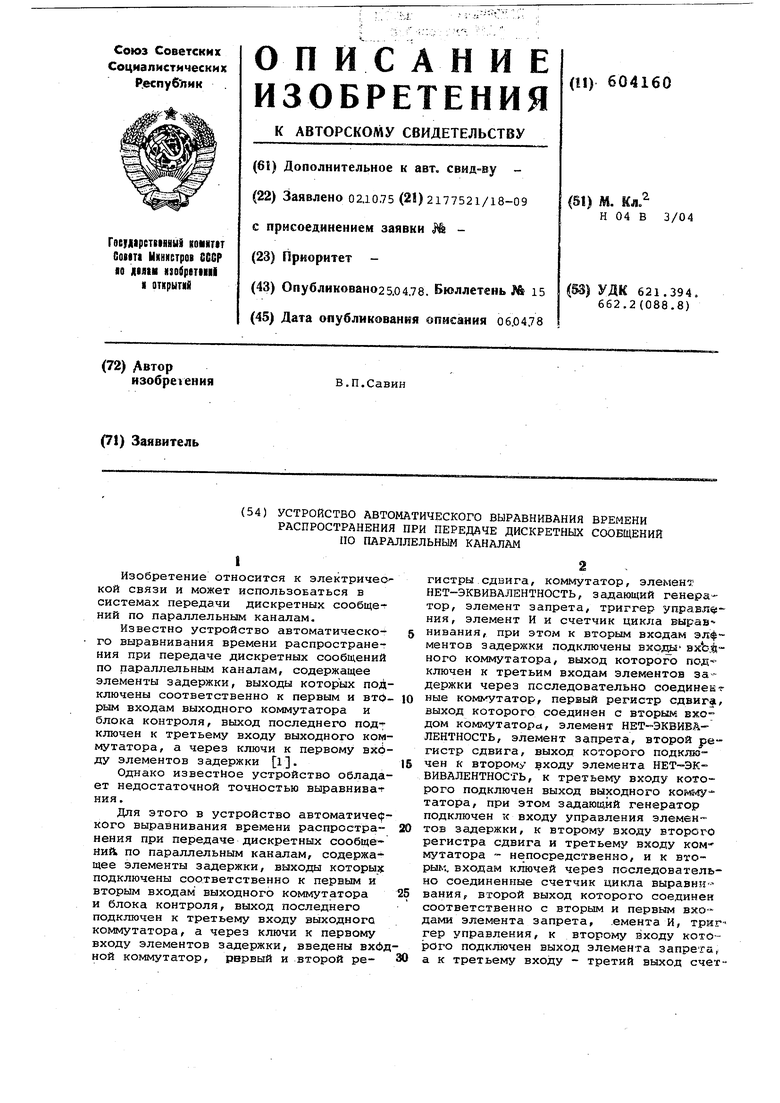

чика цикла выравнивания, и элемент И, выход блока контроля подключен к вход управления входного коммутатора. На чертеже изображена структурная электрическая схема предложенного уст ройства. Устройство содержит элементы 1 и 2 задержки, выходы которых подключены соответственно к первым входам выход- ного коммутатора 3 и блока 4 контрол, выход которого подключен к третьему входу выходного коммутатора 3, а через ключи 5 и 6, к первому входу элементов 1 и 2 задержки, к вторым входам которых подключены входы входного ком мутатора 7, выход которого подключен к третьим входам элементов 1 и 2 задержки через последовательно соединенные коммутатор 8; первый регистр 9 сдвига, выход которого соединен с вто рым входом коммутатора 8; элемент НЕТЭКВИВАЛЕНТНОСТЬ 10; элемент 11 запрета и второй регистр 12 сдвига, выход которого подключён к второму входу элемента НЕТ-ЭКВИВАЛЕНТНОСТЬ 10, к третье му входу которого подключен выход выходного коммутатора 3, при этом задающий генератор 13 подключен к входу управления элементов 1 и 2 задержки, к второму входу второго регистра 12 сдвига и третьему входу коммутатора 8 непосредственно, и к вторым входам ключей 5 и 6 через последовательно соединенные счетчик 14 цикла выравнивания , второй выход которого соединен соответственно с вторым и первым входами элемента 11 запрета и элемента И 15; триггер 16 управления, к второму° входу которого подключен выход элемента 11 запрета, а к третьему входу третий выход счетчика 14, и элемент И 15, выход блока контроля 4 подключен к входу управления входного коммутатора .7 . Каждый элемент 1 и 2 задержки содержит коммутатор 17,регистр 18 сдвига, элемент И 19, коммутатор 20, регистр 21 сдвига, триггер 22 с раздельными входами, управляемый Д-триггер 23 и триггер 24 с раздельными вхсэдами Устройство работает следующим образом. В начальный момент работы элементы 1 и 2 задержки устанавливают в положение, соответствующее значению задержки, равному .к или TiK -двоичных разрядов, где максимальный временной сдвиг одного канала относительно другого. Допустим, единичный потенциал на выходе блока 4 соответствует выбору сигнала данных, поступающих с второго входа устройства на элемент 1 задержки. Тогда входной коммутатор 7 пропускает на первый вход коммутатора 8 сигнал данных с первого входа устройства, а выходной коммутатор 3 пропускает на выход устройства сигнал данных второх о входа устройства, прошедший через элймент 1. Сигнал данных первого входа устройства стробируется импульсами ч стоты f, длительностью Т (где ).Логическое значение сигнала данных в момент стробирования проходит через коммутаторы 7,8 и 17 и записывается в регистры 9 и 18 сдвига. Триггер 24 с раздельными входами устанавливается в единичное (исходное состояние от импульса частоты f, поступающего на единичный вход. В управляемый Д-триггер 23 производится перепись с триггера 22 предварНтельно записанного в него предыдущего единичного элемента, и одновременно установка триггера 22 в нулевое (исходное) состояние. Регистры 12 и 21 в это время находятся в режиме хране- ния. Регистр 12 сдвига в исходном со тоянии выравнивания заполнен нулями. После окончания режима записи регист-г ров 9 и 18 сдвигов наступает режим рециркуляции регистров 12, 9,18и 21. В начальный момент времени в регистрах 21 хранится 2т|К -разрядное двоичное слово с единицей в пК -ом разряде. На выходах элементов 1 и 2 с часто -, той fi появляется логическое значениф пК -го разряда, а на втором входе элемента НЕТ-ЭКВИВАЛЕНТНОСТЬ 10 nortfческое значение -пК-го разряда злемен- та 1 на все время режима рециркуляци. Элемент НЕТ-ЭКВИВАЛЕНТНОСТЬ 10 р4ализует переключательную функцию j jslTjCxixz-t-XiXj), де X,-логическое значение первого хода, Xj - логическое значение второго хода, X.J - логическое значение входа правления. Таким образом, элемент НЕТ-ЭКВИВА- ЕНТНОСТЬ 10 производит операцию оразрядного сравнения двоичного слоа регистра 9 с логическим значением ыхода устройства и, одновременно,опеацию поразрядного логического умноения результата сравнения с содержи ым регистра 12. На вход- элемента 11 подается инерсное значение сигнала с выхода элеента НЕТ-ЭКВИВАЛЕНТНОСТЬ Ю.СчеТик 14 задает количество последовательых операций сравнения и логического множения, по результатам которых выноится решение о временном рассогласоании сигнала данных первого и второо входов устройства. Допустим цикл выбран равным N перидам частоты J1, тогда на (N-2)-ом пеиоде частоты jj , на втором выходе екодера счетчика 14 появится импульс длительностью , равной периоду часто ты -fi , который поступает на нулевой вход триггера 16 управления с раздельными входами и устанавливает его в исходное (нулевое) состояние. На (N -1)-ом периоде частоты f на третьем выходе декодера счетчика 14 появится импульс/ который поступает на вход управления триггера 16 и разрешает на все время (N -1)-и рециркуляции установку триггера 16 сигналом инверс ного значения с выхода элемента 11,пос тупающего на единичный вход триггера 1 После окончания (N-1)-го периода , рециркуляции в регистре 12 будет находиться двоичное 2 разрядное слово, заполненное единицами, за исключением К соседних разрядов, заполненных нулями. Эти К соседних разрядов однознач но определяют место в элементах 1 и 2 задержки, в котором находится единичный элемент сигнала данных первого и второго входов, совпадающий с единичным элементом, считываемым с выходов элементов 1 и 2 и поступающим на выход устройства. На N -ом периоде час/тоты j на первом выходе декодера счет чика 14 появится импульс с длительностью, равной периоду частоты fi , который поступает на вход управления эле мента 14 и на вход элемента И 15. В результате на все время fT -го периода рециркуляции на выходе элемента 11 устанавливается нулевое значение, регистр 12 заполняется нулями и одновременно двоичное слово, хранившееся в регистре 12 и характеризующее величину задержки, поступает на вход ввода величины элемента 2 задержки. Одновременно логическое значение выхода триггера 16 через элемент И 15 и ключи 4 (5) поступает на вход управления ввода величины задержки в элементах 1 и 2. В случае единичного потенциала на выходе триггера 16 коммутатор 20 элементов 1 и 2 пропускает на вход регист ра 21 в режиме рециркуляции двоичное слово величины задержки сигнала данных первого и второго входов устройства. В случае нулевого потенциала на выходе триггера -16 управления коммутатор 20 пропускает на вход регистра 21 в режиме рециркуляции сигнал с выхода регистра 21 и, таким образом,сохраняется прежнее значение величины задержки элементов 1 и 2. На третий вход элементов I и 2 пот;, дается с выхода регистра 12 инверсный сигнал, таким образом, регистр 21 хранит двоичное 2п.К -разрядное слово,заполненное нулями за исключением К ср. седних разрядов, заполненных единица ми. С помощью триггера 24 с раздельными входами производится считывание в режиме рециркуляции единичного элеме та в регистре 18 с номером разряда, совпадающим с номером первой правой единицы ( из К единиц) в регистре 21 Логическое значение единичного элемечта, считанного с регистра 18 сдвига, через элемент И 19 записывается в триггер 22 с раздельными входами, выполни-юцего функции промежуточной памяти. Очередным импульсом частоты J длительностью Т. производится запись сигнала на выходе триггера 22 в Д-триггер 23, установка триггеров 22 и 24 i исходное состояние, перевод регистров 21 и 12 в режим хранения, перевод KOI мутатора 17 с регистром 18 и коммутатора 8 с регистром 19 s режим записи очередного единичного элемента сигнала данных первого и второго входов устройства. Допустим п 7,5,, В 1200 5оа, где суммарная нестабильность частоты задающего генератора и генератора на передающей стороне В - скорость передачи информации.. Тогда емкость регистров 12, 9, 18, и 21 равна 2-7-3 42 (разряда), где Р В 1200 Гц. j, F 1200-5 b600r4, (2TMi. 1-1V1200а()-(5(800гц . Вследствие нестабильности ьЧ с учетом двух параллельных каналов, через М единичных элементов, где гк1-ач - IT (элементов) будет происходить флюктуация значащих, моментов сигнала данных первого входа и второго входа устрой ;тва на -Ь. величину.. С учетом этого выбирается К «М например N 15. Вероятность ложного выравнивания при этом будет равна Р(0,5Г СО,5)5гб-Ю .е. по существу равна нулю. Тогда возможная погрешность выравивания при переключении из-за возможого отставания определения величины адержки вследствие суглмарной нестаильности и возможности ошибок в сигале данных параллельных каналов ке удет превышать величины . При еЗ, это эквивалентно 33% от Тд. Учитывая наличие системы синхрониации дискретной информации в приемике информации с Исправляющей cnocoie|остью, равной 48%, можно утверждать.,; то уже при , возможно переключение

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля экспоненциальных процессов | 1987 |

|

SU1500997A1 |

| Устройство для умножения | 1984 |

|

SU1256016A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1228290A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Вычислительное устройство | 1983 |

|

SU1144105A2 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| Устройство для исправления ошибок | 1990 |

|

SU1783622A1 |

| Интегро-дифференциальный вычислитель | 1983 |

|

SU1108445A2 |

| Устройство формирования много-СТупЕНчАТОгО КВАзиСиНуСОидАльНОгОТРЕХфАзНОгО НАпРяжЕНия | 1978 |

|

SU809437A1 |

| Функциональный преобразователь | 1982 |

|

SU1100621A1 |

Авторы

Даты

1978-04-25—Публикация

1975-10-02—Подача