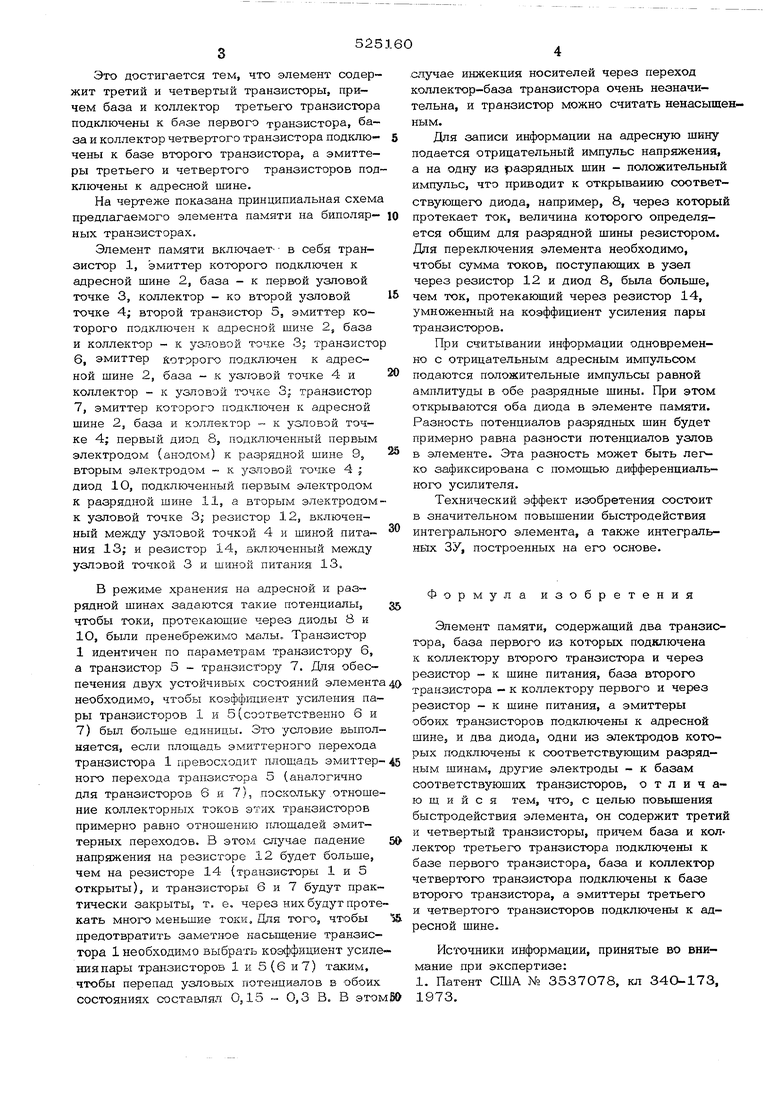

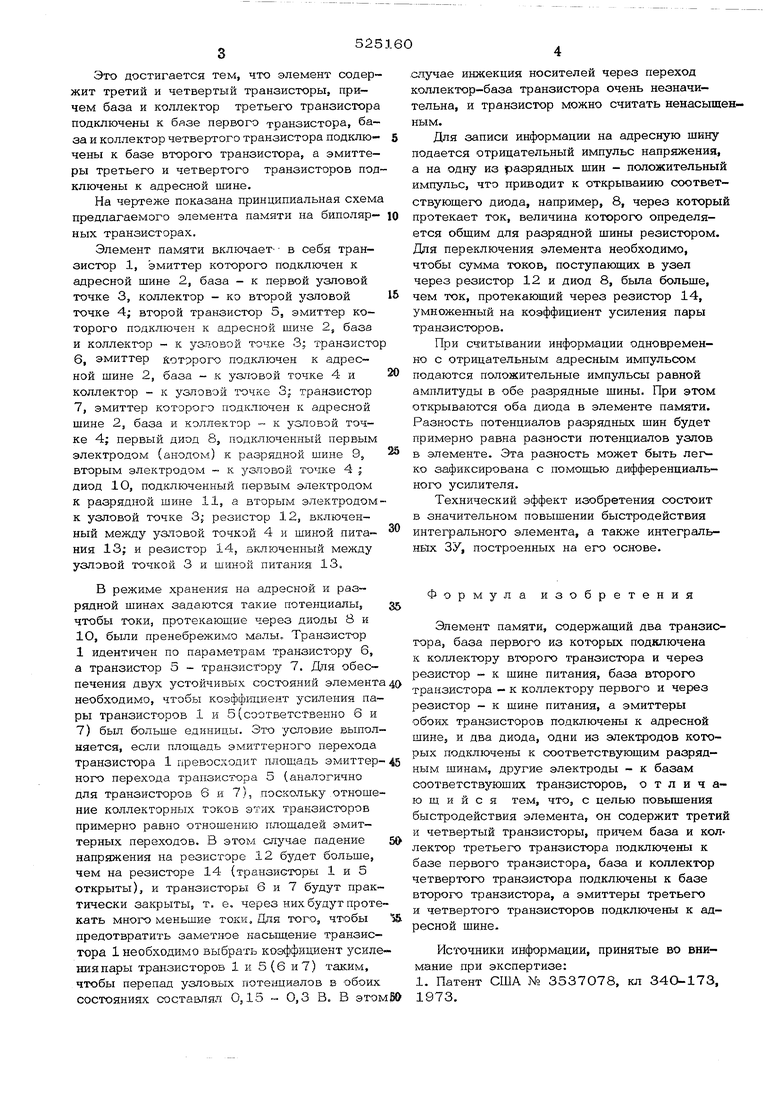

(54) ЭЛЕМЕНТ ПАМЯТИ Это достигается тем, что элемент содержит третий и четвертый транзисторы, причем база и коллектор третьего транзистора подключены к базе первого транзистора, база и коллектор четвертого транзистора подклю- чены к базе второго транзистора, а эмиттеры третьего и четвертого транзисторов под ключены к адресной шине. На чертеже показана принципиальная схем предлагаемого элемента памяти на биполяр- ных транзисторах. Элемент памяти включает в себя транзистор 1, эмиттер которого подключен к адресной шине 2, база - к первой узловой точке 3, коллектор - ко второй узловой точке 4; второй транзистор 5, эмиттер которого подключен к адресной шине 2, база и коллектор - к уаповой точке 3; транзисто 6,эмиттер котррого подключен к адресной шине 2, база - к уз/ювой точке 4 и коллектор - к узловой точке 3; транзистор 7,эмиттер которого подключен к адресной шине 2, база и коллектор - к узловой точке 4; первый диод 8, подключенный первым электродом (анодом) к разрядной шине 9, вторым электродом - к уаповой точке 4 ; диод 10, подключенный первым электродом к разрядной шине 11, а вторым электродом к узловой точке 3; резистор 12, включенный между уачовой точкой 4 и шиной питания 13; и резистор 14, включенный между узловой точкой 3 и шиной питания 13.

В режиме хранения на адресной и разрядной шинах задаются такие потенциалы, чтобы токи, протекающие через диоды 8 и 1О, были пренебрежимо малы. Транзистор 1 идентичен по параметрам транзистору 6, а транзистор 5 - транзистору 7. Для обеспечения двух устойчивых состояний элемента необходимо, чтобы коэффипиент усиления пары транзисторов 1 и 5(соотБетственно б и 7) был больше единицы. Это условие выполняется, если площадь эмиттерного перехода транзистора 1 гфевосдодит площадь эмиттерного перехода транзистора 5 (аналогично для транзисторов 6 и 7), поскольку отношение коллекторных токов этих транзисторов примерно равно отношению площадей эмиттерных переходов. В этом случае падение напряжения на резисторе 12 будет больше, чем на резисторе 14 (транзисторы 1 и 5 открыты), и транзисторы 6 и 7 будут практически закрыты, т, е, через них будут протекать много меньшие токи. Для того, чтобы предотвратить заметное насыщение транзистора 1 необходимо выбрать коэффициент усипе кия пары транзисторов 1 и 5(6 и 7) таким, чтобы перепад узловых потенциалов в обоих состояниях составлял 0,15 - 0,3 В. В этом

них ЗУ, построенных на его основе.

Формула изобретения

Элемент памяти, содержащий два транзистора, база первого из которых подключена к коллектору второго транзистора и через резистор - к шине питания, база второго транзистора .- к коллектору первого и через резистор - к шине питания, а эмиттеры обоих транзисторов подключены к адресной шине, и два диода, одни из электродов которых подключены к соответствующим разрядным шинам, другие электроды - к базам соответствующих транзисторов, отличающийся тем, что, с целью повышения быстродействия элемента, он содержит трети и четвертый транзисторы, причем база и коллектор третьего транзистора подключены к базе первого транзистора, база и коллектор четвертого транзистора подключены к базе второго транзистора, а эмиттеры третьего и четвертого транзисторов подключены к адресной шине.

Источники информации, принятые во внимание при экспертизе:

1. Патент США № 3537078, кл 340-173, 1973. случае инжекция носителей через переход коллектор-база транзистора очень незначительна, и транзистор можно считать ненасыщенным. Для записи информации на адресную шину подается отрицательный импульс напряжения, а на одну из разрядных шин - положительный импульс, что приводит к открыванию соответствующего диода, например, 8, через который протекает ток, величина которого определяется общим для разрядной щины резистором. Для переключения элемента необходимо, чтобы сумма токов, поступающих в узел через резистор 12 и диод 8, была больше, чем ток, протекающий через резистор 14, умноженный на коэффициент усиления пары транзисторов. При считывании информации одновременно с отрицательным адресным импульсом подаются положительные импульсы равной амплитуды в обе разрядные шины. При этом открываются оба диода в элементе памяти. Разность потенциалов разрядных шин будет примерно равна разности потенциалов узлов в элементе. Эта разность может быть лег ко зафиксирована с помощью дифференциального усилителя. Технический эффект изобретения состоит в значительном повышении быстродействия интегрального элемента, а также интеграль52. Патент США № 3810130, кл. 3401973. 525160 6 173, 3. Патент ФРГ № 1912176, кл. 42 t , 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающий элемент | 1975 |

|

SU562866A1 |

| Запоминающее устройство | 1985 |

|

SU1256097A1 |

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

| Устройство для обращения к памяти (его варианты) | 1982 |

|

SU1092561A1 |

| Запоминающее устройство | 1985 |

|

SU1305774A2 |

| Тлэс-ттл преобразователь | 1977 |

|

SU617844A1 |

| Усилитель записи-считывания | 1986 |

|

SU1437913A1 |

| Накопитель для запоминающего устройства | 1983 |

|

SU1137537A1 |

| Формирователь импульсов | 1974 |

|

SU493906A1 |

| Оперативное запоминающее устройство | 1990 |

|

SU1809466A1 |

Авторы

Даты

1976-08-15—Публикация

1975-02-03—Подача