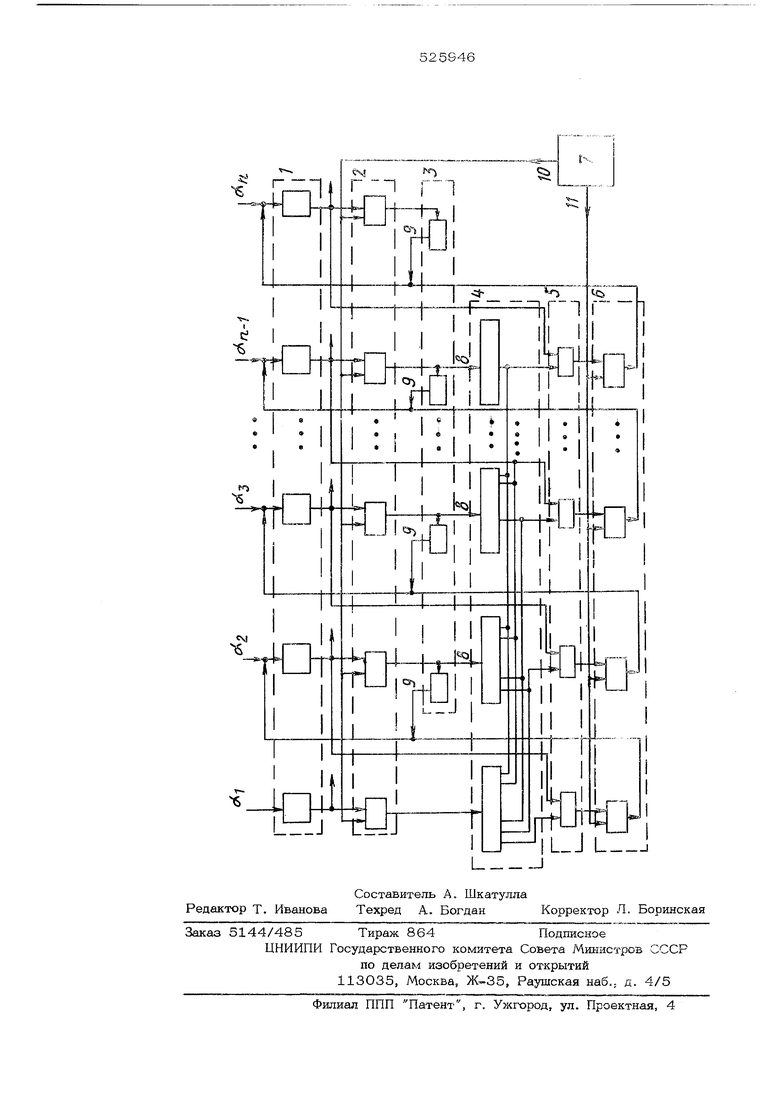

На чертеже изображена блок-схема предлагаемого устройства. Преобразователь содержит входной регистр 1 , первый блок элементов И 2, дешифратор 3, блок памяти 4, блок 5 модульных сумматоров, второй блок 6 элементов блок управления 7, группу выходов 8 дешифратора 3, вторую группу выходов 9 дешифра тора, первый выход 10 блока управления 7 и второй выход 11 блока управления 7. Преобразователь работает следующим образом. На входы преобразователя поступает информация, соответствующая представлению исходного числа в системе остаточных классов. Эта информация записывается во входно регистр 1. На k -том такте работы преобраз вателя управляющим сигналом с первого выхода 10 блока управления 7 разрешается пе редача остатка только по k -ому основанию через первый блок элементов И 2 на дешифратор 3. С первой группы выходов 8 дешифратора 3 этот остаток поступает на соответ ствующий элемент блока памяти 4. Кроме того, этот остаток в дешифраторе расшифровывается и со второй группы выходов 9 дешифратора как цифра полиадического кода заносится во входной регистр 1. При расшифровке в дешифраторе 3 реализуется формула- остаток числа по осно попученный в результате (.k.ого такта работы устройства. Поскольку остаток по первому основанию равен первой цифре полиадического кода х расшифровки этого остатка в дешифраторе 3 не производится. Поэтому остаток по первому основанию с первого выхода первого блока элементов И 2 передается непосредствен но на первый вход блока памяти 4. В блоке памяти формируются дополнительные коды остатков минимальных чисел по основаниям формирование вели к+1/ f где aL . j - остаток минимального числа -ому основанию на k-ом такте ра- ПОI-lyiVAJf i V JniJiJCiJnLJrJLiVy Jnc Г J.vj. Л. J, V- боты преобразователя. Дополнительные коды остатков минимальных чисел поступают на входы блока 5 модульных сумматоров, на вторые входы которых с выходов входного регистра поступают остатки по соответствую-бО шим основаниям, представляющие результаты работы преобразователя в предьщущем такте. При этом на выходе блока 5 формируются остатки вида: к-1 к к-1 .к -ot ОС - л оС , к K+V MZ. я п где - J - остаток по j -ому основанию после (lc-l)-ro такта работы преобразователя. Таким образом в преобразователе осуществляется последовательная нулевизация исходного числа. При этом по основаниям Р ( i 1, 2,.,. , К. ) выработка дополнительных кодов остатков минимальных чисел на k -ЮМ такте работы преобразователя не производится, т.е. соответствующие элементы блока памяти 4 для каждого последующего такта упрощаются и для последнего (П -1)-го такта происходит формирование кодов только по последнему ( П -му) основанию. Результаты k--oro такта работы преобразователя передаются через второй блок 6 элементов И на входы входного регистра 1. При этом на управляющие входы второго блока элементов И поступает управляющий сигнал со второго выхода 11 блока управления 7. Этим сигналом обеспечивается передача на входной регистр 1 только остатков по основаниям PJ ( j )с + 1 , к + 2,... п). В результате fc -юго такта работы преобразователя во входном регистре 1 на триггерах, соответствующих остаткам по основаниям Tt( - J )будут находиться цифры полиади-ческого кода числа, а на триггерах, соответствующих остаткам PJ ( K-t-i, K-t-a,... ri), будут находиться результаты нулевизации исходного числа после k-ого такта работы преобразователя. Для своей реализации преобразователь требует значительно меньших аппаратурных затрат, чем прототип. Основное отличие аппаратурных затрат заключается в разном количестве структурных элементов типа модульных и двоичных сумматоров и элементов дешифраторов. Так и в прототипе используются: модульных сумматоров т двоичных сумматоров n-i; дешифраторов f-гг. Предлагаемый преобразователь требует ля своей реализации 2 ( П -1) структурных лементов типа модульных сумматоров и деифраторов. Поскольку затраты на первый и второй блок элементов И приближаются к затратам на выходной регистр прототипа, в прототипе используется структурных элементов типа сумматоров и дешифраторов в П -3 2(п-1) раз больше. При П -5 величина 6 s. 4; при П. 10 величина и 6, что свидетельствует об увеличении коэффициента использования оборудования в предлагаемом преобразователе. Формула изобретения Преобразователь кода из системы остаточных классов в полиадический код, содержащий входной регистр, входы которого соединены с входными шинами, дешифратор, пе вая группа выходов которого соединена со всеми входами блока памяти, кроме пepвoгo выходы которого соединены с первой группо входов блока модульных сумматоров, о т личаюшийся тем, что, с целью увеличения коэффициента использования оборудования, он дополнительно содержит блок управления и два блока элементов И, приче выходы входного регистра соединены с информационными входами первого блока эле- ментов И и выходными шинами, управляющий вход первого блока элементов И соединен с первым выходом блока управления, второй выход которого соединен с управляющим входом второго блока элементов И, выходы которого подключены кО всем входам входного регистра, кроме первого, и ко второй группе выходов дешифратора, информационные входы второго блока элементов И соединены с выходами блока модульных сумматоров, вторая группа входов которого подключена ко всем выходным шинам, кроме первой, все выходы первого блока элементов И, кроме первого, подключены к входам дешифратора, а первый выход первого блока элементов И соединен с первым входом блока памяти. Источники информации, принятые во внимание при экспертизеi 1. Авторское свидетельство № 407301, М.Кл. G 06 F5/O2 от 1971 г. 2. Авторское свидетельство № 328448, М.КлГ G06 F 5/02 от 1970.

Авторы

Даты

1976-08-25—Публикация

1974-11-20—Подача