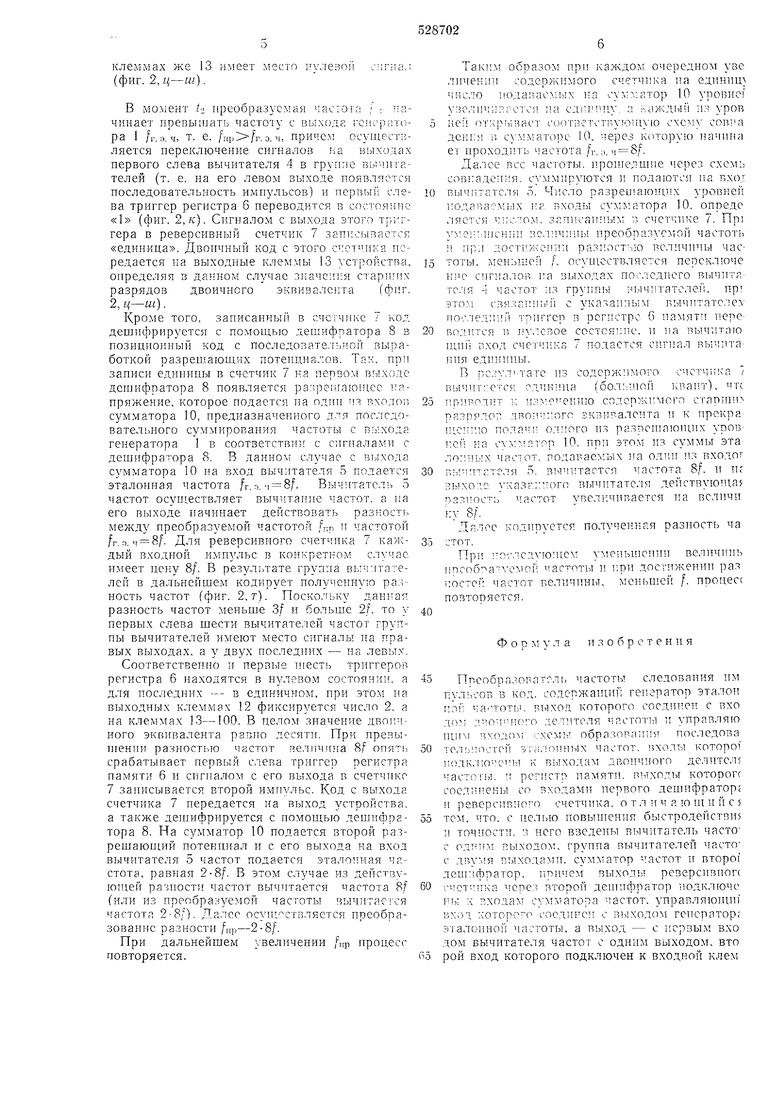

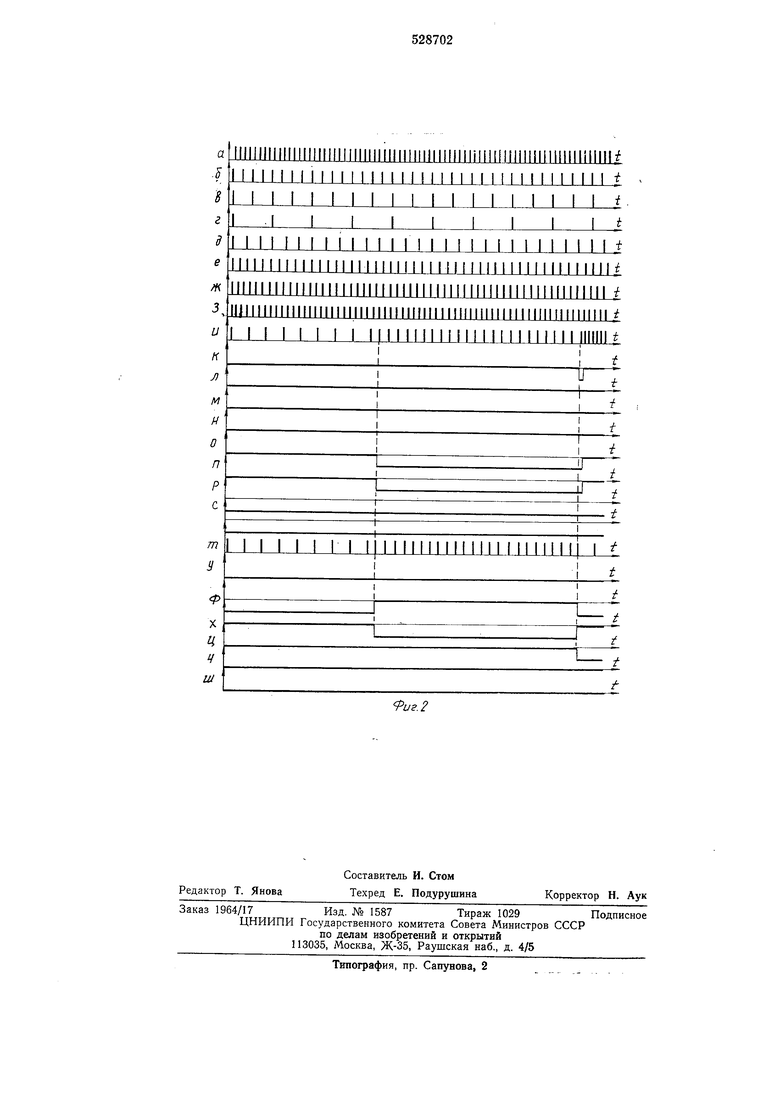

чидом, регистр 6 iia.u-i Ili, ровспсивпыи счетчик 7, второй дешифратор 8, первый дешифратор Э, сумматор 10 эталонных частот, клемму 11 юдачи преобразуемой частоты и выходные ллеммы 12 и 13, причем выход генератора 1 соединен с входом двоичного делителя 2 и управляющим входом схемы 3, входы которой лодключены к выходам делителя 2, выходь регистра памяти 6 соединены с входами иер:joro дешифратора 9 и реверсивного счетчика 7, выходы носледнего через второй дешифратор 8 подключены к входам сумматора 10, уиэавляюпи1Й вход которого соединен с выхо1, генератора 1, а выход-с нервым входом вычитателя 5, второй его вход подключен к клемме 11, а ,ыход соединен с первыми вхо;1,ами группы вь читателей 4 часто г с Д1;у;.;я выходами, вторые зходы которых подключены к выходам схемы 3, а выход -- к входам регистра памяти 6.

Преобразователь работас следуюни1л образом.

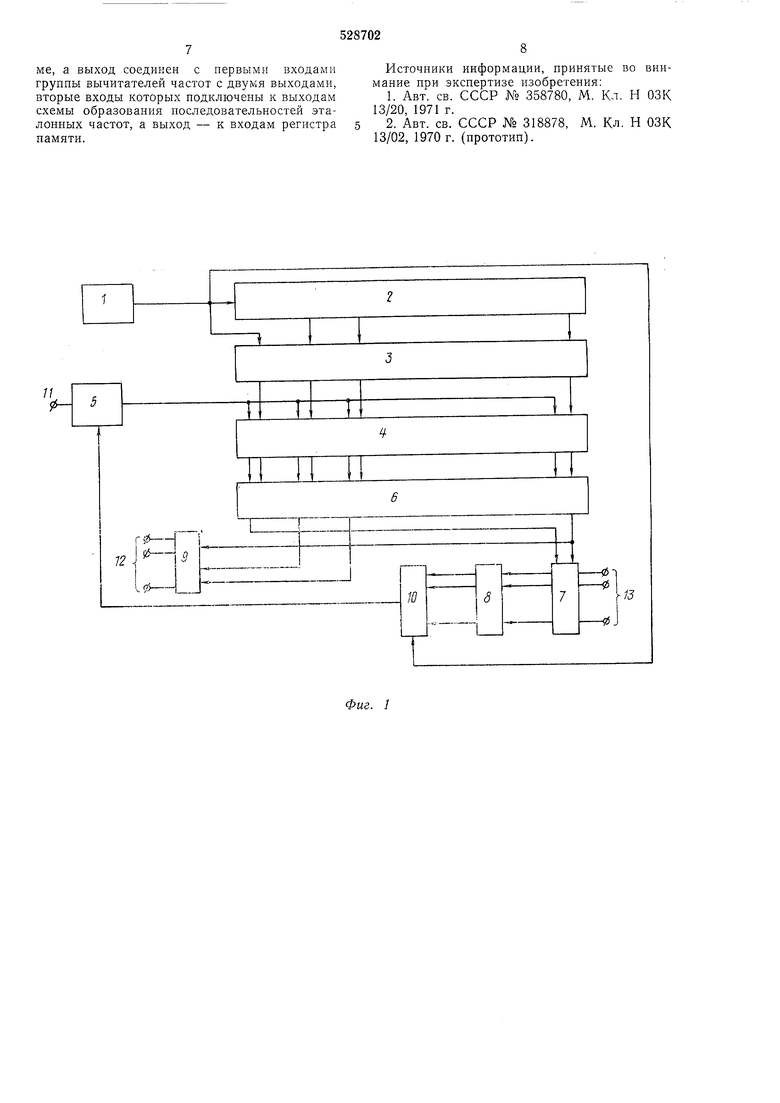

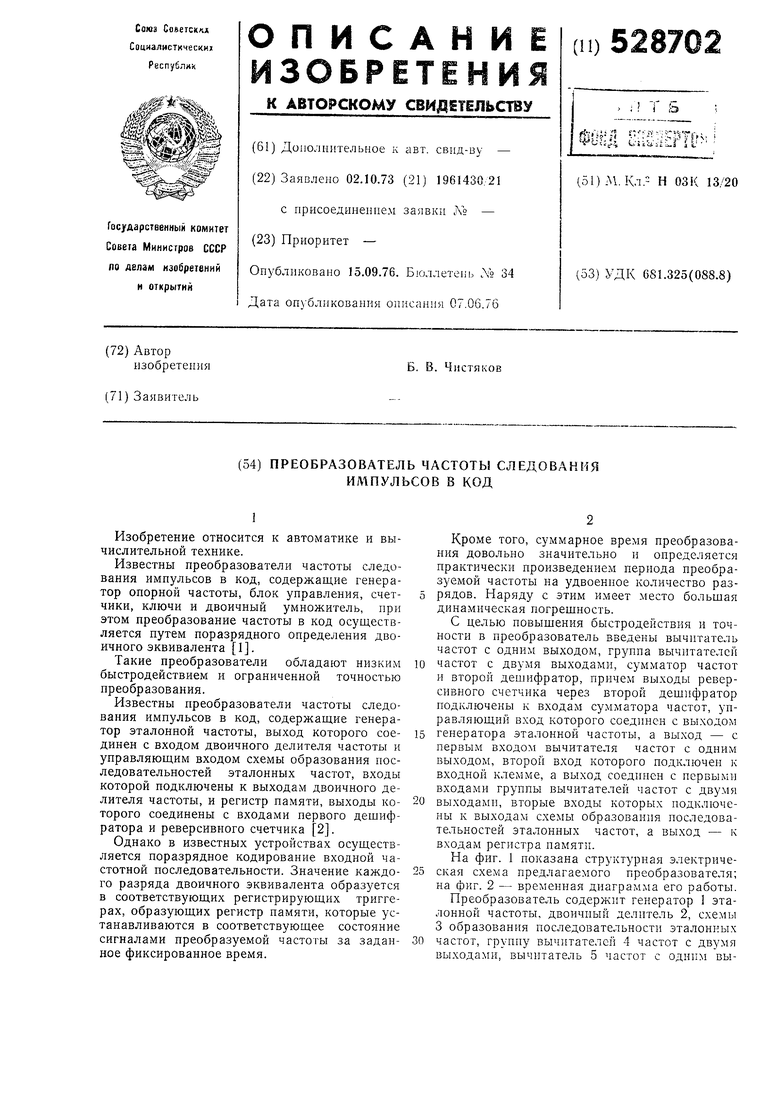

Сигналы с выхода гспер;:тора 1 эта лснио; част(ггы (ф-нг. 2,0.) нодаютс;-; на )д a..: noiO доли геля 2 частоты, где ерссч 1гьн аются

5 двоичном СИПКОШСННН. ,Ь; с

генератора 1 н с разрядных выходов jisO4ior;; делнлеля 2 (фнг. 2,с--с подаются ка iiX() схсУы 3, где образуется ря.л, импульснь;:-; носледовательностен с частотами 8/, 7/, 6, о/, 3/, 2/ н , где /--частота нмну,п.с)В :ia вяходс 1()след1н:то разряда делнте.ля, оирС.-еляюн ая велнчнну минимальною кванта н значение младшего разряда двинчного эквчзаленга. Сл-1гьа;1Ы с частотой 3f, 5Д G/ и 7/ нредета 5лсны на . 2, г-з. Ма врс:,1енной нредста1 лен случай нреобразоваиия частоты i; Н1естнразрядный двоичный код, нри этом три младших разряда двоичного эквивалента образуются ири исмощи групны вычнтателей чаСТОЛ, регистра 6 и ден1ифратора 9, а три старших - при иомонги счетчика 7,

Частотнвш последовательностн с выходов схемы 3 подаются соответственно на входы груины вычитателеГ 4, причем на уиравляюнип- вход каждого вв1читателя частот указанной группы подается своя последозательпость.

На другие входы всех вычитателе часток входянигч в группу вычиталеле; 4, подается частота следования импульсов с выхода вычитателя 5 частот (фнг. 2,т), которая представляет собой разность между преобразуемой частотой (фнг. 2,гг), подаваемой );а клемму 11, и эталонной частотой с выхода сумматора 10. Например, когда преобразуемая частота /пр меньше частоты с выхода генератора 1, частота с выхода вычитателя. 5 |KiBiia преобразуемой частоте.

Сигналы преобразуемой частоты с клеммы 11 через вычитатель 5 подаются одновременно на управляюгцие входы всех вычитателей частот, входящих в группу вычитателей 4. В завнснмости от соотношения частот иа входах каждого нз вычитателей имеет место носледова1СЛ)Н;;сть импульсов только на одном из дзух его выходов. Поскол1;ку частота слсдова) имнульсов эталонпой частоты на выходах схемы 3 слева направо уменьшается, то начиная с момента, когда

fig.;,

для вычитателей с индексом i+1, f-r 2 ... п, сн1иалы находятся на левых выходах и отсутствуют на их иравых выходах. Для вычитателей же с индексами i, i-l. i-2, ,,,1 имеет место частотная иоследовательность только на правых выходах,

В соответствии с налн1чнем импульсов на тех или ипых выходах вычитателей осуществляется устаиовка связанных с ними триггеров регнст|)а () намя.И в то или иное состояние, временной диаграмме рассмолрены несколько характерных случаев, характеризуюninx работу устройства. ZU) момента ti входная преобразуемая, частота /пр мепьп1е частоты снгн;1,:()1 с выхода roiepaiopa 1 эта.лонной частоты /;,.,, и лежит в пределах 3f -/rip -2/, гг .;/, скачком уве,1нчнвается, но меньнде /i.,,., и лежит в иределах

d ;омен1 1- входная часюта увеи станов1ггся бо;плне /г.:,, ч, нри

,чичи15ается разность /::|, - /г.;), ч на выхо5ТОМ образует.

дс вычигателя ;; часто с одним выходом

(ф1Н. 2, г), коюзая сжнг в нреде,лах

3/ /:;,,,,.

При /п), - /J..;. ч л.о момсп а J нне текущего- .значения частоты осун1ествл cji следуюнгим образом.

У зычитателя 5 частот на выходе имеет месго частота f-,,-,, (фиг. 2. и, т). У первых шести. с;1ева вь:чнтателе1 1 4 груины вычгггателсГ имеют место снгна,лы на иравых выходах, а у иоследпнх -- иа левых.

Первые слева шееть триггеров регистра 6 памяти находятся в нулевом состоянии, а два последних ----- в единично.1 (выходиые сигналы тзлнлсров представлены соответственно па фнг. 2, к-с). Сигиалы с выходов регистра 6 далее преобразуются в соот;5етствуюии1Й двоичный код ири помоии-1 ден1ифратора 9.

Таким об1)азом. для -;онкретного случая до момента /i на выходных клеммах 12 (где образуется младшая часть двоичного эквиваJieirra) имеет место сигнал, характеризующий число 2 р, двоичном нредставленн - (фиг. 2.i/--.v). На выходных клеммах 13, где образуется старнтая часть двоичного эквивалента, HiieeT место нулевой енгнал (фиг. 2, ц-ш), онределяемый нулев,ыми состояниями триггеров счетчика 7,

Далее, начиная с момента ч, у иервых четы)ех СоЛева вычитателей имеют меето сигналы на правых выходах, а у последних четырех - на левых, нри этом нервые елева четыре триггера регистра 6 на.ходятся в нулевом состоянии, а четыре последних - в единичном. На выхо.лных клеммах 12 фиксируется ч:осло 4 в двоичном коде (фиг. 2, у-х). На

клеммах же 13 имеет место iv;ie3oii oiirHa.i (фиг. 2, ц-ш.).

В момент ti преобразуемая часгога / : начинает превьииать частоту с выхода генератора 1 /г. э. ч, т. е. /г1,/г. э. ч, причем осуществляется переключение еигналов на выходах первого елева вычитателя 4 в группе выч1ггателей (т. е. на его левом выходе появляется последовательность импульсов) и первый слева триггер регистра 6 переводится в состояппс «1 (фиг. 2, к). Сигналом с выхода этого Tpi-rгера в реверсивный ечетчик 7 записывается «единица. Двоичный код е этого счет-пка передается на выходные клеммы 13 устройства, определяя в данном значения стартппх разрядов двоичного эквивалента (фиг. 2, ц-ш.

Кроме того, записанный в счетчике 7 код дешифрируется с помощью дешифратора 8 в позиционный код с последовате-льной выработкой разрещающих потенциалов. Так, прп записи е.п;иннп.ы в счетчик 7 на первом выходе денлифратора 8 появляется pa peniaioniee напряжение, которое подается па один пз входог сумматора 10, предназначенного для пос;1сдовательного еуммирования частоты с выхода генератора 1 в соответствии с сттгналами с дещифратора 8. В данном случае с вт тхода сумматора 10 па вход вычитателя 5 подается эталонная частота fr. г5. 4 8/. Вычитател-з 5 частот осуихествляет вычитание частот, а па его выходе начинает действовать размоет, между преобразуемой чаетотой ,Чф и частотой fr. Г). . Для реверсивного счетчика 7 каждый входной импульс в конкретном случае имеет цену 8/. В резул 1тате группа вычитателей в дальнейшем кодирует полл-ченную разность частот (фиг. 2, т). Поскольку данная разность частот меньше 3f и больше 2/, то у первых слева шести вычитателей частот группы вычитателей имеют место сигналы на правых выходах, а у двух последних - на левых.

Соответственно и первые niecTb триггеров регистра 6 находятся в нулевом состоянии, а для иоследних - в единичном, при этом на выходных клеммах 12 фиксируетея число 2, а на клеммах 13-100. В целом значение двоичного эквивалента равно десяти. При превышении разностью частот вел11чи5га 8f опять срабатывает первый слева триггер регистра памяти 6 и сигналом с его выхода в счетчике 7 запиеывается второй импульс. Код с выхода счетчика 7 нередается на выход устройства. а также ден1ифрируетея с помощью дешифратора 8. На сумматор 10 подается второй разрешаюнцтй потенпиал и е его выхода на вход вычитателя 5 частот подается эталонная частота, равная 2-8/. В этом случае из действуюн1ей разности частот вычитается частота 8f (или из нреобразуемой частоты вычитается частота 2-8/). Далее осутт;-: ствляется преобразование разности f,,p-2-8/.

При дальнейшем увеличении Дф процесс повторяется.

аким ооразом ири каждом очередном уве лнчении содержимого ечетч1п а на е.диниц число 1 ода; асмых иа сумматор 10 уровнеГ узелич;;: ;-отся ia едщмцл, а -;ажды11 из уров Hei г)ткр1 ;вает С1)от; етстнуюп1ую coBia деиия ;; сулматоре 10, через которую начина ет прохо.дить частота /г. :i. .

Далее вес частоты. проитедшие через схемь сов :адеп; я. суммируются и подаются па вхо.г

выч1 татсля о. Число разрешающих уровней подаваемых на входы cy : ;aтopa 10. опреде ляетс 4i;c.0i. записаиуым з счетчике 7. Пр1 :e; иlcиIiи величины преобразуемой частоть и гтри достижении разностью всличпны чаетоты, меньшей f, осуп1ествляется переключе ние сигналов иа выходах последиего вычитателя -1 частот из группы тчлчптатолеи, пр этом сзязаииьп с лказанным вычптателеу

водится в нулевое состояние, и на вычитаю nuiii вход счетчика 7 подается сипкал вычитапня едннии.ы.

В резул-тате из содержимого счстчнка вычит;:е -ся единица (больнюй кпапт), чтс

приводит к из е1ению еодержимого стапищ разрядов дво;г.:;ого зкзипа,тснта и к прекраиенпю одлтого из разреи аюи1,11х ypoisней на сУлГлатор 10. при этом из суммы эталонных частот, подаваемых на один нз входо

пьпппателя 5. вычитается частота 8f. н нг

выходе каза;:ого вьтчитателя действуюца

пззиость частот увеличивается Tia величи

ну 8/.

Далее кодируется полученная разность ча

стот.

При г-ослсдую;цем уменл июнии велттчинь ипеоб: а емой и. г;ри достижении раз иостей частот величины, меньп ей /. процесс повторяется.

Формула изобретения

Преобразователь частоты следования нм ПУЛЬСОВ в код. содержаищи генератор эталон нзй чатоть1, выход которого сосдит ен с вхо ЮМ ОГЧЮУо .делителя частоты и управляю Hui-j nx(vioN -.хемь образова;1ия последова

(1стей эталонных частот, входы которой 1К5дклю еиы к выходам двончного делител частогы. и pcrHeTn памяти, выхо.ды которогс соединены со входами первого дешифратор; и реверсивно о счетчнка, о т лнч аю ши и сs

тем, что, с п,елью повьпиения быетродейетглп и точности. , него введены вычитатель часто с одпнм выходом, группа вычитателей часто с .двумя выхо.дами. сумматор частот и второ деишфратор, нпичем выходы реверсивпогс

через второй деитифратор нодключе ньт X входам c м laтopa частот, управляюпии вх;)д которого соед;1рен с выходсш генератор; эталонной частоты, а выход - с иервым вхо дом вычитателя частот с одним выходом, вто

рой вход которого подключен к входной клем ме, а выход соединен с первыми входами группы вычитателей частот с двумя выходами, вторые входы которых подключены к выходам схемы образования последовательностей эталонных частот, а выход - к входам регистра памяти. Источники информации, принятые во внимание при экспертизе изобретения: 1.Авт. св. СССР N° 358780, М. Кл. Н ОЗК 13/20, 1971 г. 2.Авт. св. СССР № 318878, М. Кл. Н ОЗК 13/02, 1970г. (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь цифрового кода в частоту следования импульсов | 1976 |

|

SU738158A1 |

| Преобразователь частоты следования импульсов в код | 1974 |

|

SU516190A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ЭТАЛОННОЙ КАРТЫ МЕСТНОСТИ ДЛЯ НАВИГАЦИОННЫХ СИСТЕМ | 1992 |

|

RU2022355C1 |

| Многоканальное устройство тестового контроля логических узлов | 1990 |

|

SU1837295A1 |

| Устройство задержки импульсов | 1980 |

|

SU917326A1 |

| Многоканальная цифровая телеметрическая система | 1989 |

|

SU1672498A2 |

| Устройство для идентификации характеристик четырехполюсников | 1983 |

|

SU1188676A1 |

| Устройство для распознавания контуров изображений | 1983 |

|

SU1156103A1 |

| Многоканальное устройство для обработки информации датчиков с частотным выходом | 1984 |

|

SU1196892A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ ПЕРИОДИЧЕСКИХ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ И ОЦЕНКИ ИХ ПЕРИОДА | 1990 |

|

RU2033617C1 |

Г

.J

10-II

10

13

Фиг. 1

1

Illllllllllll

lUIIIIIIIIIIIIII111111М111ПНIIllllllllllll/

llllllllllll

X

Ч

Ч

ш

i f f

LUJ-LULJ-LI I I I I . Illllllll I IliHIIIIHIIIIIIIIIIL

1

I I I I Illllll i

t

П

/

X f

L

J t

/ /

j;;

f

Авторы

Даты

1976-09-15—Публикация

1973-10-02—Подача