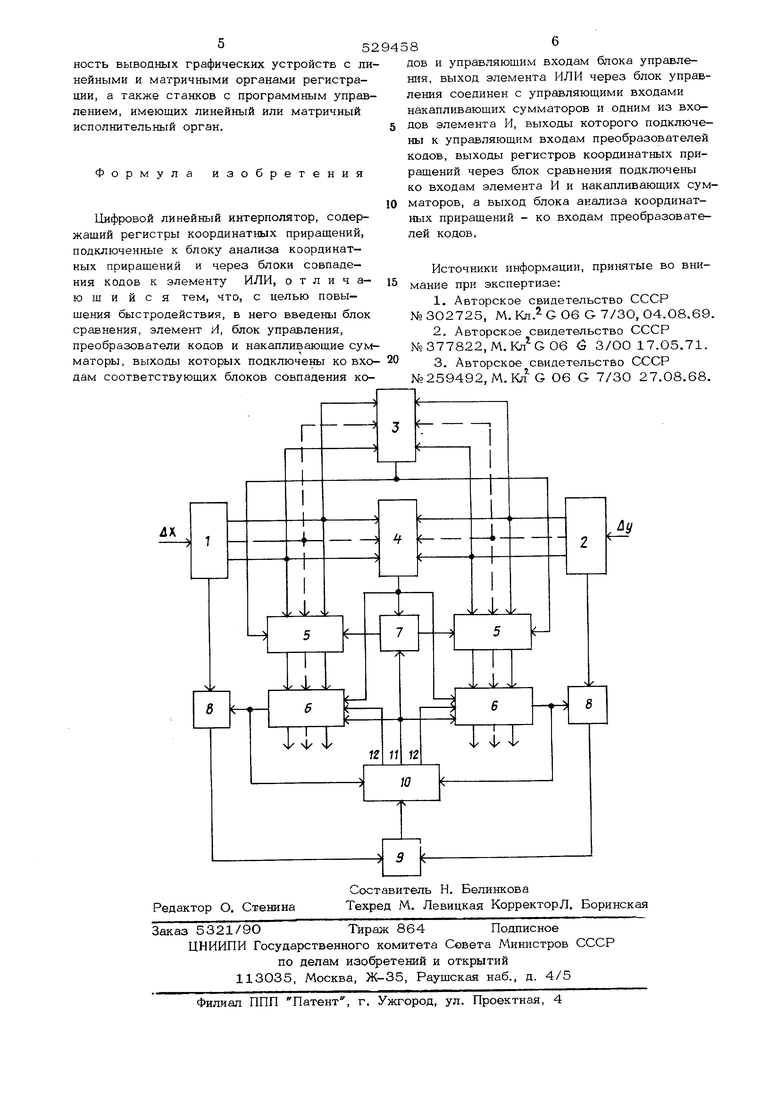

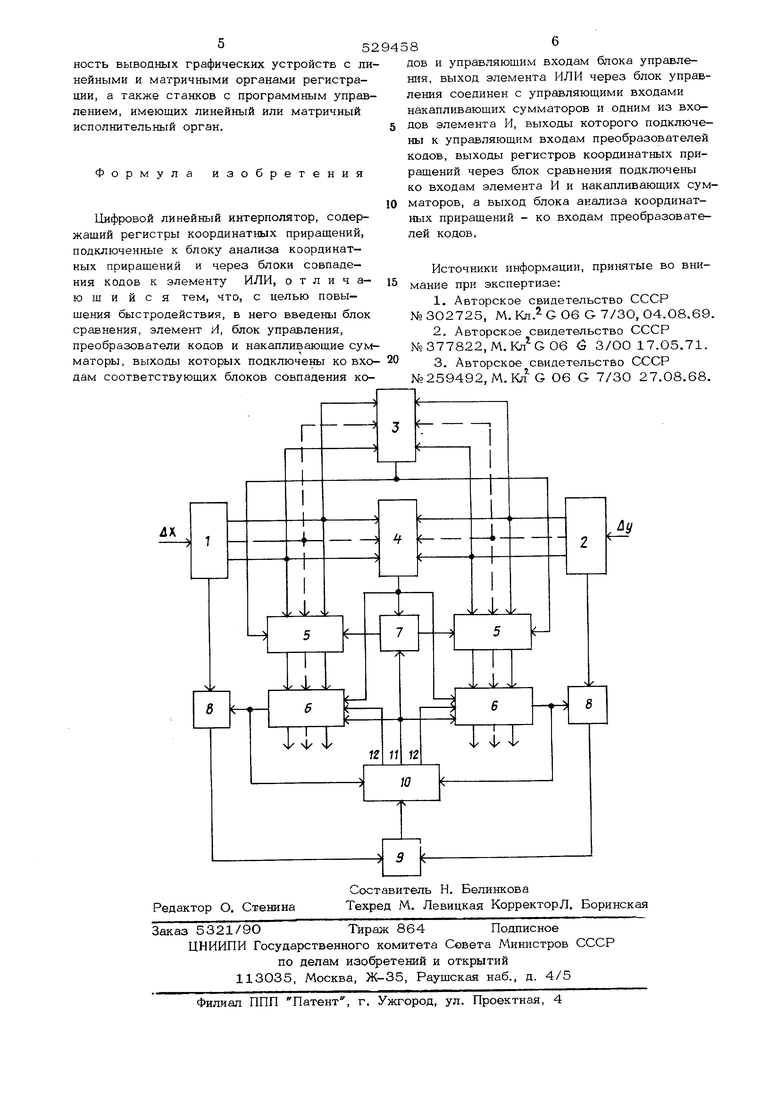

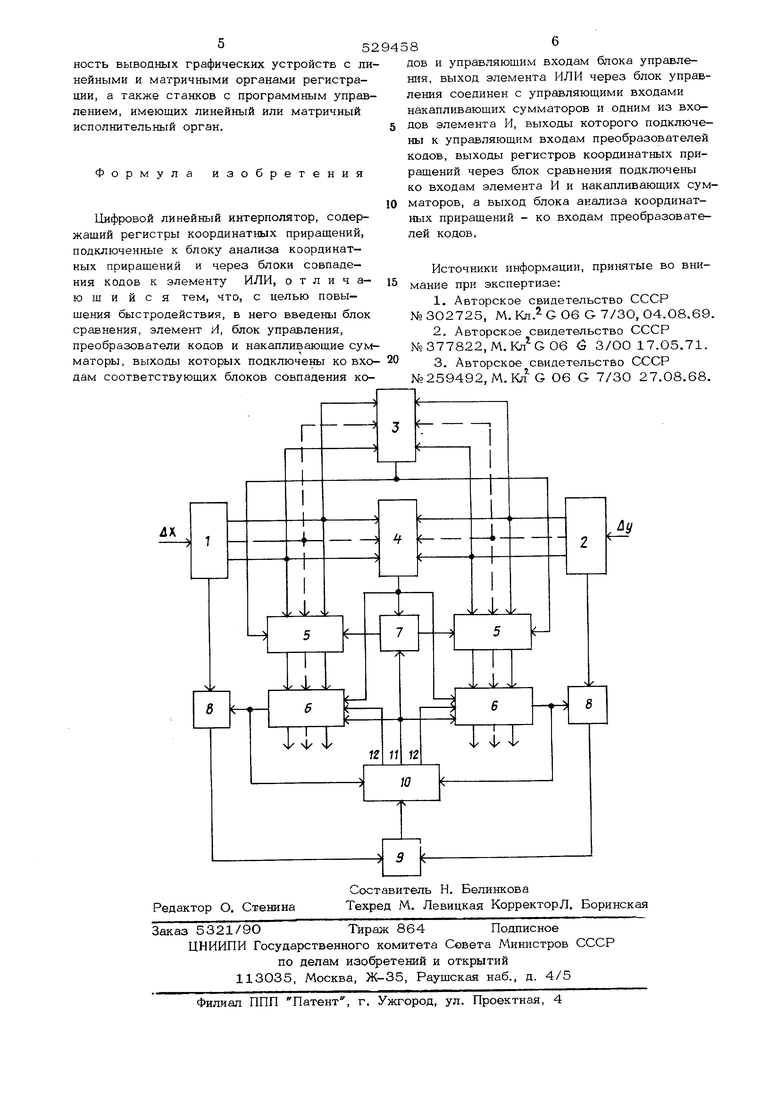

Изобретение относится к области автоматики и вычислительной техники и может использоваться в выходных графических устройствах с линейными и матричными ор ганами регистрации, а также в станках с программным управлением, использующих линейные и матричные исполнительные органы. Известен цифровой линейный интерполятор, содержащий генератор, устройство изменения частоты по двум координатам, выполненное на импульсно-потенциальных пре образователях, соединенных с общим делителем частоты, вьшолненным на триггерах, триггеры, инверторы и вентили f Ij. Однако это устройство имеет низкое йлстродей ствие. Известен также линейный интерполятор, содержащий собирательную схему, последовательно соединенные регистр, вентили, сум матор и схему анализа знака, один из выходов которой соединен с управляющими вх дами вентилей 2 Он также обладает недостаточным быстродействием. Наиболее близким по техническому решению к предлагаемому интерполятору является цифровой линейный интерполятйр, содержащий регистры координатных приращений, подключенные к блоку анализа координатных приращений и через блоки совпадения кодов - к элементу ИЛИ з. Этот интерполятор обладает низким быстродействием из-за отсутствия взаимосвязи между временем интерполирования и соотнощением координатных приращений. Цель изобретения - повысить быстродействие -интерполятора. Это достигается тем, что в интерполятор введены блок сравнения, элемент И, блок управления, преобразователи кодов и накапливающие сумматоры, выходы которых подключены ко входам соответствующих блоков совпадения кодов и управляющим входам блока управления, выход элемента ИЛИ через блок управления соединен с управляющими входами накапливающих сумматоров и одним из входов элемента И, выходы которого подключены к управляющим входам преобразователей кодов, выходы рег истров координатных приращений через блок сравнения подключены ко входам элемента И и на капливающих сумматоров, а выход блока ан лиза координатных приращений - ко входам преобразователей кодов. На чертеже представлена структурная электрическая схема устройства. Предлагаемый интерполятор содержит ре гистры 1 и 2 координатных приращений, блок 3 анализа координатных приращений, блок сравнения 4, преобразователи 5 кодов накапливающие сумматоры б, элемент И 7, блоки 8 совпадения кодов, элемент ИЛИ 9 и блок управления 10с выходами 11 и 12 Интерполятор работает следующим образом. В регистры 1 и 2 координатных приращений записываются приращения ДХ и Л У. Потенциалы с обоих регистров подаются на вход блока 3 анализа координатных приращений. В случае если старщие разряды кодов приращений ЛХ и л У нулевые, т.е. величины приращений относительно малы, блок 3 анализа координатных приращений осуществляет умножение на 2 приращений Л.Х и АУ, используя преобразователи кодов 5, причем координатные приращения предварительно разделены на 2 в тех же преобразователях кодов 5. В случае если и следующие разряды кодов приращений ДХ и лУ нулевые, то вновь осуществляется ум ножение на 2 и т.д. Таким образом осуществляется выполнение следующих операций: дх-г , чг; I где h - максимальное число разрядов в дво ичном коде приращений дХ и Л У; ( - количество общих нулевых старщих разрядов в кодах приращений А X и Л У до первого нулевого разряда. Потенциалы с выходов регистров 1 и 2 координатных приращений подаются также на вход блока сравнения 4, осуществляющего сравнение приращений ZS X и /N У. На выходе блока сравнения 4 образуется двоичный код 2 , величина которого являет ся ближайщей меньшей или равной величине отношения больщего приращения к меньщему л X ДХ для Л X Л у 2 ду для Д X Д у Полученное значение 2 определяет пер вый шаг интерполирования и управляет работой преобразователей кодов 5, в которых по сигналу с выхода 11 блока управления 10 осуществляется умножение величии на первый щаг интерполирования 2 , т.е. осуществляется операция.З. -2 Полученные двоичные коды записываются в накапливающие сумматоры 6. По сигналу с выхода 12 блока управления 1О осуществляется запись двоичных кодов йХ-г U В накаплива п2 2 ющие сумматоры 6 (без сдвига в преобразова1елях кодов 5), в которых образуются частичные суммы (24,) 2 Затем блок управления 10 вновь вырабатывает сигнал на выходе 12 и т.д.В результате этих операций в накапливающих сумматорах 6 образуются суммы К (24u...-fl)uZy -(г ./...../;. В блоке управления фиксируются переносы из разрядов после запятой в разряды до запятой (из дробных в целые) для меньшего из приращений. По каждому переносу осуществляется выдача целых разрядов частичных сумм из накапливающих сумматоров 6 на выход интерпо.тятора и затем осуществляется сброс в О целых разрядов накапливающего сумматора 6 для больщего из приращений. Блок управления 10 вновь вырабатывает сигнал на выходе 11, затем серию сигналов на выходе 12 до следующего переноса (получаются частичные суммы Х., и УЗ ). Сигнал конец интерполирования вырабатывается при выполнении одного из равенств 1Х - .. . ДЛЯЛХ- Дх лу 1 5:у|+ -. ЛХ ду . Этот сигнал вырабатывается блоками 8 совпадения кодов, элементом ИЛИ 9 и блоком управления 10. Число тактов интерполирования в пределе равно меньшему из координатных приращений Применение цифрового линейного интерполятора с взаимосвязью между временем интерполирования и соотношением координатных приращений увеличивает производи:тель 5294ность выводных графических устройств с линейными и матричными органами регистрации, а также станков с программным управлением, имеющих линейный или матричный исполнительный орган.5 Формула изобретения Цифровой линейный интерполятор, содержащий регистры координатных приращений, подключенные к блоку анализа координатных приращений и через блоки совпадения кодов к элементу ИЛИ, о т л и ч а- 15 ю щ и и с я тем, что, с целью повышения быстродействия, в него введены блок сравнения, элемент И, блок управления, преобразователи кодов и накапливающие сумматоры, выходы которых подключены ко вхо- 20 дам соответствующих блоков совпадения ко8одов и управляющим входам блока управлеш я, выход элемента ИЛИ через блок управления соединен с управляющими входами накапливающих сумматоров и одним из вхоДов элемента И, выходы которого подключены к управляющим входам преобразователей кодов, выходы регистров координатных приращений через блок сравнения подключены ко входам элемента И и накапливающих сумматоров, а выход блока анализа координатных приращений - ко входам преобразователей кодов. Источники информации, принятые во внимание при экспертизе: 1.Авторское свидетельство СССР № 302725, М. Кл. G Об G 7/ЗО, О4.О8.69. 2.Авторское свидетельство СССР №377822, М. 06 3 3/00 17.05.71. 3.Авторское свидетельство СССР №259492, M.Krfc Об G 7/30 27.08.68.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой линейный интерполятор | 1976 |

|

SU579599A1 |

| Цифровой линейный интерполятор | 1986 |

|

SU1310779A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Цифровой линейный интерполятор | 1988 |

|

SU1624406A1 |

| Линейно-круговой интерполятор | 1977 |

|

SU741234A1 |

| Цифровой линейный интерполятор | 1977 |

|

SU682923A1 |

| Линейный интерполятор | 1979 |

|

SU888073A1 |

| Линейный интерполятор | 1991 |

|

SU1809421A1 |

| Линейный интерполятор | 1975 |

|

SU634236A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

Авторы

Даты

1976-09-25—Публикация

1975-03-13—Подача