1

Изобретение относится к цифровым вычислительным машинам, в частности к сумматорам, и может быть использовано при построении арифметических устройств.

Известны последовательные сумматоры, построенные на основе одноразрядных комбинационных сумматоров, fl, 2, В извест ны.с сумматорах используется два способа передачи цифры переноса из одного такта в другой: с задержкой переноса и с запо- минанием переноса. Недостатком таких устройств является большое количество оборудования.

Ближайшим аналогом изобретения является последовательный сумматор, содержа- щий узел образования суммы, выполненный на пяти элементах И-НЕ, и узел образования и хранения сигнала переноса, выполненный на триггере с раздельными входами и двух элементах И-НЕ, причем к первому и второму входам четырех элементов И-НЕ узла oбpaзoвaIiия суммы и элементов И-НЕ узла образования и хранения сигнала переноса подключены шины прямого и инверсного значений двух слагаемых, к

третьим входам первого и второго элементов И-НЕ уапа образования суммы подключен нулевой выход триггера узла образования и хранения сигнала переноса, а выходы четырех элементов И-НЕ узла образования суммы подключены ко входам пятого элемента И-НЕ уала образования суммы, выход которого является выходом сумматора, к третьим входам элементов И-НЕ узла образования и хранения сигнала переноса подключена тактовая шина, а выходы их соединены соответственно с нулевым и единичным входами триггера узла образования и хранения сигнала переноса Гз.

В таком сумматоре сигнал переноса поступает на входы узла образования переноса сразу же по окончании переходных процессов в триггере узла образования и хранения сигнала переноса, что может вызвать ненадежную работу сумматора.

Целью изобретения является повышение надежности работы сумматора,

С этой целью узел образования и хранения сигнала переноса содержит третий элемент И-НЕ, первый вход которого соеда-

нен с нулевым выходом триггера, второй вход - с выходом первого элемента И-НЕ ysfia образования и хранения сигнала переноса, а выход - с четвертым входом этого элемента и с третьими входами третьего и четвертого элементов И-НЕ узла образования суммы, выход четвертого элемента И-НЕ узла образования суммы соединен с четвертым входом, а четвертый вход - с выходом второго элемента И-НЕ уапа об- разовш ия и хранения сигнала переноса.

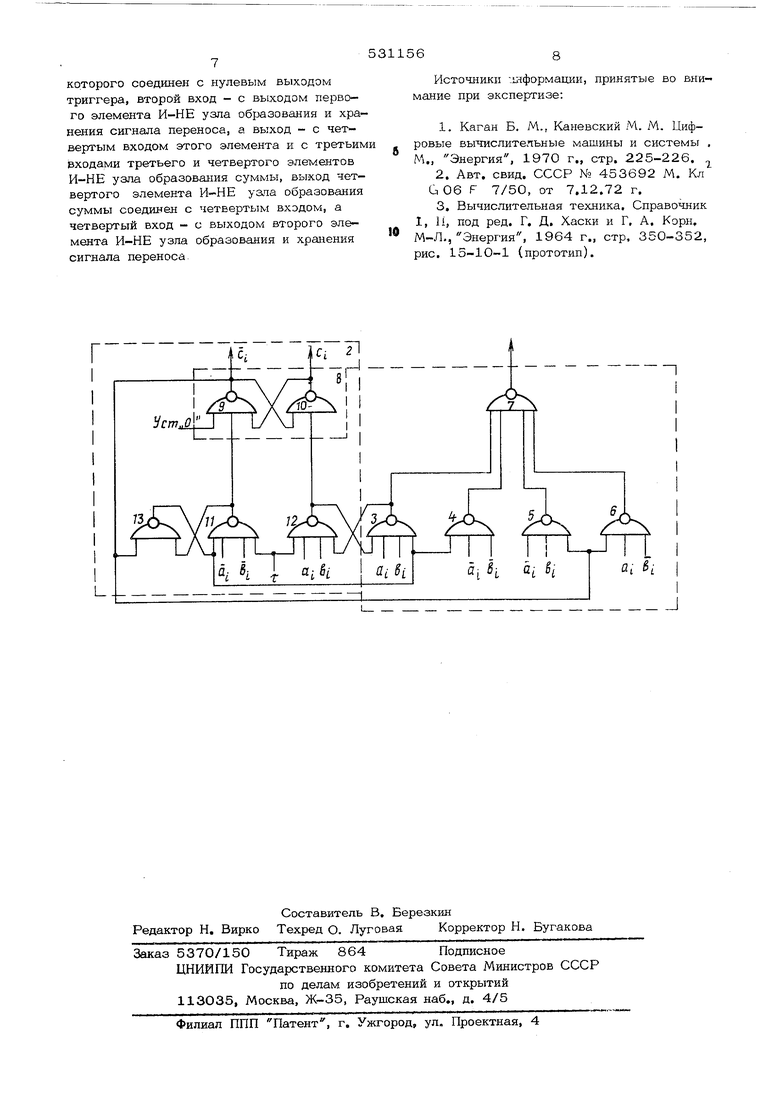

На чертеже представлена схема последовательного сумматора, содержащего узел 1 образования суммы и узел 2 образования и хранения сигнала переноса. Узел 1 состоит из элементов 3-7, причем выход элемента И-НЕ 7 является выходом сумматора на котором последовательно формируется сигнал значения суммы 5- каждого разряда Узел 2 состоит из триггера с раздельными входами 8, образованного элементами 9 и 10, и элементов И-НЕ 11. 12 и 13. К первому и второму входам элементов 3, 4, 5, 6, 11 и 12 подключены шины прямого и инверсного значений двух слагаемых, выходы элементов 3, 4, 5 и 6 подключены ко входам элемента 7, выходы элементов 11 и 12 подключены соответственно к нулевому и единичному входам триггера, нулевой выход которог о подключен к третьим входам элементов 5 и 6 и к первому входу элемента 13, ко второму входу которого подключен выход элемента 11, и выход его соединен с третьими входами элементов 3, 4 и 11, К третьему входу элемента 12 подключен выход элемента 3, а выход его соединен с четвертым входом элемента 3, К четвертым входам элементов 11 и 12 подключена тактовая шина

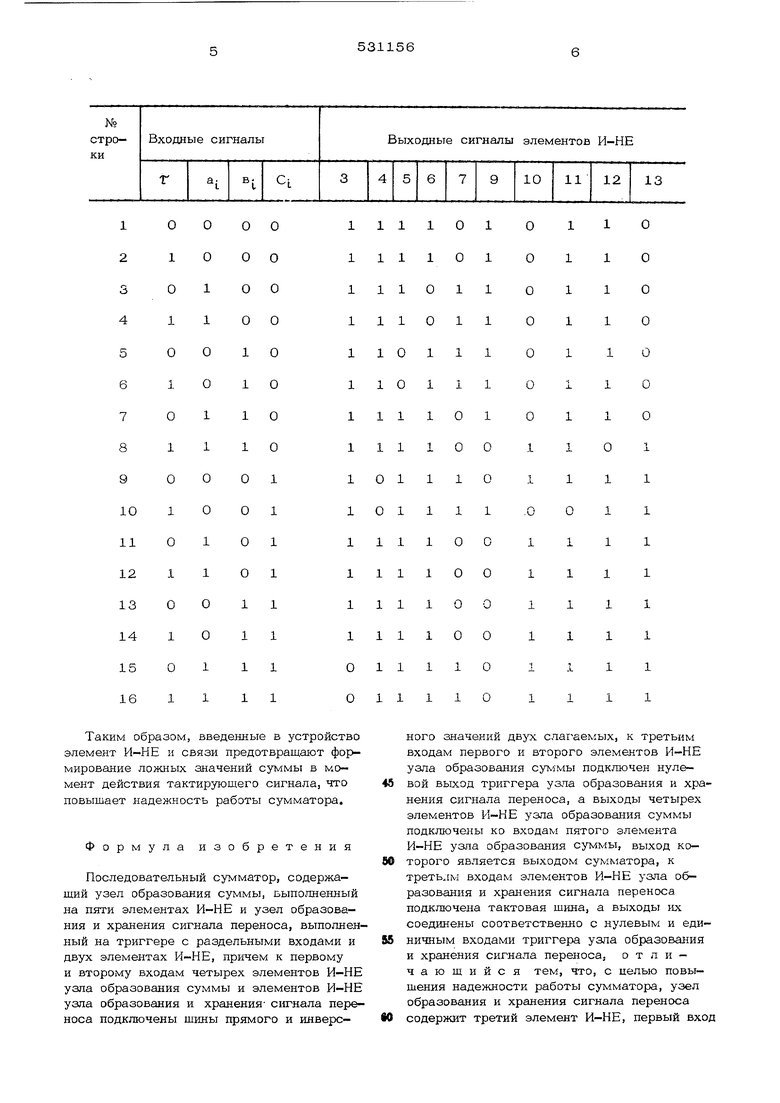

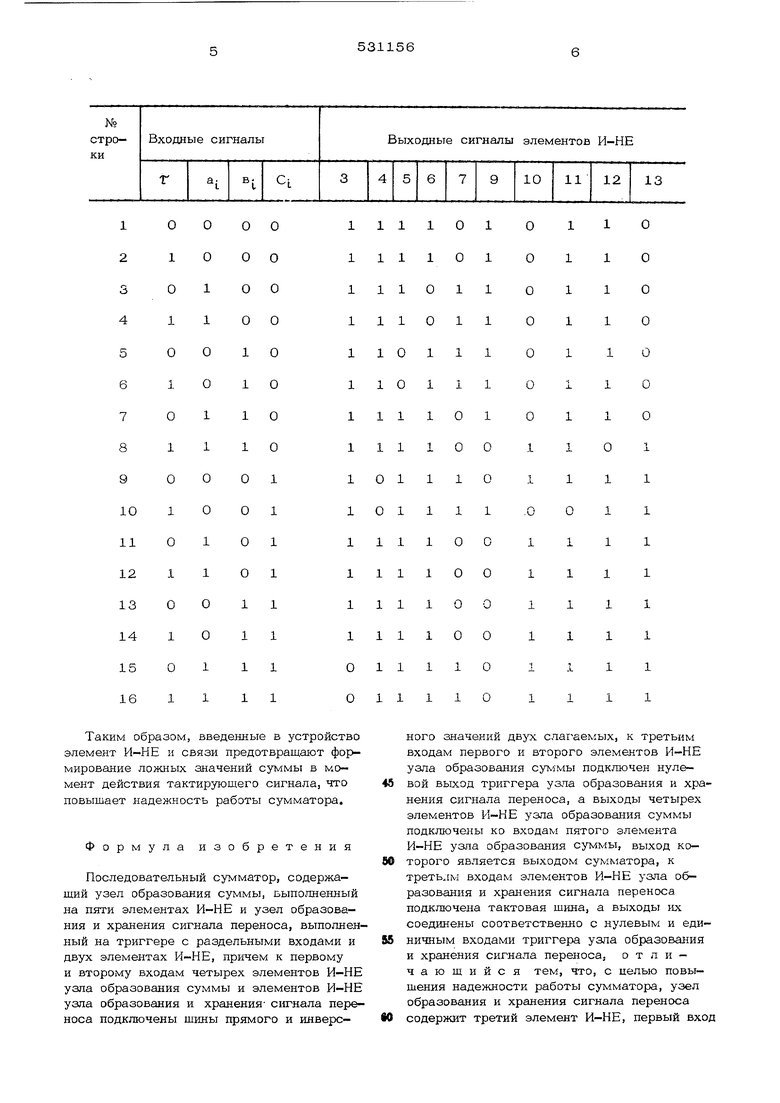

В начальный момент времени триггер узла образования и хранения сигнала переноса установлен в нулевое состояние, В этом случае на выходе элемента 10 - логический О, т.е. отсутствует сигнал переноса, на выходе элемента 9 - логическая 1, т, е. имеется сигнал инверсии переноса. Поркольку тактовый импульс отсутствует (равен логическому О), то на выходах элементов 11 и 12 - логические 1, следовательно, значение сигнала на выходе элемента 13 совпадает со значением сигнала на выходе элемента 10 и равно Cj , Суммирование входных сигналов и сигнала переноса производится сумматором в соответствии С таблицей истинности.

Значения входного сигнала С; в каждой строке таблицы указаны на тот момент времени, когда значения выходных сигналов элементов 3-8, 9-13 еще не изменились под действием значений входных сигналов данной конкретной строки таблицы. Так, например, в восьмой строке значение С равно логическому О, а значение выхода элемента 10 равно логической 1. Это означает, что С равно логическому О в начальный момент времени, а как только поступит импульс (логическая 1) Т на тактовую шину, то по окончании переходных процессов на выходе элемента 10 установится логическая 1, т, е, фактически и сигнал С{ станет равным логической 1, хотя в столбце С стоит О, показывая, что это значение было до начала поступления сигнала Т . Значения выходов элементов 3-9-13 указаны на тот момент времениз когда переходные процессы закончились, после подачи соответствующих входных сигналов.

Таким образом, введенные в устройство элемент И-НЕ и связи предотвращают формирование ложных значений суммы в момент действия тактирующего сигнала, что повышает надежность работы сумматора.

Формула изобретения

Последовательный сумматор, содержащий узел образования суммы, выполненный на пяти элементах И-НЕ и узел образования и хранения сигнала переноса, выполненный на триггере с раздельными входами и двух элементах И-НЕ, причем к первому и второму входам четырех элементов И-НЕ узла образования суммы и элементов И-НЕ узла образования и хранения- сигнала переноса подключены шины прямого и инверсного значений двух слагаемых, к третьим входам первого и второго элементов И-НЕ узла образования суммы подключен нуле-

вой выход триггера узла образования и хранения сигнала переноса, а выходы четырех элементов И-НЕ узла образования суммы подключены ко входам пятого элемента И-НЕ узла образования суммы, выход которого является выходом сумматора, к третьлм входам элементов И-НЕ узла образования и хранения сигнала переноса подключена тактовая щина, а выходы их соединены соответственно с нулевым и едияичным входами триггера уапа образования и хранения сигнала переноса, отличающийся тем, что, с целью повышения надежности работы сумматора, узел образования и хранения сигнала переноса

содержит третий элемент И-НЕ, первый вход

которого соединен с нулевым выходом триггера, второй вход - с выходом первого элемента И-НЕ узла образования и хранения сигнала переноса, а выход - с четвертым входом этого элемента и с третьим входами третьего и четвертого элету ентов И-НЕ узла образования суммы, выход четвертого элемента И-«НЕ уача образования суммы соединен с четвертым вхэдом, а четвертый вход - с выходом второго элемента И-НЕ узла образования и хранения сигнала переноса

Источники -Шформации, принятые во внимание при экспертизе:

1. Каган Б, М., Каневский М. М. Цифровые вычислительные машины и системы , М., Энергия, 1970 г., стр. 225-226.

2.Авт. свид. СССР № 453692 М. Кл G 06 F 7/50, от 7.12.72 г.

3.Вычислительная техника. Справочник 1, И, под ред. Г. Д. Хаски и Г, А. Корн, М-Л., Энергия, 1964 г., стр. 350-352, рис. 15-10-1 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| НАКАПЛИВАЮЩИЙ ДЕСЯТИЧНЫЙ СУММАТОР | 1966 |

|

SU224164A1 |

| Фазоимпульсный сумматор | 1980 |

|

SU885996A1 |

| Цифровой интерполяционный фильтр | 1990 |

|

SU1728962A1 |

| Последовательное множительное устройство | 1985 |

|

SU1307455A1 |

| Десятичный сумматор | 1973 |

|

SU491947A1 |

| Сумматор | 1974 |

|

SU541173A2 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| Комбинационный сумматор | 1985 |

|

SU1310808A1 |

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

Авторы

Даты

1976-10-05—Публикация

1973-06-15—Подача