Изобретен-ие относится к вычислительной технике и может быть использовано для аппаратурной реализации вычисления функций синуса и косинуса в циф 5овых вычислительных машинах и специализированных вычислителях .

Известно устройство для определения функций синуса и косинуса, содержащее блок памяти, блоки умножения , дешифратор и регистры синуса и косинуса f.

Недостатком известного устройства является накопление ошибки с увеличением значения аргумента.

Наиболее близким техническим решением к изобретению является устройство, содержащее блок памяти, дешифратор, регистры синуса и косинуса, делитель аргумента, блок сложения, блок вычитания, блок выборки информации, счетчик остатка, эле- , мент задержки, блок формирования зна|ка функции, коммутаторы, триггер и генератор итераций .2 .

Недостатком этого устройства является то, что функции коммутации опорных значений синуса и косинуса и изменения направления интегрирования выполняются коммутаторсцли, включенными в схему интегрирования. Это приводит к необходимости делать коммутаторы излишне громоздкими и, кроме того, потребует дополнительной коммутации при считывании вычисленных значений синуса и косинуса, поскольку они меняют местоположение в регистрах синуса и косинуса в зависимости от значения аргумента.

10

Цель изобретения - упрощение устройства.

Поставленная цель достигается тем, что устройство, содержащее де15литель аргумента, два коммутатора, счетчик остатка, элемент задержки, деишфратор, триггер, генератор импульсов, блок адресации, блок памяти, первый блок вычитания, первый

20 блок сложения, регистр знака, регистр косинуса и регистр синуса, причем вход аргумента устройства соединен с входом элемента задержки и информационным входом делителя аргумен25та, управляющий вход и выход младших разрядов которого соединены соответственно с входом делителя аргумента устройства и первым информационным входом первого коммутатора,

30 выход старших разрядов делителя

соединен с входом регистра знака, выход элемента задержки - с первым входом триггера, второй вход которого соединен через дешифратор с выходом счетчика остатка, вход вычитания которого соединен с выходом генератора импульсов и управляющими входами регистра синуса, первых блока вычитания и сложения и регистра косинуса, первые выходы регистров синуса и косинуса соединены соответственно с первыми входами первых блоков сложения и вычитания, вторые входы которых соединены соответственно со вторыми выходами регистра косинуса и регистра синуса, вход генератора импульсов соединен с выходом триггера, выход блока адресации с Входом блока памяти, содержит второй блок вычитания и второй блок сложения, выход которого соединен с входом блока адресации и управляющим входом второго коммутатора, информационный вход которого соединен с выходом блока памяти, первый и второй выходы второго коммутатора соединены соответственно с установочными входами регистра косинуса и регистра синуса, информационные входы которых соединены соответственно с выходами первого блока вычитания и первого блока сложения, вход второго блока сложения соединен с выходом старцгих разрядов делителя аргумента, выход младших разрядов соединен с первым входом второго блока вычитания, второй вход и выход которого соединены соответственно с входом делителя устройства и вторым информационнЕзМ входом первого коммутатора, выход и управляющий вход которого соединены соответственно с установочным входом счетчика остатка и выходом старших разрядов делителя аргумента.

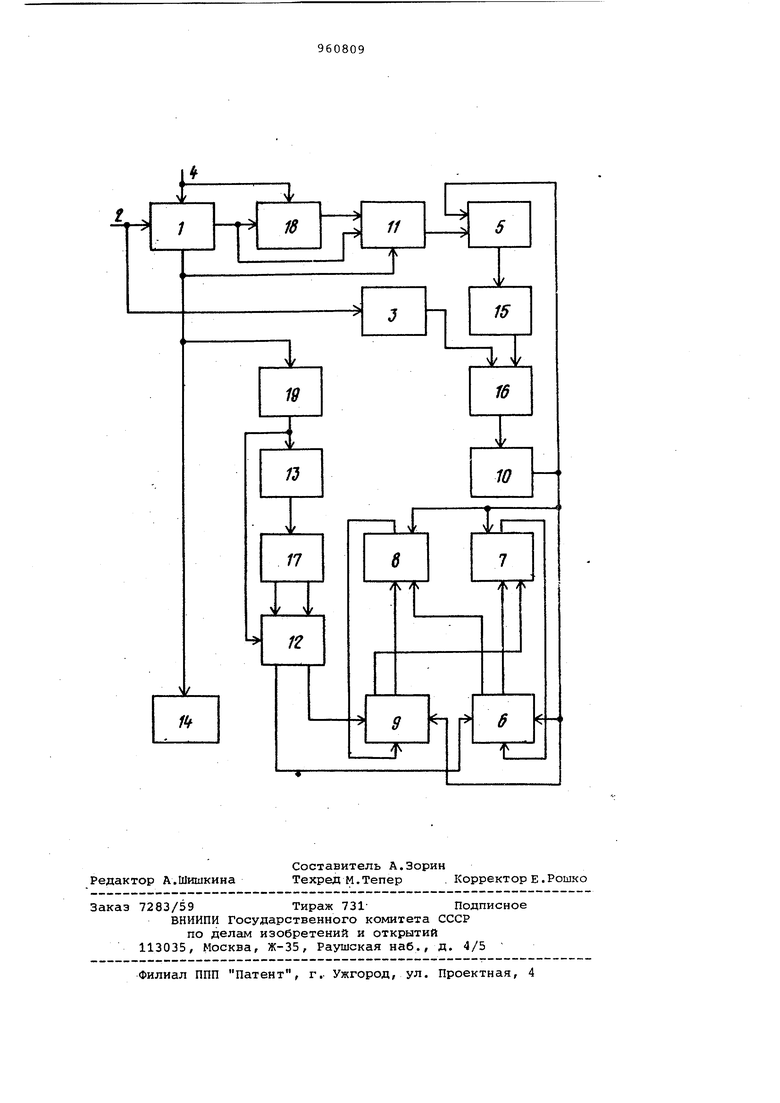

На чертеже приведена функциональная схема устройства.

Устройство содержит делитель 1 аргумента, вход 2 аргумента, элемен 3 задержки, вход 4 устройства для ввода делителя, счетчик 5 остатка, регистр 6 синуса, блок 7 сложения, блок 8 вычитания, регистр 9 косинуса, генератор 10 импульсов, коммутаторы 11 и 12, блок 13 адресации, регистр 14 знака, дешифратор 15, триггер 16, блок 17 памяти, блок 18 вычитания, блок 19 сложения.

Устройство позволяет воспроизводить значения синуса и косинуса при дискретном задании аргумента с использованием опорных значений функций из блока памяти в качеОтве начальных условий интегрирования и интегрирования на интервале, определенном остатком аргумента, получающимся после вьзделения из него целой части, выраженной в единицах дискрета задания опорных значений функций и определяющей для синуса ближайшее меньшее по абсолютной величине опорное значение, а для косинуса - ближайшее большее по абсолютной величине опорное значение. Интегрирование реализуется при помощи итерационного принципа с использованием рекуррентных формул

а.ч- Ъ. д.

CD (2)

Ь. - а. д.

значение синуса на i-ом

где а- шаге;

Ь значение косинуса на i-ом шаге;

изменяется от до значе1ния, равного остатку аргумента, выраженному в единицах дискрета задания аргумента;

Д Зо дискрет задания аргумента; начальное условие для синуса,

Ь„ начальное условие для косинуса.

Для определенности считаем, что устройство предназначено для вычисления в 16-ти разрядной двоичной сетке функций синуса и косинуса при задании аргумента с дискретностью 2 а опорных значений функций с дискретностью 7Г/32.

В исходном положении триггер 16 устанавливают в нулевое состояние и в блок 17 вводят опорное значение функций синуса и косинуса для значений аргумента: О, 7t/32, 2 , 3 ГГ/32, 4 К;/32, 5 Tt/32, 6 /Ъ2, 11t/Ъ2, 8-ТС/32 (всего восемнадцать значений);

Значение аргумента в двоичном коде в радианной мере записывается по входу 2 устройства в делитель 1 аргумента, а по входу 4 устройства двоичный код поступает в делитель 1 и блок 18. В результате деления аргумента на Tt/22 в делителе 1 образуется двоичное число, в котором используются шесть младших разрядов целой части и пять разрядо (с 4-го по 8-й) остатка. Значения шестого и пятого разрядов целой части поступают в регистр 14 . Шестой и пятый разряды указывают номер квадранта,в который попадает аргумент, и соответственно знаки функций синуса и косинуса (00 : ++, 0,1 : +-; 10 -; 11 : -+).

Разряды целой части с первого по пятый поступают в блок 19. Здесь значение пятого разряда складывается с двоичным кодом первых четырех разрядов. Это делается для того, чтобы для аргументов, попадающих |ВО II и IV квадранты, также как для аргументов, попадающих в I и JII квадранты, сохранить неизменной схему интегрирования по формулам (1) и (2). Полученные значения четырех млад ших разрядов целой части поступают в блок 13 адресации, а .значение чет вертого разряда поступает на вход коммутатора 12. Согласно значению трех разрядов, определяющих микроинтервал, из блока 17 памяти должны быть считаны и записаны в регистр б синуса и регистр 9 косинуса соответ ствующие значения функций. При этом значение четвертого разряда показывает, какой восьмой части круга при надлежит аргумент - (О; тг/4 или (Rr/4; гг/2) . Значение О указывает на промежуток (О , /4) и соответственно на считывание из блока 17 зна чений функций, поставленных в соответствие значению трех младших раз.рядов целой части. Значение 1 указывает на промежуток (it/4; 7Г/2) и соответственно на считывание из блока 17 последующих значений функций синуса и косинуса, что соответствует зеркальному -значению аргумента В промежутке (0)1Г /4) . В последнем случае при значении четвертого разряда, равном 1, коммутатор 12 изменяет место записи (регистры синуса и косинуса) считываеNMx из блока 17 памяти опорных значений, что соответствует формуле приведения к дополнительному углу для. функций синуса и косинуса. Значения пяти разрядов (используются разряды с 4-го по 8-й) остат ка из делителя 1 поступают на первый вход блока 18 и на вход коммута тора 11. В блоке 18 производится вычитание из пяти старших разрядов числа 17732 пятиразрядного кода оста ка, и полученное значение поступает на второй вход коммутатора 11 остат ка. На другой вход коммутатора 11 из делителя 1 аргумента поступает значение 5-го разряда целой части, причем если это значение равно О, что соответствует тому, что аргумент находится в I или III квадрантах, то в счетчик 5 остатка через коммутатор 11 проходит значение остатка, полученное в делителе 1, в противном случае, при значении 5-го разряда целой части, равной 1 чт соответствует тому, что аргумент находится во II или в III квадранта в счетчик 5 через коммутатор 11 про ходит преобразованное значение остатка, полученное в блоке 18. Через интервал времени, определя Nttift элементом 3 задержки, необходимый для записи опорных значений функций в регистры б и 9, триггер 1 перебрасывается в единичное состоян и запускается генератор 10 импульсо Управляющие сигналы с выхода генера тора 10 начинают поступат-ь на вычитающий вход счетчика 5 остатка, на управл$пощие входы регистра б синуса и регистра 9 косинуса и на управл пощие входы блоков сложения 7 и вычитания 8. В этом случае с первого выхода регистра б синуса на первый вход блока 7 сложения поступает 16-разрядный код синуса, со второго выхода регистра 9 косинуса на второй вход блока 7 сложения для ввода 8-ми младших ра:зрядов поступает 8-разрядный код, образованный первойполовиной разрядов (8 старших разрядов) значения косинуса. Одновременно с первого выхода регистра 9 косинуса на первый вход блока 8 вычитания поступает 16-разрядный код косинуса, со второго выхода регистра б синуса на второй вход блока 8 вычитания для ввода 8-ми младших разрядов поступает 8-разрядный код, образованный первой половиной разрядов (8 старших разрядов) значения синуса. Результат сложения кодов, поступивших на первый и второй входы блока 7 сложения, поступает в регистр 6 синуса,и следовательно, в нем устанавливается число, превышающее исходное на величину, соответствующую одной итерации по формуле (1). Результат вычитания из кода, поступившего на первый вход кода и на второй вход блока 8 вычитания, поступает в регистр 9 косинуса ,и следовательно, в нем устанавливается число, меньше исходного на величину, соответствующую одной итерации по формуле (2). Описанная процедура накопления в регистрах 8 и 9 повторяется до тех пор, пока не будет вычтено из счетчика 5 остатка значения остатка. В этом случае с выхода дешифратора 15 (например, многовходового элемента И) сигналом, фиксирующим нулевое состояние счетчика 5, триггер 16 устанавливается в единичное состояние и генератор 10 затормаживается. При этом на выходе устройства формируются значения функций синуса и косинуса, а также знаки этих функций. Преимущества предложенного устройства по сравнению с известным определяется следующим. Вместо коммутатора на 32 разряда и коммутатора на 48 разрядов, использованных в известном устройстве, в предложенном устройстве используются коммутатор на 32 разряда, коммутатор йа 10 разрядов и два дополнительныхмалоразрядных блока (в качестве блока 18 преобразования остатка может использоваться 5-разрядный блок вычитания, а в качестве блока- 19 преобразования целой части может использоваться 4-рлэрядный блок сложения). Кроме того, при считывании из известного устройства вычисленных значе ний синуса и косинуса потребуется применение дополнительного коммутат ра на 32 разряда. В предложенном устройстве этого не требуется, поскольку здесь вычисленные значения не меняют своего местоположения в регистрах синуса и косинуса. Формула изобретения Устройство для вычисления функци синуса и косинуса, содержащее делитель аргумента, два коммутатора, счетчик остатка, элемент задержки, дешифратор, триггер, генератор импульсов , блок адресации, блох памяти, первый блок вычитания, первый блок сложения, регистр знака, регис косинуса и регистр синуса, причем вход аргумента устройства соединен с входом элемента задержки и информационным входом делителя аргумента управляющий .вход и выход младмих разрядов которого соединены соответ ственно с входом делителя аргумента устройства и первым информационным входом первого коммутатора, выход старших разрядов делителя соединен с входом регистра знака, выход элемента задержки - с первым входом триггера, второй вход которого соединен через дешифратор с выходом счетчика остатка, вход вычитания которого соединен с выходом генератора импульсов и управляющими входа ми регистра синуса, первых блока вычитания и сложения и регистра косинуса, первые выходы регистров синуса и косинуса соединены соответ ственно с первыми входами первых блоков сложения и вычитания, вторые входы которых соединены соответственно со вторыми выходами регистра косинуса и регистра синуса, вход генератора импульсов соединен с выходом триггера, выход блока адресации - с входом блока памяти, о тличающееся тем, что, с целью упрощения устройства, оно содержит второй блок вычитания и второй блок сложения, выход которого соединен с входом блока адресации и управляющим входом второго коммутатора, информационный вход которого соединен с выходом блока памяти, первый и второй выходы второго коммутатора соединены соответственно с установочными входами регистра косинуса и регистра синуса, информационные входы которых соединены соответственно с выходами первого блока вычитания и первого блока сложения, вход второго блока сложения соединен с выходом старших разрядов делителя аргумента, выход младших разрядов соединен с первым входом второго блока вычитания, второй вход и выход которого соединены соответственно с входом делителя устройства и вторым информационным входом первого коммутатора, выход и управляющий вход которого соединены соответственно с установочным входом счетчика остатка и выходом старших разрядов делителя аргумента. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР №419896, кл. G Об F 7/548, 1973. 2.Авторское свидетельство СССР №531161, кл. G 06 F 7/548, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функций синуса и косинуса | 1974 |

|

SU531161A1 |

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

| Цифровой вычислитель функций синуса и косинуса | 1976 |

|

SU622087A1 |

| Синусно-косинусный функциональный преобразователь | 1980 |

|

SU888111A1 |

| Устройство для вычисления спектрафуНКций уОлшА | 1979 |

|

SU849224A1 |

| Устройство для вычисления тангенса | 1975 |

|

SU650073A1 |

| Цифровой вычислитель синуса и косинуса | 1977 |

|

SU682905A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU955082A1 |

| Устройство для преобразования координат | 1983 |

|

SU1141405A1 |

| Устройство для деления чисел без восстановления остатка | 1989 |

|

SU1605228A1 |

Авторы

Даты

1982-09-23—Публикация

1981-01-15—Подача