1

Изобретение относится к вычислительной технике (автоматизированным системам контроля логических блоков).

Известны устройства для контроля логических блоков, работающих по принципу контроля функционирования блоков, заключающемуся в том, что на входы контролируемых блоков подается последовательность входных наборов и сравниваются выходные значения сигналов с эталонными наборами.

Известно контрольное устройство для хранения эталонных входных -и выходных наборов кодов, содержащее запоминающие устройства и сравниватели, связанные

между собой и блоками для управления и синхронизации 1 Известно также устройство, содержащее блок для хранения эталонных входных наборов, блок для хранения эталонных вы- ходных наборов, блок для сравнения и управляющий блок,причем первые вход и выход блока для сравнения соединены с первыми выходом и входом управляющего блока, второй выход которого соединен с

входом блока для хранения эталонных выходных наборов, выход которого с(единен с вторым входом блока для сравнения, третий вход которого соединен с входом устройства, третий выход управляющего блока соединен с входом блока для хранения эталонных входных наборов 2.

Контроль в данном случае осуществляется путем подачи на входы контролируемых логических блоков последовательности входных наборов, считываемых из блока для хранен лЛ входных наборов, и сравнения значений выходных сигналов, образующихся на выходах контролируемых блоков, с наборами, считываемыми из блока для хранения эталонных выходных наборов. Выявление блоком для сравнения неравенства хотя бы при одном сравнении свидетельствует о неисправности в контролируемых логических блоках.

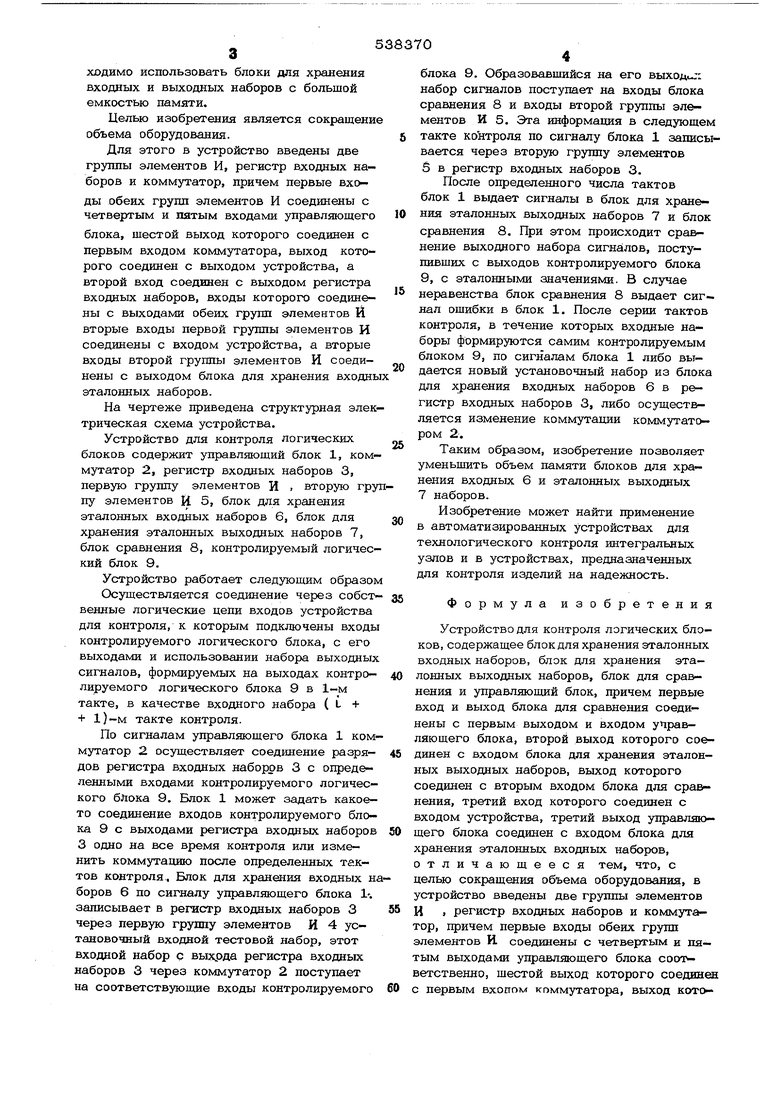

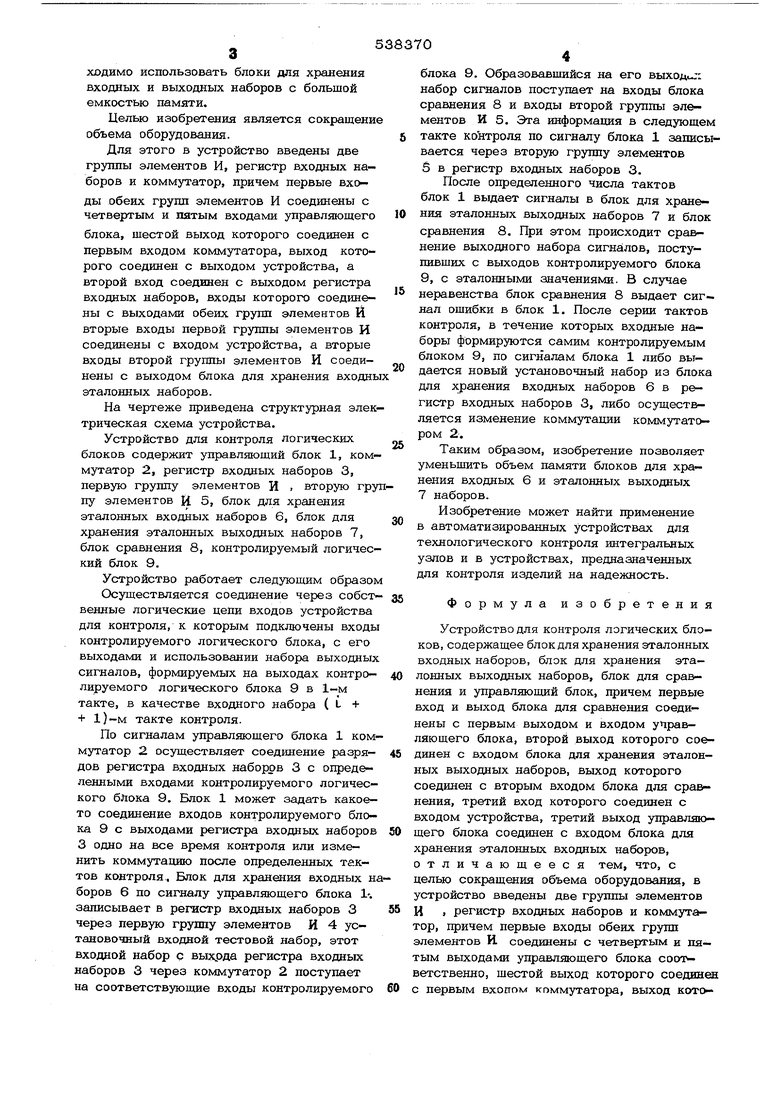

Однако в случае контроля интегральных узлов с больщой степенью интеграции и малым количеством входных и выходных контактов, которые требуют тестовых последовательностей большого объема, нео&ходимо использовать блоки для хранения входных и выходных наборов с большой емкостью памяти. Целью изобретения является сокращени объема оборудования. Для этого в устройство введены две группы элементов И, регистр входных наборов и коммутатор, причем первые входы обеих групп элементов И соединены с четвертым и пятым входами управляющего блока, щестой выход которого соединен с первым входом коммутатора, выход которого соединен с выходом устройства, а второй вход соединен с выходом регистра входных наборов, входы которого соединены с выходами обеих групп элементов И вторые входы первой группы элементов И соединены с входом устройства, а вторые входы второй группы элементов И соединены с выходом блока для хранения входны эталонных наборов. На чертеже приведена структурная элек трическая схема устройства. Устройство для контроля логических блоков содержит управляющий блок 1, коммутатор 2, регистр входных наборов 3, первую группу элементов Ц , вторую гру пу элементов И 5, блок для хранения эталонных входных наборов 6, блок для хранения эталонных выходных наборов 7, блок сравнения 8, контролируемый логичес кий блок 9. Устройство работает следующим образо Осуществляется соединение через собст венные логические цепи входов устройства для контроля, к которым подключены входы контролируемого логического блока, с его выходами и использовании набора выходных сигналов, формируемых на выходах контролируемого логического блока 9 в 1-м такте, в качестве входного набора ( L + + 1)-м такте контроля. По сигналам управляющего блока 1 ком мутатор 2 осуществляет соединение разря- дов регистра входных наборов 3 с определенными входами контролируемого логического блока 9. Блок 1 может задать какоето соединение входов контролируемого блока 9 с выходами регистра входнък наборов 3 одно на все время контроля или изменить коммутацию после определенных тактов контроля. Блок для хранения входных н боров 6 по сигналу управляющего блока 1. записывает в регистр входных наборов 3 через первую группу элементов И 4 установочный входной тестовой набор, этот входной набор с выхрда регистра входных наборов 3 через коммутатор 2 поступает на соответствующие входы контролируемого блока 9. Образовавшийся на его выкоц набор сигналов поступает на входы блока сравнения 8 и входы второй группы элементов И 5. Эта информация в следующем такте контроля по сигналу блока 1 записывается через вторую группу элементов 5 в регистр входных наборов 3. После определенного числа тактов блок 1 выдает сигналы в блок для хранения эталонных выходных наборов 7 и блок сравнения 8. При этом происходит сравнение выходного набора сигналов, поступивших с выходов контролируемого блока 9, с эталонными значениями. В случае неравенства блок сравнения 8 выдает сигнал ощибки в блок 1. После серии тактов контроля, в течение которых входные наборы формируются самим контролируемым блоком 9, по сигналам блока 1 либо выдается новый установочный набор из блока для хранения входных наборов 6 в регистр входных наборов 3, либо осуществляется изменение коммутации коммутатором 2. Таким образом, изобретение позволяет уменьшить объем памяти блоков для хранения входных 6 и эталонных выходных 7 наборов. Изобретение может найти применение в автоматизированных устройствах для технологического контроля интегральных узлов и в устройствах, предназначенных для контроля изделий на надежность. Формула изобретения Устройство для контроля логических блоков, содержащее блок для хранения эталонных входных наборов, блок для хранения эталонных выходных наборов, блок для сравнения и управляющий блок, причем первые вход и выход блока для сравнения соединены с первым выходом и входом управляющего блока, второй выход которого соединен с входом блока для хранения эталонных выходных наборов, выход которого соединен с вторым входом блока для сра&нения, третий вход которого соединен с входом устройства, третий выход управляющего блока соединен с входом блока для хранения эталонных входных наборов, отличающееся тем, что, с целью сокращения объема оборудования, в устройство введены две группы элементов И , регистр входных наборов и коммутатор, причем первые входы обеих групп элементов И соединены с четвертым и пятым выходами управляющего блока соответственно, щестой выход которого соединен с первым вхопом коммутатора, выход кото-

рого соединен с выходом устройства, а второй вход соединен с выходом регистра входных наборов, входы которого соединены с выходами обеих грухш элементов И , вторые входы первой грушш элементов И соединены с входом устройства, а вторые входы второй группы элементов И соединены с выходом блока для хранения входных эталонных наборов.

Источники информации, принятые во внимание при экспертизе:

1.Буферные быстродействующие устройства на сдвиговых регистрах, Электроника, 1971, № 10, с. 38-43.

2.Авторское свидетельство СССР

0)05 В 23/00 27.06.

№ 377738, МКИ 73 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логическихблОКОВ | 1978 |

|

SU811267A1 |

| Устройство для контроля цифровых блоков | 1982 |

|

SU1037261A1 |

| Устройство для проверки функционирования логических схем | 1980 |

|

SU955072A1 |

| Устройство для контроля логических схем | 1985 |

|

SU1252786A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| АВТОМАТИЗИРОВАННЫЙ КОМПЛЕКС КОНТРОЛЯ И ДИАГНОСТИКИ (ВАРИАНТЫ) | 2003 |

|

RU2257604C2 |

| Устройство для контроля логических блоков | 1984 |

|

SU1196692A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1982 |

|

SU1108451A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1430957A2 |

Авторы

Даты

1976-12-05—Публикация

1975-04-14—Подача