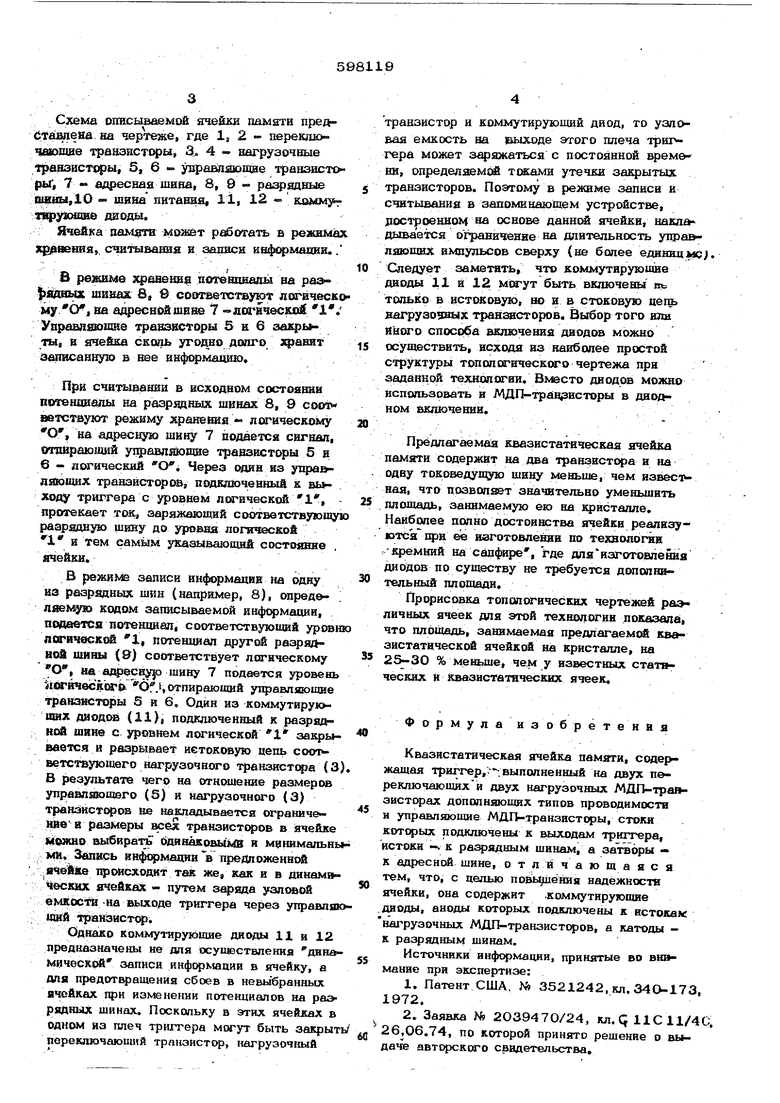

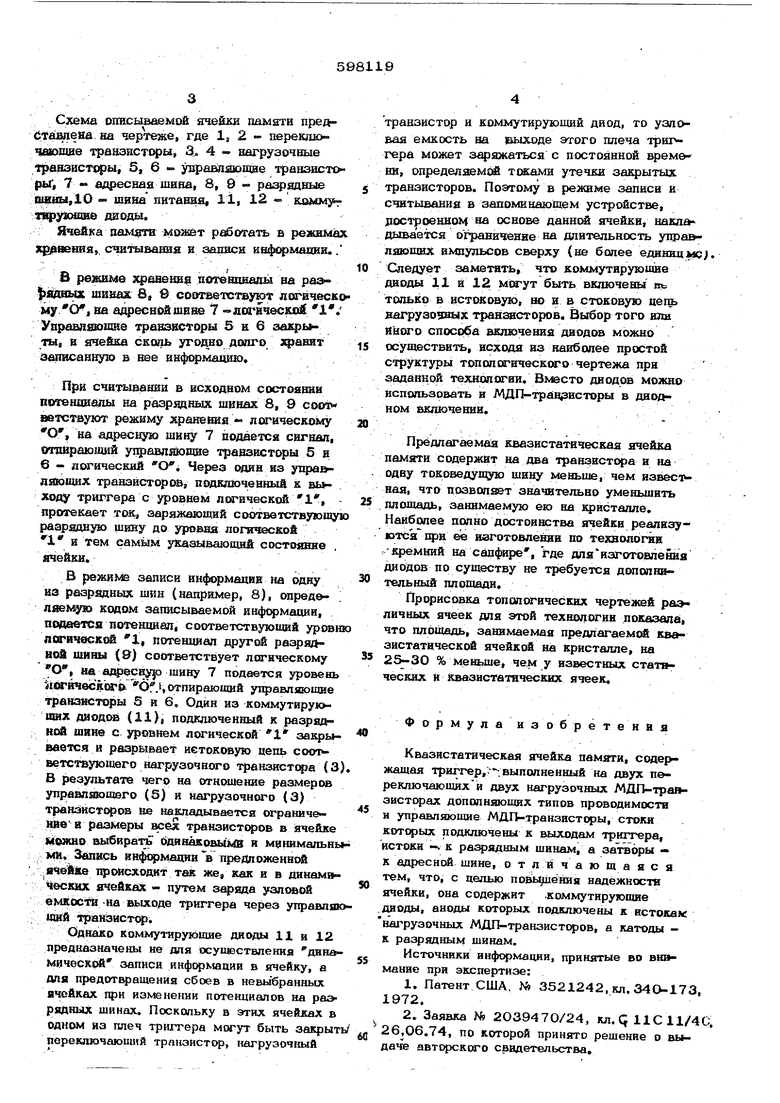

(54) КВАЗИСТАТИЧЕСКАЯ ЯЧЕЙКА ПАМЯТИ Схема описываемЕЙ ячейки памяти предйташена ва чертеже, где 1, 2 - перекшочаювше транзйСтсфы, 3 4 нагрузочные 1равзистсры, 5, 6 - увравляющае транзисто рьГ, 7 адресная шняа, 8, 9 разрядные аишы,1О шина питания, lij 12 «° &амму 1Г1фУ10«Ш6 Д0ОДЫ. Ячейка памяти может работать в , считглвання и записи наф рмадии.. - « - В режиме хревеш|1 потенпиапы ва раз | 1цшых шгнаж 3, & соответствуют л огвческ( му 6, йа адресной ШВЕЙ 7 -логической 1, Упрашяююив трааэдаторы 5 Е 6 закрыты, в ячейка скояь угодно долго зфавит дашсавну: в вее информацию. При считьшан0и в ЁСХОДВОМ состоянии потеновалы на разрядных шивах 8, 9 сооо ветстауют режиму хранегая лшическому О , на адресную шину 7 подается сигнал, (тшраюший управляоовше транзисторы 5 в 6 - логический Через один из утфавлясюших транзисторов, подключенный к вь хоод триггера с уровнем логической 1, протекает ток, заряжающий соответствующу разрядную шику до уровня логической 1 и тем самым указывающий состояние , ячейки. В режима записи информации на одну из разрядных ШИН (например, 8), опред ляем кодом записываемой информации, подеется потенциал, соответствующий уровн логячбскоЗ 1, потенциал другсхб раэржь вой шины (9) соответствует логическому О, на шину 7 подеется уровень д йчесвсГ1& Of., отпирающий управляющие транзисторы 5 и 6. Один из коммутирук ших диодов (llh подключенный к разрядкод шине С- уровнем логической I закрьь вается и разрывает иетоксюую цепь соответствующего нагрузочного TpaHancTqpa (3 В результате чего на отношение размеров управляющего (5) и Нагрузочного (3) транзистс ов Be накладывается ограничеНива размеры всех транзистс ов в ячейке М10жно вы6кра1ъ бДинакоаымв и М(1нимальн ми. Зешись йнфсрмаоиив предложенн ячейке 1Ф1ЖСХОДИТ так же, как и в динамв Ч1вских ячейках путем заряда узлсюой емкости-на выходе триггера через управля щвй тфаи зистсчр. Однако коммутирующие диоды 11 я 12 предназначены не для осуществления сина мическрй записи кнффкиции в ячейку, а дпя предотвращения сбоев в невыбранных ячейках при изменении потенциалов на ра рядных щинах. Поскольку в этих ячейках в одном из плеч три1тера могут быть закры переключающий трпнэистор, нагрузочный ранзистор и коммутирующий диод, то узлсь ая емкслть на этого плеча триг ера может заряжаться с постоянной времеи, определяемой тска.ш утечки закрытых ранзисторов. Поэтому в режиме записи и читывания в запоминающем устройстве, остроенном на основе данной ячейки, наклд дьтается ограничение на длительность управяющих импульсов сверху (не более единицмСЬ Следует заметать, что коммутирующие диоды 11 и 12 мотут быть включены кь только в и:стоковую, но и в стоковую цеш нагрузочных транздсторов. Выбор того или иного способ включения диодов можно осуществить, исх(здя из наиболее простой структуры топопогического чертежа при заданной технологии. Вместо диодов можно использовать и МДП-тран исторы в диодном включении. Предлагаемая квазистатнческая ячейка памяти содержит на два транзистора и на одну токоведущую шину меньпю, чем известная, что позвопяет значительно уменыаить площадь, занимаемую ею на кристалле. Наиболее полно достоинства ячейки реализуются при ее ивготовлевии по техвологии : кремний на сапфире . Где дляизготовления диодов по существу не требуется дополнительный площади. Прорисовка топологических чертежей различных ячеек для этой технологии показала, что площадь, занимаемая предлагаемой квазистатической ячейкой на кристалле, на 25-30 % меньще, чем у известных статвческих и Квазистатических ячеек. Формула изобретения Квазистатическая ячейка памяти, содер жащая триггер,.-.выполненный на двух переключающихи двух нагрузочных МДП-тра зист фах дополняющих типов проводимости и управляющие Л1Д1Ъ-транзист« ы, стоки подключены к выходам триггера, истоки -. к разрядным шинам, а затворы - к адресной шине, о т л и чающаяся тем, что, с целью повыщ йия надёжности ячейки, она содержит .коммутирующие .диоды, аноды которых подключены к иСтокак нагрузочных МДП-транзистсров, а катоды к разрядным шинам. Источники информации, принятые во вн9маняе при экспертизе: 1.Патент США, й 3521242, кл. 340-173, 1972. 2.Заявка Ns 2039470/24, кл. Q 11С11/4С. 26,06.74, по которой принято рещеняе о вы даче свидетельства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Квазистатическая ячейка памяти | 1974 |

|

SU541197A1 |

| Запоминающий элемент | 1979 |

|

SU773738A1 |

| Квазистатическая ячейка памяти | 1974 |

|

SU541198A1 |

| Статическая ячейка памяти на мдп- ТРАНзиСТОРАХ | 1979 |

|

SU799004A1 |

| Программируемое постоянное за-пОМиНАющЕЕ уСТРОйСТВО | 1978 |

|

SU809378A1 |

| Динамическая ячейка на мдп транзисторах | 1973 |

|

SU478361A1 |

| Матричный накопитель для электрорепрограммируемого запоминающего устройства | 1980 |

|

SU1336110A1 |

| Параллельный дешифратор на допол-НяющиХ Мдп-ТРАНзиСТОРАХ" | 1978 |

|

SU798997A1 |

| Ячейка памяти (ее варианты) | 1982 |

|

SU1115106A1 |

| Ячейка памяти для регистра сдвига | 1975 |

|

SU570108A1 |

Авторы

Даты

1978-03-15—Публикация

1975-12-15—Подача