I

Изобретение относится к области вычислительной техники и может быть использовано в аналоговых и аналого-цифровых вычислительных машинах в схемах квантования сигналов ПО времени, при создании линий задерлжи и т. д.

Известно и широко применяется в вычислительных машинах запоминаюш,ее устройство, строящееся с применением ячеек памяти. Простейшая ячейка содержит конденсатор памяти, усилитель-повторитель и ключ. Основным (Параметром запоминаюш;его устройства является отношение времени хранения к времени записи. Простейшая ячейка памяти характеризуется минимальным временем записи, а указанное отношение ограничивается недостаточным входным сопротивлением повторителя, определяющим время хранения. Существует ряд схем, улучшающих работу ячейки памяти iB режиме записи информации (режим слежения). Такая ячейка содержит помимо ключа, конденсатора памяти и повторителя, операционный усилитель, подключаемый Б режиме записи в цепь отрицательной обратной связи, улучщающий в этом режиме точность слежения и уменьшающий время записи. Однако на режим хранения усилитель влияния не оказывает.

Известно также устройство, наиболее близкое к изобретению по технической сущности.

содержащее ячейки памяти, выход последней из которых связан с выходом устройства и одним из входов (Первой ячейки памяти, другой вход которой соединен через ключ с входом

устройства, управляющий вход ключа подключен К шине управления, управляющие входы ячеек памяти подсоединены к выходам генератора соответственно, и щину питания. Основным недостатком указанной схемы является малое время хранения, ограниченное величиной входного сопротивления усилителяповторителя ячейки памяти.

Цель изобретения - увеличение времени хранения информации.

Это достигается введением в устройство масштабного блока и дополнительного ключа, вход которого подключен к щине питания, выход дополнительного ключа соединен с управляющим входом генератора, управляющий

вход дополнительного ключа подключен к щине управления, выход первой ячейки памяти - к входу масщтабного блока, выход масщтабного блока-к входу последней ячейки памяти, управляющий вход которой соединен с щиной управления.

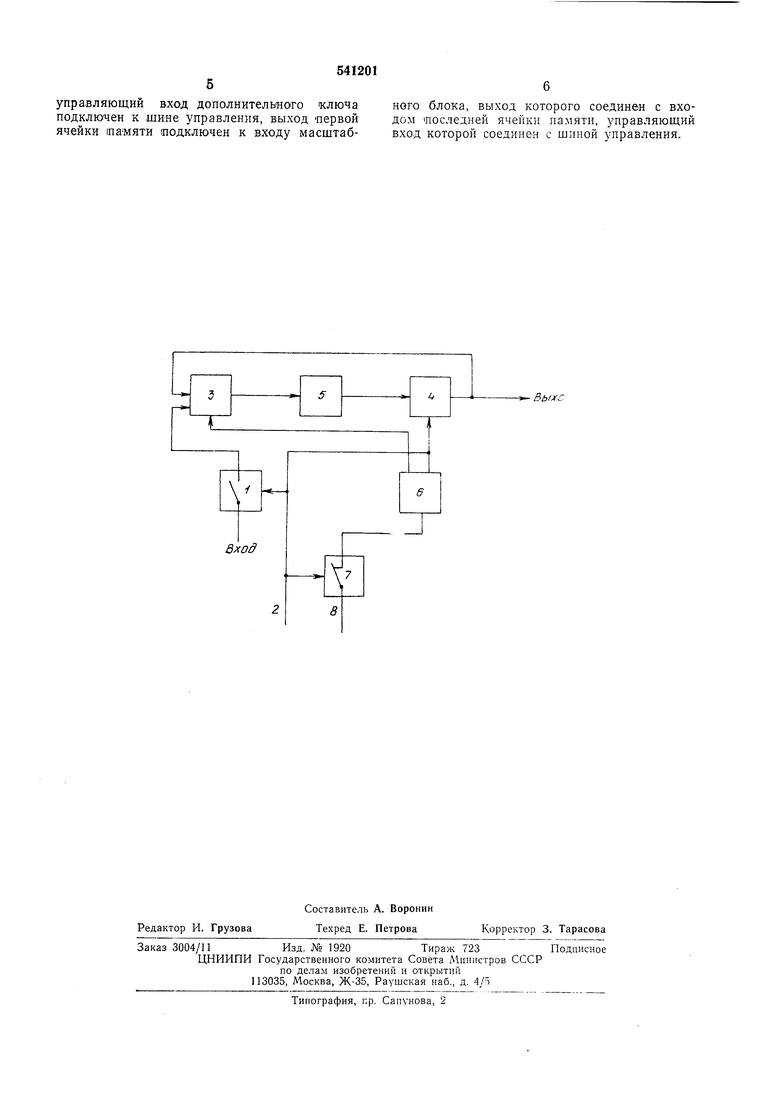

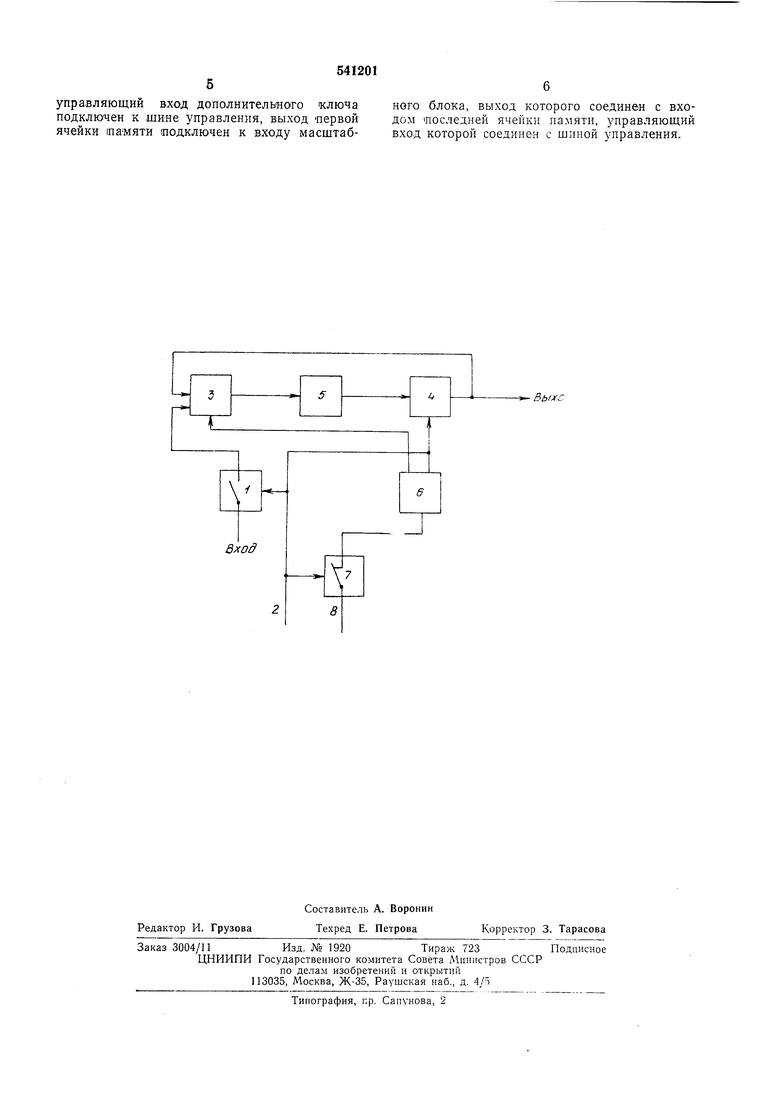

На чертеже представлена схема аналогового запоминающего устройства.

Оно содерл ит ключ 1, установленный в цепи входного сигнала и управляемый командным импульсом, поступающим по шине управления 2, ячейки памяти 3, 4, масштабный блок 5, вход которото соединен с выходом ячейки памяти 3, а выход - с входом ячейки 4, тенератор 6 управляющих импульсов с двумя выходами, ключ 7 и шину питания 8. Каждая из ячеек 3, 4 содержит ключ, вход которого является входом ячейки, конденсатор памяти и усилитель-повторитель. Выход ключа ячейки памяти соединен с конденсатором памяти и входом усилителя-повторителя. Выход усилителя-1повторителя служит выходом ячейки памяти (3, 4), а вход его - вторым входом ячейки ламяти (3, 4). Управляющий вход ключа является управляющим входом ячейки памяти 3, другой вход которой соединен с выходом ключа 1. Управляющие входы ячеек памяти 3, 4 соединены соответствен«о с выходами генератора 6 управляющих иметульсов, а управляющий вход ячейки памяти 4, кроме того, - с шиной управления 2. Питание на генератор 6 подается с щины питания 8 через ключ 7, управляющий вход которого соединен с шиной управления 2.

Аналоговое запоминающее устройство работает в двух режимах: записи и хранения.

Р е л-: и м записи. При подаче командного импульса на управляющие входы ключей 1 и 7 и ячейки памяти 4 аналоговый сигнал записывается на конденсаторе памяти ячейки 3 и через масщтабный блок 5 «а конденсаторе памяти ячейки 4. Ключ 7 размыкается и снимает питание с генератора Q, чтобы предотвратить случайное замыкание ключа ячейки памяти 3 импульсом генератора Q в момент записи, так как при этом образовался бы контур с положительной обратной связью (ячейки памяти 3 - масщтабный блок 5 - ячейки паМяти 4) и создались бы условия для самовозбуждения схемы.

Режим хранения. По окончании командного импульса ключ 1 размыкается, ключ 7 замыкается, напряжение питания подается на тенератор 6 управляющих импульсов. Генератор вырабатывает две бесконечные во времени последовательности импульсов, смещенных одна относительно другой на определенный интервал времени. Частота следования импульсов на обоих выходах генератора одинакова и постоянна. Она определяется допустимой ощибкой аналогового запоминающего устройства, в режиме хранения и постоянной времени конденсаторов памяти ячеек 3, 4. Генератором управляющих импульсов может служить, например, питающая сеть переменного тока. В этом случае один полупериод напряжение сети управляет ячейкой памяти 3, другой - ячейкой 4. Таким образом происходит поочередное обновление информации на ячейках памяти 3 и 4. В период отсутствия управляющих импульсов с выходов -генератора 6 конденсаторы памяти ячеек 3 и 4 разряжаются через входное сопротивление соответствующих усилителей-повторителей (ощибка хранения).

Однако благодаря попеременному включению ключей ячеек памяти 3 и 4 эта ощибка мол-сет быть существенно уменьщена, так как в схеме происходит попеременная передача напряжений с конденсатора памяти ячейки 4 на конденсатор памяти ячейки 3 и с конденсатора памяти ячейки 3 через масщтабный блок 5, восстанавливающий запомненный уровень сигнала, на конденсатор памяти ячейки 4..

Коэффициент передачи масщтабного блока 5 выбирается таким, чтобы восстановить на конденсаторе памяти ячейки 4 первоначальнозапомненную величину напрялсения (компенсировать разряд конденсаторов памяти ячеек 3 и 4 за время меладу последовательными импульсами, приходящими на ключ ячейки памяти 3, 4 с генератора 6), например, если частота следования импульсов - f, постоянные времени разряда конденсаторов памяти ячеек памяти 3, 4 одинаковы и равны Гр, щирина импульсов равна половине периода следования, то коэффициент передачи масщтабного блока 5 определяется вырал ;ением

/ Г 2/.7р у

L27-V-TJ

При этом на выходе аналогового запоминающего устройства напрялсение представляет собой сумму постоянной составляющей, равной запомненному значению напряжения Us, и пульсаций треугольной формы с частотой / и амплитудой

и

2/.7-р-1

Таким образом, за счет периодического восстановления напряжения на конденсаторе памяти ячейки 4 время хранения предлагаемого аналогового запоминающего устройства существенно увеличивается. При испытаниях лабораторного макета запоминающего устройства на предприятии-заявителе при Гр 1 сек ( мкф, ,1 мгом) получено время хранения 200 сек (погрещность менее 5%). Время же хранения отдельной ячейки памяти при указанных параметрах схемы было бы 0,05 сек.

Формула изобретения

Аналоговое запоминающее устройство, содержащее ячейки памяти, выход последней из которых соединен с выходом устройства и одним из входов первой ячейки памяти, другой в.ход которой соединен через ключ с входом устройства, управляющий вход ключа подключен к щине управления, управляющие входы ячеек памяти подсоединены к выходам генератора соответственно, и щину питания, отличающееся тем, что, с целью увеличения времени храпения информации, в устройство введены масщтабный блок и дополнительный ключ, вход которого подключен к щине питания, выход дополнительного ключа соединен с управляющим входом генератора.

управляющий вход дополнительного ключа подключен к шине управления, выход первой ячейки пЯМяти подключен к входу масштаб6

ного блока, выход которого соединен с входом последней ячейки памяти, управляющий вход которой соединен с шиной управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1979 |

|

SU930387A1 |

| Аналоговая ячейка памяти | 1973 |

|

SU495710A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| Аналоговое запоминающее устройство | 1982 |

|

SU1104585A1 |

| Дискретно-аналоговая линия задержки | 1982 |

|

SU1115230A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU873278A1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU858111A1 |

| Дискретно-аналоговая линия задержки | 1980 |

|

SU930583A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU864342A1 |

Вь/хс

Авторы

Даты

1976-12-30—Публикация

1973-04-28—Подача