Изобретение относится к вычислительной технике, в частности к устройствам для модификации команд и может быть использовано при построении устройств управления ЦВМ. Известно устройство для модификации, содержащее индексный регистр, элементы И, регнстр арифметического устройства, коммутатор адресной информации, регистр дешифратора адреса операнда и дешифратор операций. Оно характеризуется наличием специального регистра адреса операнда со сложными связями с другими блоками, причем модификации может иодлежать только часть разрядов одного поля слова команды, что приводит к увеличению аииаратурных затрат. Наиболее близким к изобретению по техиической суш,ности и достигаемому результату яв.тяется устройство для модификации комаид, содержаuiee блок оперативной иамяти, разрядные выходы которого соединены с первыми входами элементов И первой и второй групп, арифметико-логический блок, выходы которого соединены с разрядными входами блока оперативиой иамяти, блок управления, входы которого соедииены с выходами элементов PI первой груииы, первый, второй и третий выходы соединены соответственно со вторыми входами элементов И первой группы, со вторыми входами элемеитов И второй группы и с управляющим входом арифметико-логического блока, входы которого соединены с выходами элементов И второй группы, первая группа адресных входов блока оперативной намяти соединена с груииой входов устройства, а блок оиеративиой памяти содержит адресный регистр, дешифратор, формирователи токов и первую группу ячеек, адресные входы которых соединены через последовательно соединенные формирователи тока, дешифратор и адресиый регистр с первой группой адресных входов блока оперативной памятп. В этом известном устройстве налнчие едииого адресного тракта как прн обращении к ячейкам хранення информации, так и при обращении к ячейкам, выиолняюнднм функции нндексных регнстров, прнводит к сннжению быстродействня устройства и его усложненню. Цель изобретення - новышение быстродействия и упрощение схемы. В описываемом устройстве это достигается тем, что в нем группа выходов блока управления соединена со второй груииой адресных входов блока оператнвной намяти, который содержит вторую груниу ячеек и реверсивные формирователи тока, причем вторая грунна адресных входов блока онеративной намятн через реверснвные формирователи тока соединена с адресными входами второй груипы ячеек, разрядные входы и вы.ходы которой соединены соответственно с разрядными выходами первой грунпы ячеек блока оперативной памяти и разрядными выходами блока оперативной памяти.

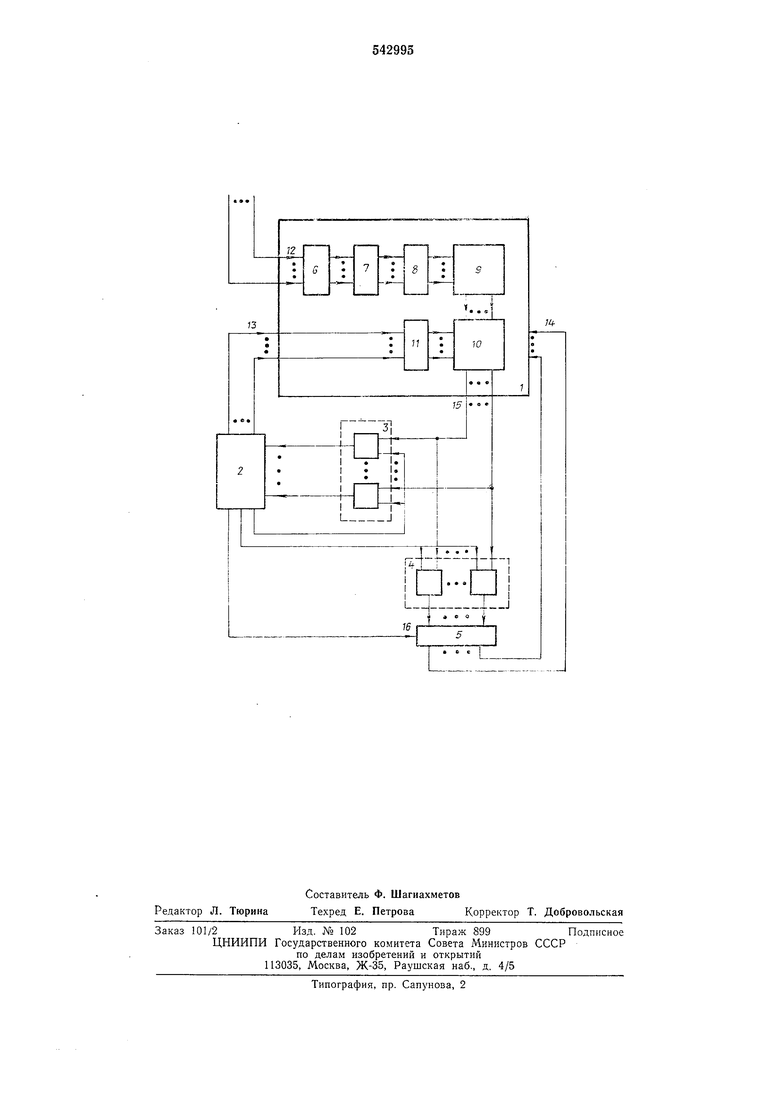

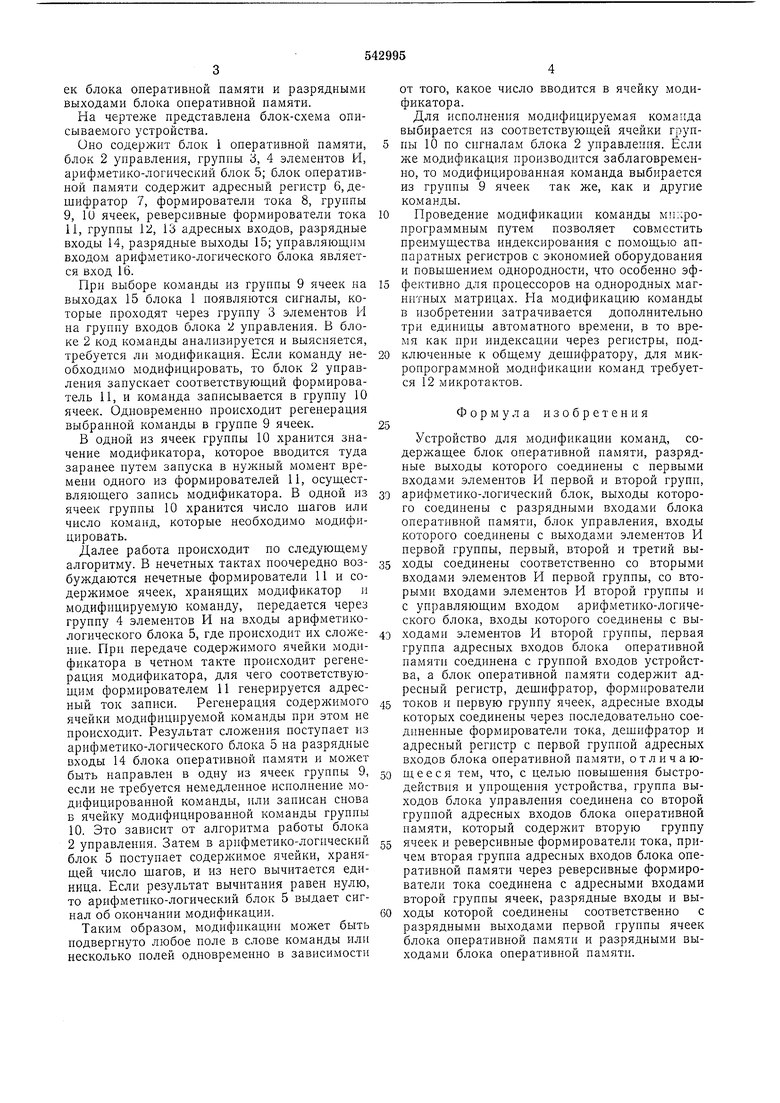

На чертеже представлена блок-схема описываемого устройства.

Оно содержит блок 1 оперативной памяти, блок 2 управления, группы 3, 4 элементов И, арифметико-логический блок 5; блок оперативной памяти содержит адресный регистр 6, дешифратор 7, формирователи тока 8, группы

9,10 ячеек, реверсивные формирователи тока 11, группы 12, 13 адресных входов, разрядные входы 14, разрядные выходы 15; управляющим входом арифметико-логического блока является вход 16.

При выборе команды из группы 9 ячеек на выходах 15 блока 1 появляются сигналы, которые проходят через группу 3 элементов И на группу входов блока 2 управления. В блоке 2 код команды анализируется и выясняется, требуется ли модификация. Если команду необходимо модифицировать, то блок 2 управления запускает соответствующий формирователь 11, и команда записывается в группу 10 ячеек. Одновременно происходит регенерация выбранной команды в группе 9 ячеек.

В одной из ячеек группы 10 хранится значение модификатора, которое вводится туда заранее путем запуска в нужный момент времени одного нз формирователей 11, осуществляющего запись модификатора. В одной из ячеек группы 10 хранится число шагов или число команд, которые необходимо модифицировать.

Далее работа происходит по следующему алгоритму. В нечетных тактах поочередно возбуждаются нечетные формирователи 11 и содержимое ячеек, хранящих модификатор п модифицируемую команду, передается через группу 4 элементов И на входы арифметикологического блока 5, где происходит их сложение. При передаче содержимого ячейки модификатора в четном такте происходит регенерация модификатора, для чего соответствующим формирователем 11 генерируется адресный ток записи. Регенерация содерлсимого ячейки модифицируемой команды при этом не происходит. Результат сложения поступает из арифметико-логического блока 5 на разрядные входы 14 блока оперативной памятн и может быть направлен в одну из ячеек группы 9, если не требуется немедленное нсполпение модифицированной команды, или записан снова Б ячейку модифицированной команды группы

10.Это зависит от алгоритма работы блока 2 управления. Затем в арифметико-логический блок 5 поступает содержимое ячейки, хранящей число шагов, и из него вычитается единица. Если результат вычитания равен нулю, то арифметнко-логический блок 5 выдает сигнал об окончании модификации.

Таким образом, модификации может быть подвергнуто любое ноле в слове команды илп несколько полей одновременно в зависимости

от того, какое число вводится в ячейку модификатора.

Для исполнения модифицируемая команда выбирается из соответствующей ячейки группы 10 по сигналам блока 2 управления. Если же модификация производится заблаговременно, то модифицированная команда выбирается из грунпы 9 ячеек так же, как и другие команды.

Проведение модификации команды микропрограммным путем позволяет совместнть преимущества индексирования с помощью аппаратных регистров с экономией оборудования и повышением однородности, что особенно эффективно для нроцессоров на однородных магнитных матрицах. На модификацию команды в изобретении затрачивается дополнительно три единицы автоматного времени, в то время как при ипдексации через регистры, подключенные к общему дешифратору, для микропрограммной модификации команд требуется 12 микротактов.

Формула изобретения

Устройство для модификации команд, содержащее блок оперативной памяти, разрядные выходы которого соединены с первыми входами элементов И первой и второй групп,

арифметико-логический блок, выходы которого соединены с разрядными входами блока оперативной памяти, блок управления, входы которого соединены с выходами элементов И первой грунпы, первый, второй и третий выходы соединены соответственно со вторыми входами элементов И первой группы, со вторыми входами элементов И второй группы и с управляющим входом арифметико-логического блока, входы которого соединены с выходами элементов И второй групны, первая группа адресных входов блока оператнвной памятн соединена с грунной входов устройства, а блок оперативной намяти содержит адресный регистр, дешифратор, формирователи

токов и нервую группу ячеек, адресные входы которых соединены через последовательно соединенные формирователи тока, дешифратор и адресный регистр с первой группой адресных входов блока оперативной памяти, отличающ е е с я тем, что, с целью повышения быстродействия и упрощення устройства, группа выходов блока управления соединена со второй группой адресных входов блока оперативной памяти, который содержит вторую группу

ячеек н реверсивные формирователи тока, причем вторая группа адресных входов блока оперативной памяти через реверсивные формирователи тока соединена с адресными входами второй группы ячеек, разрядные входы и выходы которой соединены соответственно с разрядными выходами первой группы ячеек блока оперативной памяти и разрядными выходамн блока оперативной памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления последовательностью команд | 1980 |

|

SU883904A1 |

| Однокристальный микропроцессор | 1978 |

|

SU734695A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559341A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Устройство управления | 1976 |

|

SU650079A1 |

| Устройство для отладки программ | 1979 |

|

SU849218A1 |

| Микропрограммное устройство для сопряжения процессора с абонентами | 1987 |

|

SU1539787A1 |

| Процессор с микропрограммным управлением | 1990 |

|

SU1700564A1 |

| 8-Битный микропроцессор | 1982 |

|

SU1161950A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559340A1 |

Авторы

Даты

1977-01-15—Публикация

1974-08-30—Подача