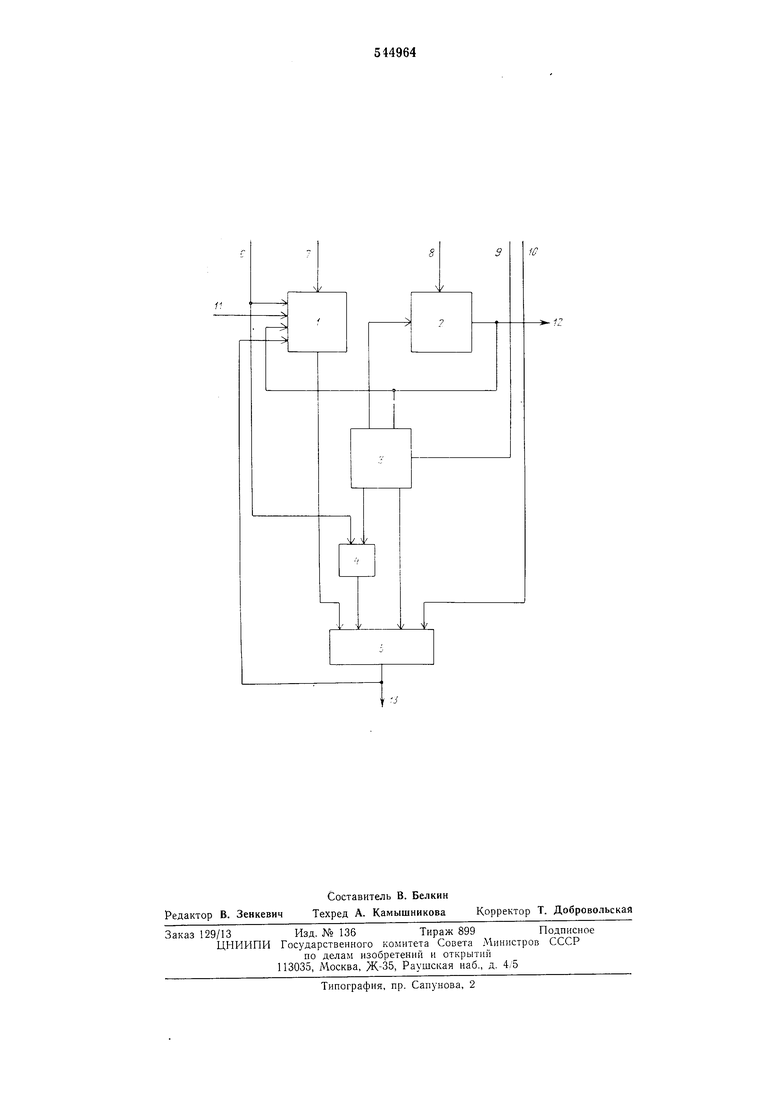

дом узла 3 управления переносом. Выход узла инвертированпя подключен к выходным информационным шинам 12 и второму входу узла управления переносом, первый выход узла управления переносом - к второму входу элемента И, к четырем входам элемента ИЛИ 5 присоединены соответственно выход переполнения сумматора 1, выход элемента И, второй выход узла унравления переносом и управляющий вход 10.

Работает устройство следующим образом.

Ири двухтактной системе синхронизирующих сигналов на управляющий вход 8 подается либо ирпзпак прямого кода (при сложении), либо инверсного (при вычитании), на управляющий вход 9 - иризнак режима, задающий осиоваиие q системы счисления, в которой должно работать устройство. Ири числе разрядов сумматора 1, равио.м п, максимальное возможное значение Q основания системы счислеиня q равно 2.

На первом такте в сумматоре 1 выполняется сложение или вычитание чиеел Zi, содержащегося в сумматоре, и Xi, поступающего на вход 11. В результате в сумматоре образуется при сложении число Zi , а при вычитании (Q-Xi)Q.

Иосле иервого такта иа первом выходе узла управления переносом формируется призиак «порогового кода, который равеп прп сложении числу (q-1), а прп вычитании - нулю.

Если , то на втором выходе узла управления переиосом формируется признак некомплектного кода, который возникает когда, .

Иризнак переноса на выходе сумматора 1 соответствует «переполнению сумматора, т. е. случаям; при сложении Zi+Aj Q-1, при вычитании .

Таким образом после иервого такта на выходе элемента ИЛИ 5 вознпкает признак переноса в одиом из трех следующих случаев: сумматор 1 переполнен, одновременно прнсутствуют признак переноса предыдущего разряда на входе 6 и признак «порогового кода, присутствует признак некомплектного кода. Иа втором такте к числу Zi добавляется (пли вычитается) число 1, если есть сигнал на входе 6, число (Q-q), при сигнале на выходе 13 н число (Q-(/-j-l), когда ирисутетвуют оба сигнала.

Иоеле двух тактов работы иа выходах сумматоров всех разрядов цифры иредставлеиы при положительио1М результате в прямом коде, при отрицательном - в коде дополнения до 9-1.

Выдача результата из сумматора может производиться как в прямом, так и в инверспом коде. Для выдачи положительных чисел на вход 8 устройства подается соответствующий управляющий сигнал (иризнак либо прямого, либо инверсного кода). Для выдачи отрицательных чисел предварительно поступает

управляющий сигнал на вход 10 и в сумматоре выполняется сложение по четвертому входу, в результате чего к содержимому сумматора 1 прибавляется число (Q-q). Затем происходит выдача. Ири этом для выдачи прямого кода на вход 8 необходимо подать призиак инверсного кода и наоборот.

Сложность предложенного устройства и прототипа оценивается числом базовых элементов ири Q 16 и q lQ для предложенного решения составляет 14,5, а для прототипа- 20. Таким образом, предложенное решение позволяет сократить расход элементов на 27,5%.

Формула изобретения

Арифметическое устройство, содержащее в каждом t-M разряде двоичный сумматор, входы которого соединены с информационными шинами и с выходом переноса из (г-1)-го разряда, а выход - с входом элемента ИЛИ, узел инвертирования, выходы которого соедииены с другими входами узла управления переносом и третьим входом двоичного сумматора, элементы И, ИЛИ, отличающееся тем, что, е целью упрощения устройства, в нем один из выходов узла уиравления переносом соедннен с одним из входов элемента

И, другой вход которого подключен к шине переноса из (/-1)-го разряда, а другой выход узла уиравлеиия переносом соединен с одним из входов элемента Р1ЛИ, другие входы которого подключены соответственно к выходу

переноса двоичного сумматора, к выходу элемента И и к уиравляюи1ей ninne устройства, а выход элемента ИЛИ соединен с четвертым входом двоичного сумматора. Источники информации, принятые во вииманне ири экспертизе:

1.Китов А. Ii. и Кргипщкий И. А. Электронные цифровые п программирование. М., 1959, с. 159-1G4.

2.Авт. св. „YO 441562, G Об1 7/385, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Разряд двоично-десятичного сумматора | 1972 |

|

SU441562A1 |

| ДВОИЧНО-ДЕСЯТИЧНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР | 1971 |

|

SU293241A1 |

| СПОСОБЫ ВЫПОЛНЕНИЯ ЭЛЕМЕНТАРНЫХ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ (ЭВО) И УСТРОЙСТВО ИХ ОСУЩЕСТВЛЕНИЯ | 2013 |

|

RU2553221C2 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

| Устройство для сложения десятичных чисел | 1975 |

|

SU595729A1 |

| Устройство для суммирования двоично-десятичных кодов | 1977 |

|

SU684542A1 |

| Параллельный сумматор-вычитатель на элементах нейронной логики | 2020 |

|

RU2780299C2 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2246752C1 |

| Устройство для умножения (его варианты) | 1984 |

|

SU1249508A1 |

Авторы

Даты

1977-01-30—Публикация

1974-04-22—Подача