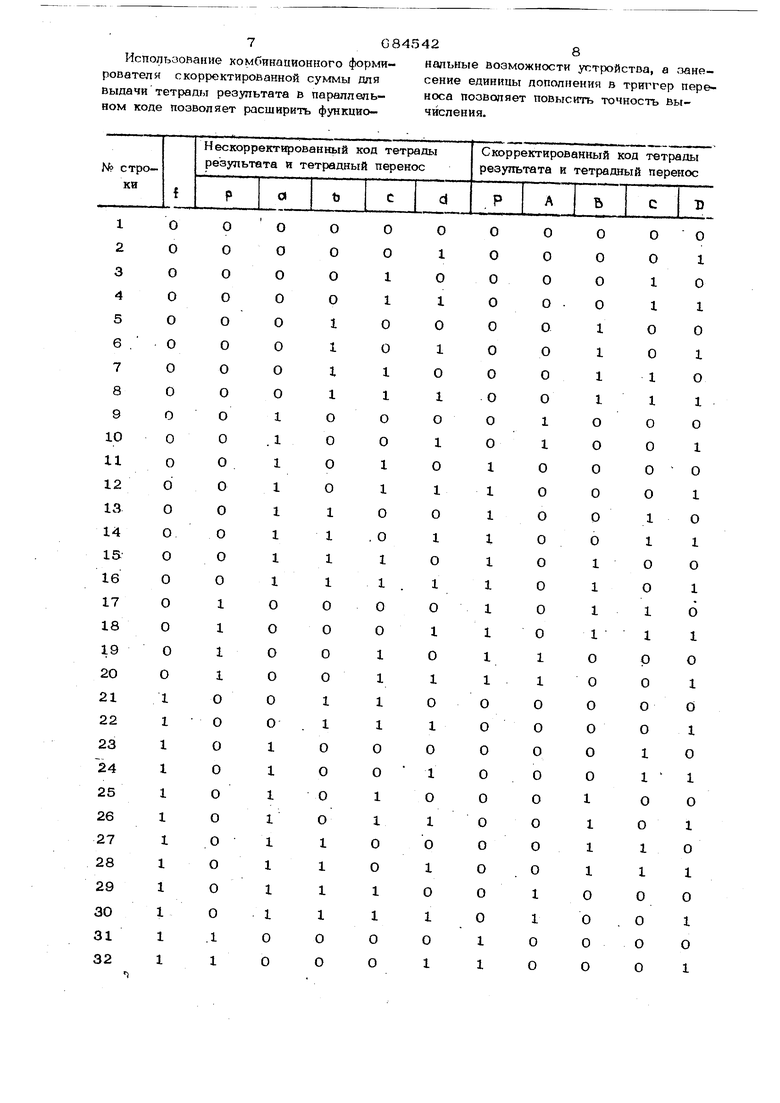

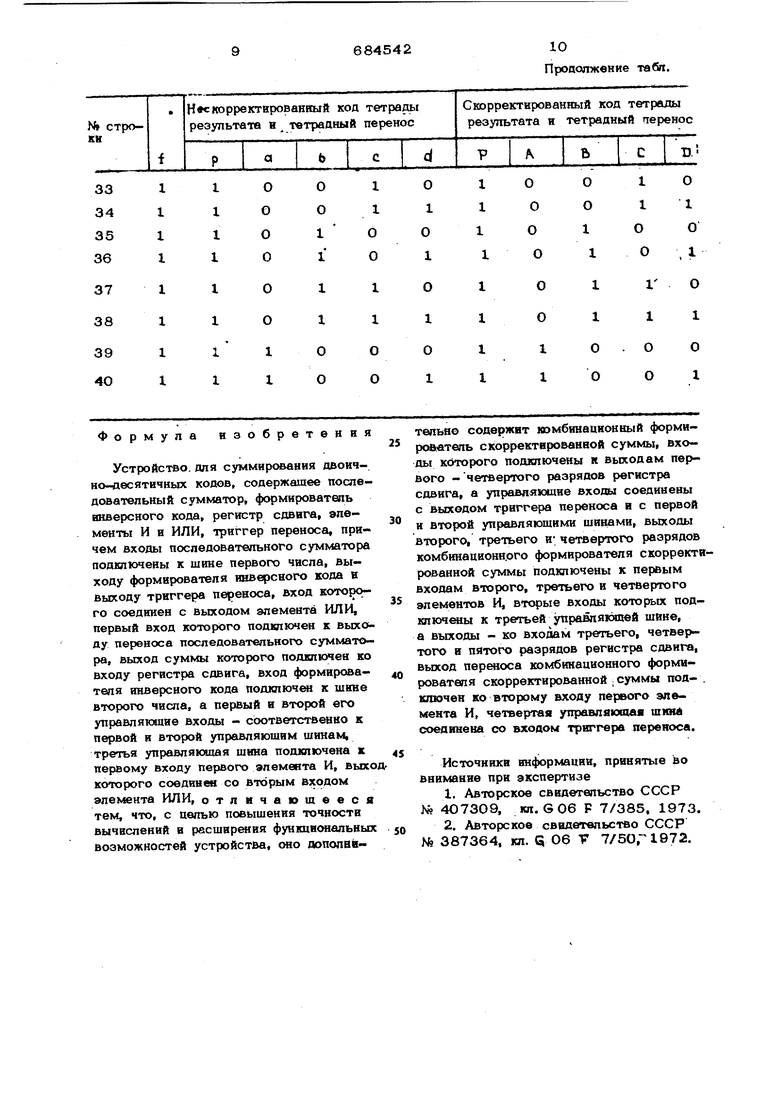

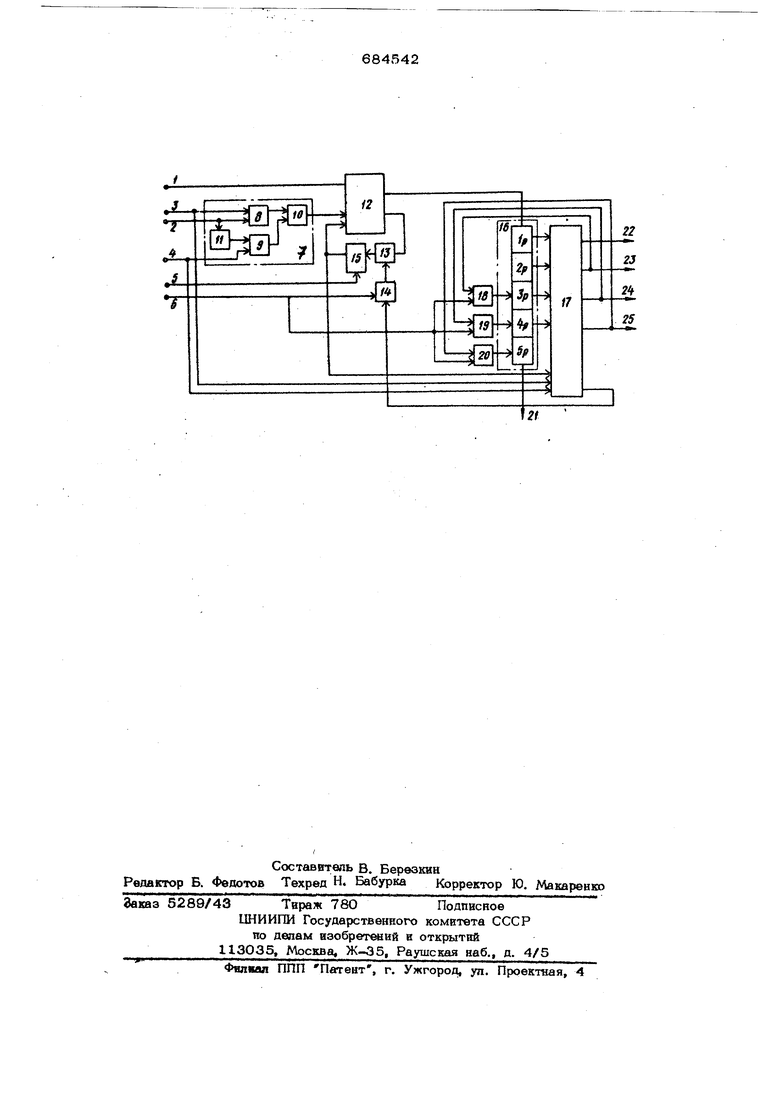

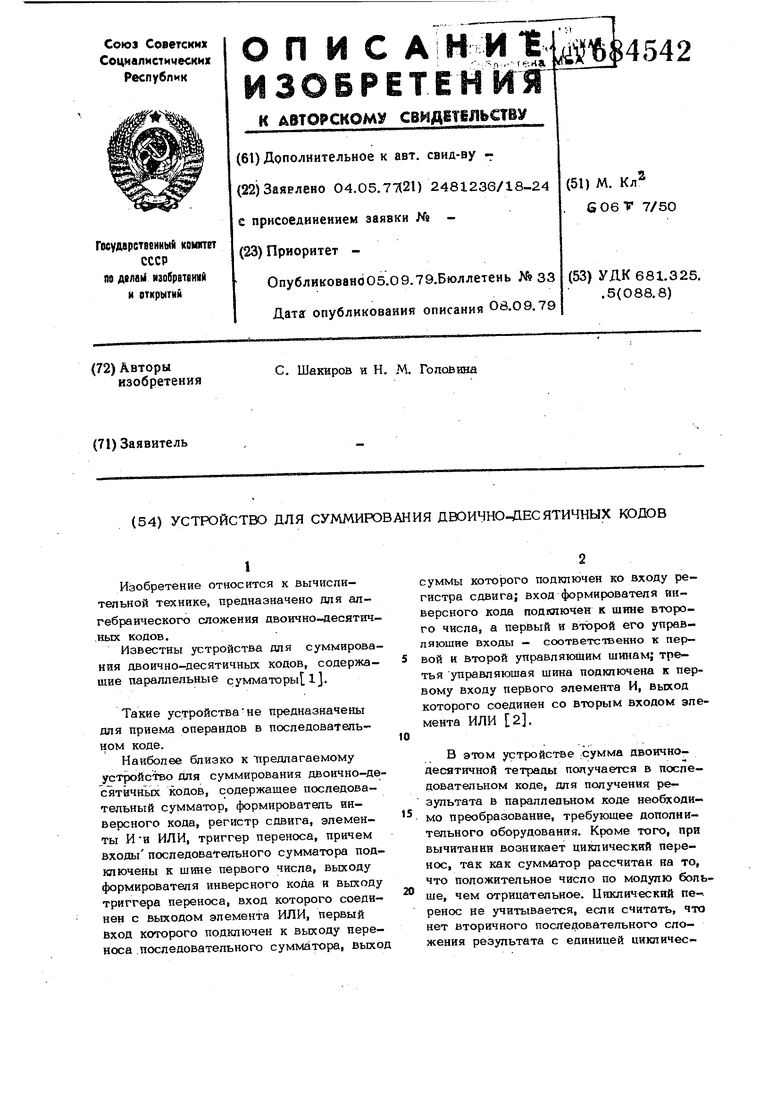

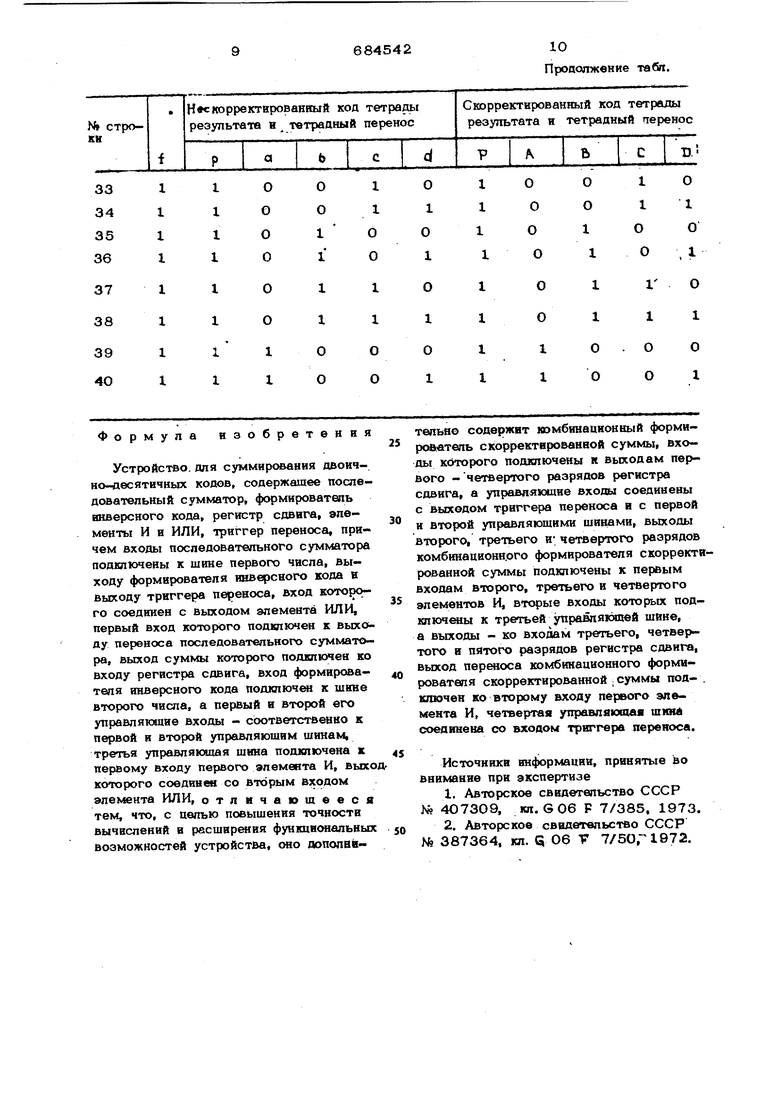

кого переноса, что снижает точность вычиспений. Цель изобретения повышение точно сти вычислений и расигирение функциональных возможностей схемы путем сов мешения коррекции с образованием последовательного кода тетрады результата сложения в параллельный код. Цель изобретения достигается тем, что в устройство введен комбинационный .формирователь скорректированной суммы входы которого тгодключены к выходам первого-четвертого разрядов регистра сдвига, а управляющие входы соединены с Выходом триггера, переноса и с первой и второй управляющими шинами. Выходы второго, третьего и четвертого раз рядов комбинационного формиров.ателя скорректированной суммы подключены к первым Входам второго, третьего и четвертого элементов И, вторые входь которых подключены к третьей управляющей шине, а выходы - ко входам третьего, четвертого и пятого разрядов регистра сдвига. Выход переноса комбинационного формирователя скорректированной суммы подключен ко второму входу первого элемента И, четвертая управляюща шина соединена со входом триггера переноса. На чертеже изображена: схема устрой cTBd. Устройство содержит входы 1 и 2 для подачи слагаемых, управляющие шин сложения 3 и вычитания 4, управляющая шина 5 для подачи импульса 1 допол нения, управляющая шина 6 для подачи импульса коррекции, формирователь инверсного кода 7 на элементах И 8 и 9, ИЛИ 10, НЕ II, последовательный сумматор 12 элементы ИЛИ 13, И 14, триггер переноса 15, регистр сдвига 16 комбинационный формирователь скорректированной суммы 17, элементы И 18- 20, шина выдачи последовательного крг да 21, шины Выдачи параллельного кода 22-25.. Два числа X и У в последовательном коде поступают на входы 1 и 2. При Выполнении сложения на управляющей шине 3 устанавливается уровень 1, а при выполнении вычитания уровень 1 устанавливается на управляющей шине 4 и в триггер переноса 15 записывается 1 дополнения, ио импульсу, поступающему на управляющую шину 5до начала вычитания. Число X поступает при ело-. жении и вычитании непосредственно на G 24 пуммотор 12 в прямом коде. Число У поступает на формирователь инверсного кода 7, а с него на вход сумматора. При вычитании число Y поступает на сумматор 12 обратным кодом двоичного представления двоично.-десятичкогр числа. Нескорректированное значение двоично-десятичной тетрады, полученное на Выходе сумматора 12, записывается последовательно за ., четыре такта в 1 - 4-й разряды регистра сдвига 16. Сигнал переноса, сформированный на сумматоре 12, записывается в триггер переноса 15 через элемент ИЛИ 13. Б пятом такте .поступает импульс коррекции, iro которому значение трех старших разрядов скорректированной тетрады с комбинационного формирователя скорректированной суммы 17 переписывается в 3-5-й разряды регистра сдвига 16 через элементы И 18-20, а значение скорректированного переноса - в триггер переноса 15 через элемент И 14. Одновременно, по этому импульсу параллельный код скорректированной тетрады Выдается из комбинационного формирователя скорректированной суммы 17 на шины 22-25. В пятом такте одновременно с переписью скорректированной тетрады с сумматора 12 в младший разряд регистра сдвига 16 записывается значение старшего разряда новой нескорректированной тетрады. Таким образом, на шину 2.1 последовательно выдается двоично-десятичный скорректированный код. Ниже приводится математическое обоснование логических уравнений Комбинационного формирователя скорректированной суммы 17, В логических уравне- ниях используются следующие буквенные обозначения: X - уменьшаемое, десятичное число;Y - Вычитаемое, десятичное число; bed - нескорректированная тетрада суммы чисел X и Y ; р - нескорректированный тетрадный перенос (перенос из тетрады в тетраду); t - признак Выполняемой операции (сложение или вычитание); БСВ - скорректированная тетрада суммы чисел X и ; Р - скорректированный тетрадный перенос. Сложение (признак i 0) двух двоичо-десятичных тетрад чисел X и Y в рямом коде Выполняется по чграгящам двоичной арифметики, в результате чего получается пятиразрядный двоичный код раьсс . Все возможные значения кода pabcd , попучаемые в результате сложения двух двоично-десятичных тетрад, приведены в левой части таблицы в строках с 1-й по 20-ю. Максимальное значение кода pabcd (10011) получается при сложении двух тетрад со значением 9 и имеющемся переносе из младшей тетрады. При значении кода jaabcd больше числа 9 нарушается двоично-десятичный код, поэтому необходима коррекция. .Откорректированные значения результата- кодРАЪСВ приведены в правой части таблицы в стр ках с 1-й по 20-ю, При выполнении вычитания (признак i. 1) тетрада числа X поступает в прямом коде, тетрада числа V - ь инверспом (поразрядное дополнение до 15 В младшую тетраду числа V добавляется единица дополнения. В результате сложения поступивших тетрад по правилам двоичной арифметики получается пятиразрядный код раЪсо.. . Рассмотрим все возможные значения кода pabc которые могут получиться при вычитании. Возможны два случая. 1) Тетрада числа X больше тетрады числа V или равна ей. Минимальное значение тетрады резул тата (строка 31 таблицы) в этом случае получается, когда значения обеих тетрад одинаковы и имеется единица переноса из младшей тетрады в данную. Наличие этой единицы переноса означает, что из тетрады числа X не было займа в младшую тетраду: 1001 (9) ЮНО (-9) 1 (дополнения или переноса) Ir OOOOj- перенос в старшую тетрад Если рассмотреть данный пример при существующем займе, то пример выйдет из- под условия X . Максимальное значение тетрады результата (строка 40 таблицы) в данном случае получается в следующем примере при условии, что не было займа из тетрады числа X 10О1 (9) mil (-0) i- ( дополнения или переноса) 1--1О01 перенос в старшую тетра2Промежуточные значения результата ежду максимальным и минимальным редставлены в левой части таблицы строках с 32-й по 39-ю. 2) Тетрада числа X меньше тетраы числа Y . Минимальное значение тетрады реультата в этом случае получается в римере , при условии, что был заем из тетрады числа X в младшую тетраду (строка 21 таблицы): ОООО (О) -V0110 (-9) сГо 110 Максимальное значение тетрады . результата получается в примере , при условии, что не Пьшо займа из тетрады числа в соседнюю младшую тетраду (строка 3U таблицы): ОООО (О) + 1110 (-1) 1 (дополнения или переноса) Промежуточные значения тетрады результата между максимальным и минимальным для рассматриваемого случая (X Y ) представлены в левой части таблицы в строках с 22-й по 29-ю. В рассматриваемом случае никогда не возникает переноса в старшую тетряду, это означает, что из старшей тетрады была занята единица. В этом случае нарушается двоично-десятичный код, поэтому необходима коррекция. Откорректированные значения тетрады результата при вычитании приведены в правой части таблицы в соответствующих строках. Из таблицы Р, - А ..Б , ,С,1) являются логическими функциями от аргументов f,p,a ,b,c ,d . После упрощения логические уравнения дляР , Л , В , С ,1 принимают следующий вид: P c(ck vabic vp(1) А 3с vet V 5b V Ьб V abk(2 §а bit vbctc V QCk vabc vSck(3) С e ek V aeic V afac(4) B d(5) При упрощении введен новый аргумент К вместо i ii р и выявлена функциональная зависимость нового аргумента от f и р К р V fр . Используемый в устройстве комбинационный формирователь скорректированной суммы реализует уравнения ( 1-5).

7084542g

Использование комбинационного форми- нальные возможности устройства, а гзанерователя скорректированной суммы длясение единицы дополнения в триггер перевыдачи тетрашл результата в параплепь-носа позволяет повысить точность выном коде позволяет расширить функцио-числения.

9

10

684542 Продолжение табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1978 |

|

SU767749A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1978 |

|

SU734685A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2402803C2 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1977 |

|

SU693369A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| Устройство для деления десятичных чисел | 1976 |

|

SU744562A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

Формула изобретения Устройство, для суммирования двоично аесятичных кодов, содержащее последовательный сумматор, формирователь инверсного кода, регистр сдвига, элементы И и ИЛИ, триггер переноса, причем входы последовательного сумматора подключены к шине первого числа, выходу формирователя инверсного кода и выходу триггера пе|реноса, вход которого соединен с выходом элемента ИЛИ, первый вход которого подключен к выходу переноса последователького сумматора, выход суммы которого подключен ко входу регистра сдвига, вход формирователя инверсного кода подключен к шине второго числа, а первый и второй его управляющие входы - соответственно к первой и второй управляюшим шинам, третья управляющая шина подключена к первому входу первого элемента И, выхо которого соединен со вторым входом элемента ИЛИ, отл ичаюшееся тем, что, с целью повышения точности вычислений и расширения функциональных возможностей устройства, оно дополввтельво содержит мамбинационный формирователь скорректированной суммы, входы которого подключены к выходам первого - четвертого разрядов регистра сдвига, а управляющие входы соединены с выходом триггера переноса и с первой и второй управляющими шинами, выходы второго, третьего и- четвертого разрядов комбинационн.ого формирователя скорректированной суммы подключены к первым входам второго, третьего и четвертого элементов И, вторые входы которых подключены к третьей управляющей шине, а выходы - ко входам третьего, четвертого и пятого разрядов регистра сдвига, выход переноса комбинационного формирователя скорректированной I суммы под-, кпючен ко второму входу первого элемента И, четвертая управляющая шюш со 1инена со входом триггера переноса. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 4О7309, кл. 606 F 7/385, 1973. 2.Авторское свидетельство СССР NO 387364, кл. Q 06 V 7/5O,-U972.

Авторы

Даты

1979-09-05—Публикация

1977-05-04—Подача