Изобретение чотносится к цифровой вычислительной технике и может быть использовано в цифровых ЭВМ.

Целью изоб)етения является унрощеиие устройства.

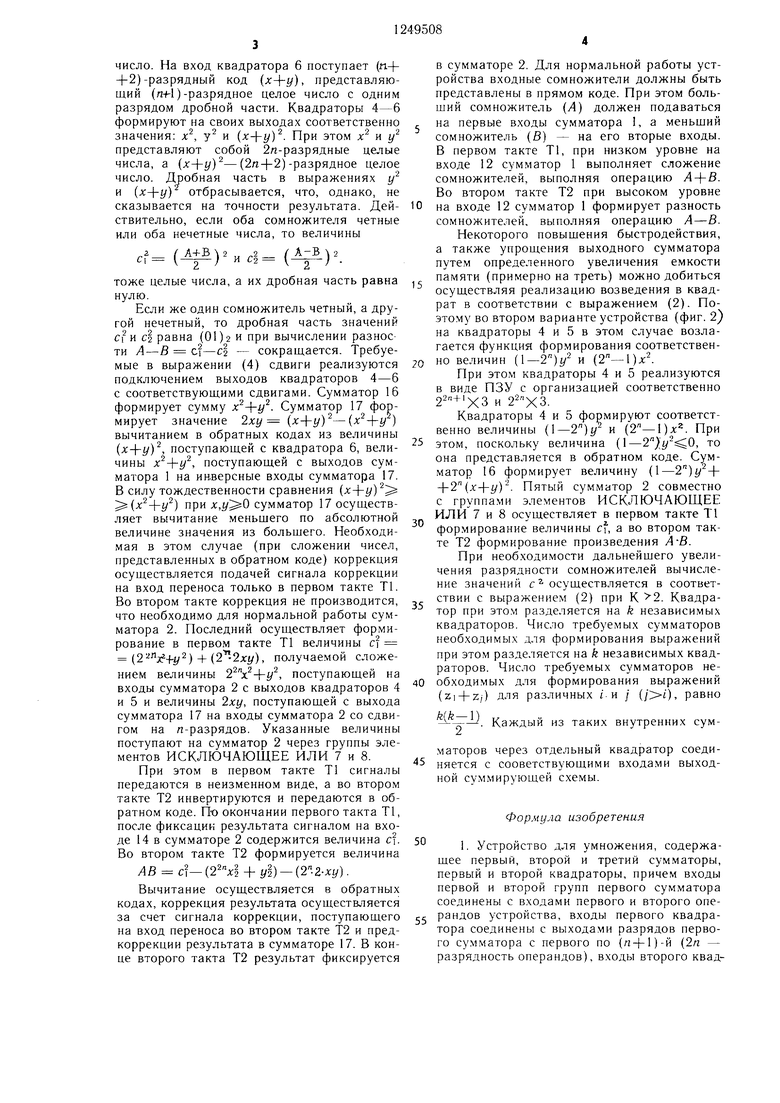

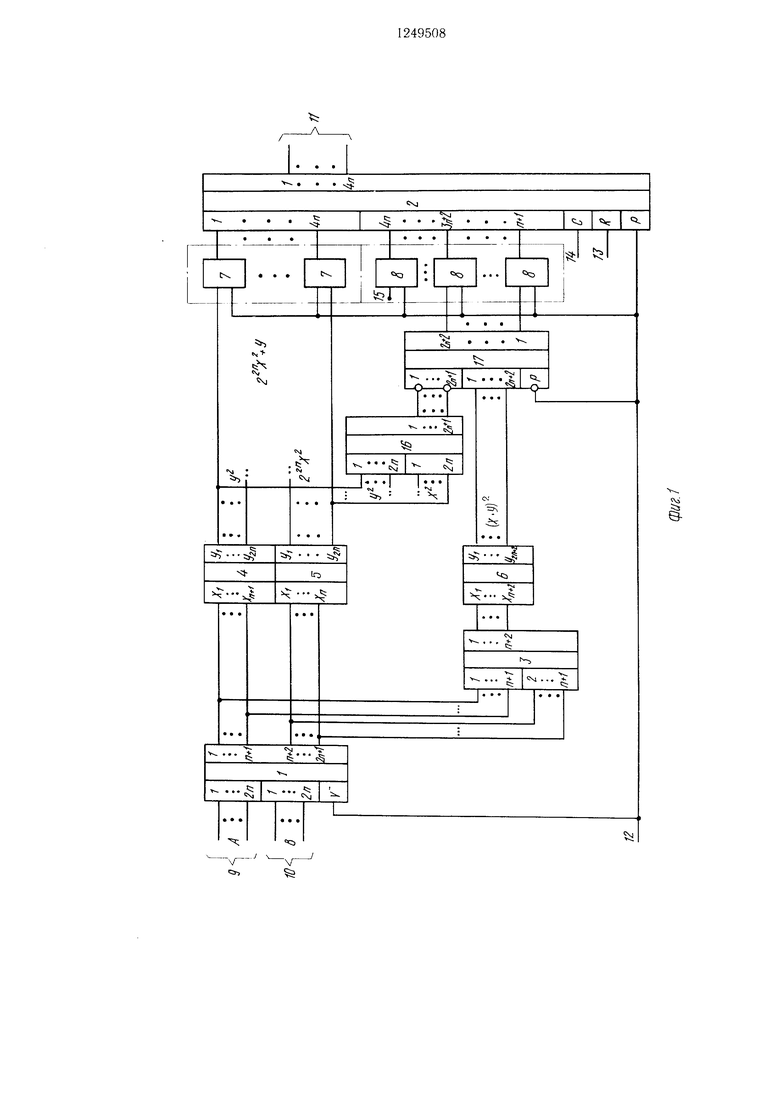

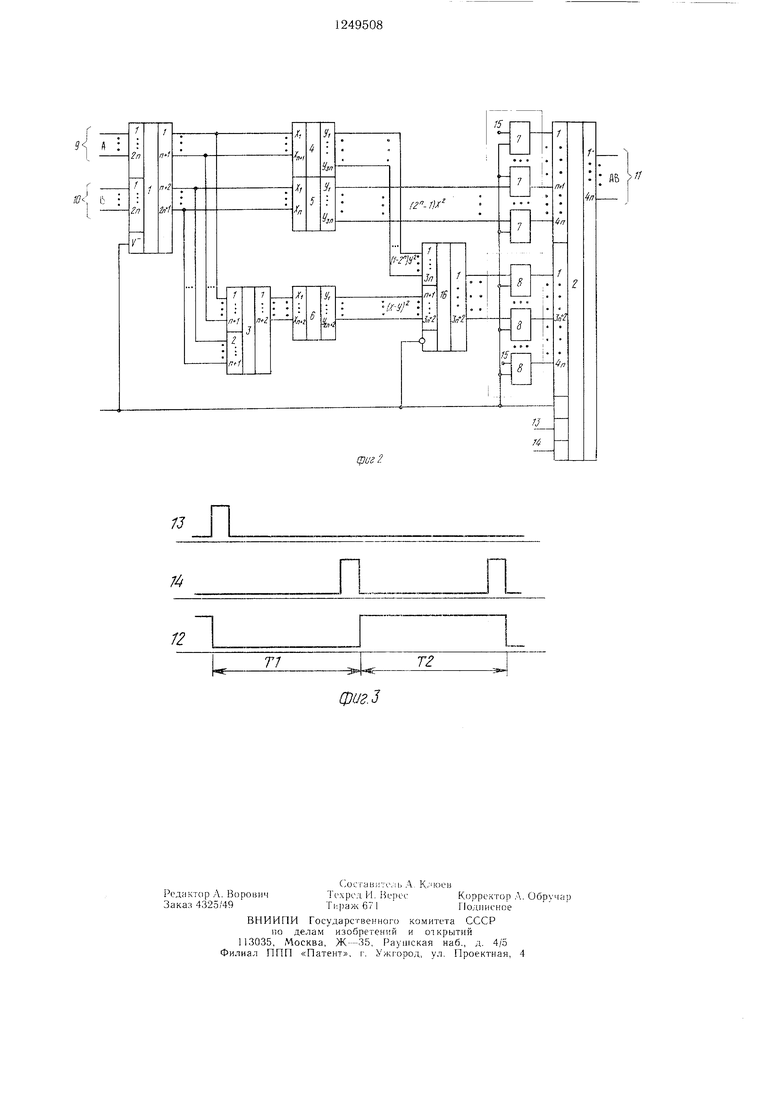

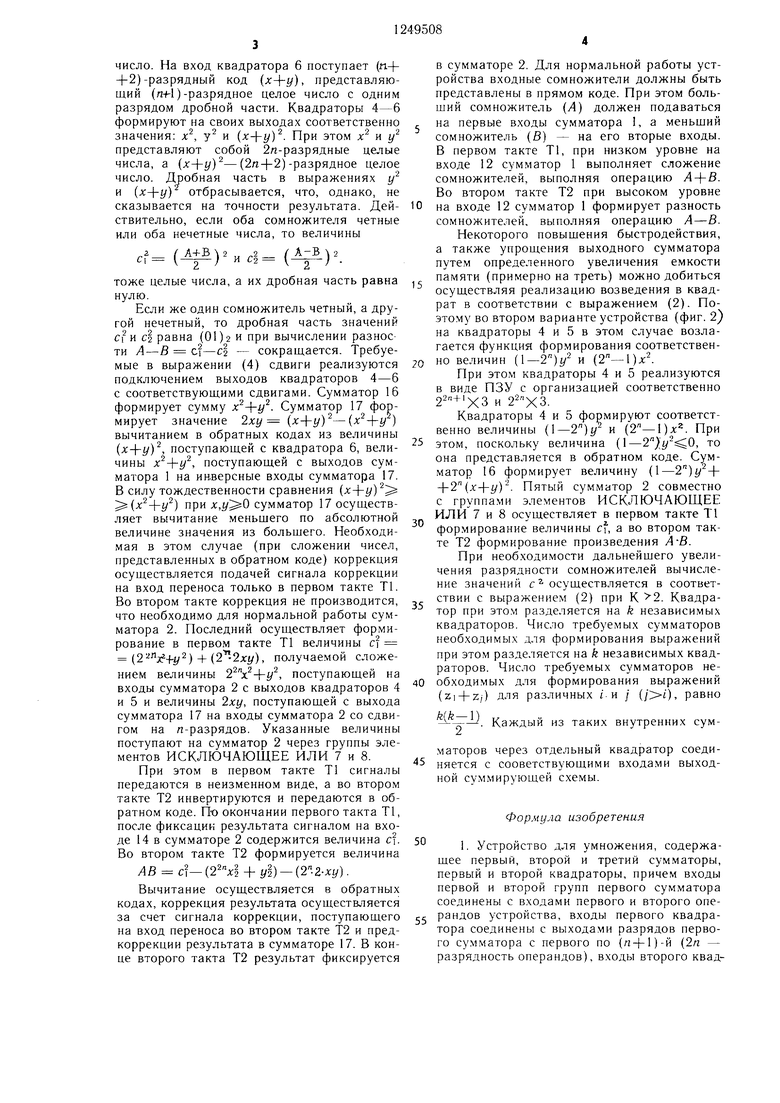

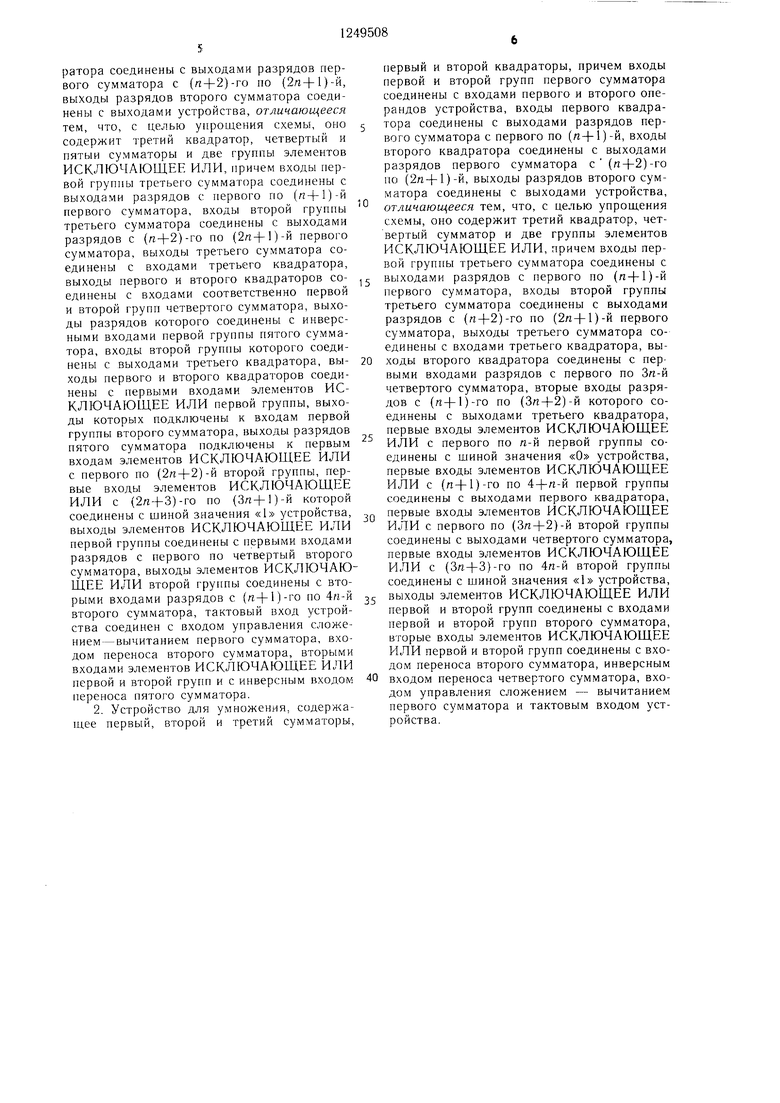

На фиг. 1 цриведеиа функциональная с.ке.ма устройства по нервому варианту; на фиг. 2 -- то же. но второму варианту; на фиг. 3 - sipeMCHHaM диаг рам.ма работы устройства.

Устройство но г ервому (фиг. ) и второму (фнг. 2) вариантам содержит сумматоры 1---3, квадраторы 4-6. группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 7 и 8, входы 9 и 10 первого и второго операндов, выходы И, тактовый вход 12, вход 13 сброса, вход 14 синхронизации, цшну 15 значения «1 и су.мматор 16.

Kpo.vie TOi O, устройство но первому варианту со.держит сумматор 17 (фиг. 1).

Сунлиость изобретения заключает ся в следующем.

Наибольшую сложность цри реализации умножения по формуле

л.й (

в случае большой разрядцосги сомножителей вызывает операция возведения в квадрат выражений

А+В

L, 1,2 -

цоскольку нри реа. -изации квадраторов в виде ПЗУ в этом случае требуются очень большие затраты памяти, разбивая значение с на /г частей по п разрядов в соответствии с выражением

При 2, обозначая х zi и г,( . имеем тождество

2();г + (x + tJ} 4- (1--2) г

и. ш в эквиваленть ой записи

с2 + 2(.:+«) + (х - + Г).

Устройство осуществляет перемножение двух т 2л-разрядных двоичных чисел. Перемножение осуществляется в соответст- 15ии с выражениями (1) и (4) в два такта. В начале первого такта Т1 (фиг. 3) сигналом на входе 13 осуществляется обнуление сумматора 2. В первом такте в соответствии с выражением (1) осуществляется вычисление величины

10

.f (+В, - V о /

0

0

5

в KOHiie такта ио.тученный результат и.м- пульсом на вхо.де 14 фиксируется в сумматоре 2. Во втором такте Т2 из полученного результата вычитается величина

«(

Полученный результат является искомым произведением А В и окончательно фикси- )уется вторым импульсом стробирования. Сомножители поступают на входы сумматора 1, функцией которого является вычисле- аие в тактах Т и Т2 соответственно суммы и разности сомножителей )| j А±В. Полученное на выходе сумматора 1 значение D рассматривается как сумма двух частей D..

2 -х представляет собой двоичный код на п-старшях. разряда.ч выходов сумматора 1 у - код на остальных младших разрядах выходов сумматора 1.

Вычисленные значения х, у поступают соответственно на входы квадраторов, а также на входы сумматора 3. Сумматор 1 формирует сумму или разность входных сомножителей .D|,2 Л±В. Однако в выражении (1) требуется значение нолусуммы и полу- )азности значения сомножителей

Л±-б 2

Деление на два для двоичного числа реализуется сдвигогл вправо па один разряд. В связи с этим результат на выходе сумматора 1 интерпретируется как

Л+В

Cl,2 - ,

Т. е. как двоичное число с 2/г-разрядной целой частью и одним разрядом дробной части. Сумматор 3 формирует значение суммы значений кодов с выходов старших и младщих разрядов выходов сумматора 1(+У). В киадргторы записаны таблицы возведения в квадрат, где каждому значению входного кода, поступающему на входы квадрато- )ов 4-6, ставятся в соответствие значения его квадрата на выходе квадраторов 4-6. На вход квадратора 4 поступает (п-|-1)- разрядное значение у, где л-разрядов составляют целую часть двоичного числа и один разряд - его дробную часть. На вход квадратора 5 поступает «-разрядное значе- 1ие А% представляющее собой целое двоичное

число. На вход квадратора 6 поступает (п-|- +2)-разрядный код {х+у} представляющий (/2-f-l)-разрядное целое число с одним разрядом дробной части. Квадраторы 4-6 формируют на своих выходах соответственно значения: x, y и (х+у). При этом х и у представляют собой 2гг-разрядные целые числа, а (х+у)-(2«4-2)-разрядное целое число. Дробная часть в выражениях I/ и ) отбрасывается, что, однако, не сказывается на точности результата. Действительно, если оба сомножителя четные или оба нечетные числа, то величины

(A)иd {)

с

2 -Z- V 2

тоже целые числа, а их дробная часть равна нулю.

Ес,ти же один сомножитель четный, а другой нечетный, то дробная часть значений cfи с равна (01)2 и при вычислении разности А-В : - сокращается. Требуемые в выражении (4) сдвиги реализуются подключением выходов квадраторов 4-6 с соответствующими сдвигами. Сумматор 16 формирует сумму . Сумматор 17 формирует значение 2j:y (;с+(/)-(x -|-i/ ) вычитанием в обратных кодах из величины (А:+У), поступающей с квадратора 6, величины , поступающей с выходов сумматора 1 на инверсные входы сумматора 17. В силу тождественности сравнения () () при j:, сумматор 17 осуществляет вычитание меньшего по абсолютной величине значения из больщего. Необходимая в этом случае (при сложении чисел, представленных в обратном коде) коррекция осуществляется подачей сигнала коррекции на вход переноса только в первом такте Т1. Во втором такте коррекция не производится, что необходимо для нормальной работы сумматора 2. Последний осуществляет формирование в первом такте Т1 величины с () + {2 -2х:у), получаемой сложением величины (-у, поступающей на входы сумматора 2 с выходов квадраторов 4 и 5 и величины 2ху, поступающей с выхода сумматора 17 на входы сумматора 2 со сдвигом на л-разрядов. Указанные величины поступают на сумматор 2 через группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 7 и 8.

При этом в первом такте Т1 сигналы передаются в неизменном виде, а во втором такте Т2 инвертируются и передаются в обратном коде, rtt) окончании первого такта Т1, после фиксации результата сигналом на входе 14 в сумматоре 2 содержится величина с. Во втором такте Т2 формируется величина

/}B ( + yi)-(2 -2xy).

Вычитание осуществляется в обратных кодах, коррекция результата осуществляется за счет сигнала коррекции, поступающего на вход переноса во втором такте Т2 и пред- коррекции результата в сумматоре 17. В конце второго такта Т2 результат фиксируется

в сумматоре 2. Для нормальной работы устройства входные сомножители должны быть представлены в прямом коде. При этом больший сомножитель (Л) должен подаваться

на первые входы сумматора 1, а меньщий сомножитель (В) - на его вторые входы. В первом такте Т1, при низком уровне на входе 12 сумматор 1 выполняет сложение сомножителей, выполняя операцию . Во втором такте Т2 при высоком уровне

на входе 12 сумматор 1 формирует разность сомножителей, выполняя операцию А-В. Некоторого повыщения быстродействия, а также упрощения выходного сумматора путем определенного увеличения емкости памяти (примерно на треть) можно добиться осуществляя реализацию возведения в квадрат в соответствии с выражением (2). Поэтому во втором варианте устройства (фиг. 2} на квадраторы 4 и 5 в этом случае возлагается функция формирования соответственно величин (1-2)/ и ()x.

При этом квадраторы 4 и 5 реализуются в виде ПЗУ с организацией соответственно и .

Квадраторы 4 и 5 формируют соответственно величины (1-2)/ и ()х. При

этом, поскольку величина (1-2), то она представляется в обратном коде. Сумматор 16 формирует величину (1-2)гy + + 2 (). Пятый сумматор 2 совместно с группами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 7 и 8 осуществляет в первом такте Т1 формирование величины Сь а во втором такте Т2 формирование произведения А-В.

При необходимости дальнейшего увеличения разрядности сомножителей вычисление значений с осуществляется в соответствии с выражением (2) при К . Квадратор при этом разделяется на k независимых квадраторов. Число требуемых сумматоров необходимых для формирования выражений при этом разделяется на k независимых квадраторов. Число требуемых сумматоров необходимых для формирования выражений (zi + z/) для различных /-и / ( равно

ff/h1

. Каждый из таких внутренних сумматоров через отдельный квадратор соеди- няется с сооветствующими входами выходной суммирующей схемы.

Формула изобретения

1. Устройство для умножения, содержащее первый, второй и третий сум.маторы, первый и второй квадраторы, причем входы первой и второй групп первого сумматора соединены с входами первого и второго опе- рандов устройства, входы первого квадратора соединены с выходами разрядов первого сумматора с первого по (п+П-й (2л - разрядность операндов), входы второго квад

ратора соединены с выходами разрядов первого сумматора с ()-го по (2п--|-1)-й, выходы разрядов второго сумматора соединены с выходами устройства, отличающееся тем, что, с целью упрощения схемы, оно содержит третий квадратор, четвертый и пятый сумматоры и две группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, причем входы первой группы третьего сумматора соединены с выходами разрядов с первого по (п-|-1)-й первого сумматора, входы второй группы третьего сумматора соединены с выходами разрядов с (п+2)-го по (2п+1)-й первого сумматора, выходы третьего сумматора соединены с входами третьего квадратора, выходы первого и второго квадраторов со- единены с входами соответственно первой и второй групп четвертого сумматора, выходы разрядов которого соединены с инверсными входами первой группы пятого сумматора, входы второй группы которого соединены с выходами третьего квадратора, вы- ходы первого и второго квадраторов соединены с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы, выходы которых подключены к входам первой группы второго сумматора, выходы разрядов пятого сумматора подключены к первым входам элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с первого по (2п-(-2)-й второй группы, первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с ()-го по (Зп+)-й которой соединены с шиной значения «1 устройства, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы соединены с первыми входами разрядов с первого по четвертый второго сумматора, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы соединены с вторыми входами разрядов с (я+1)-го по 4п-й второго сумматора, тактовый вход устройства соединен с входом управления сложением- вычитанием первого сумматора, входом переноса второго сумматора, вторыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой и второй групп и с инверсным входом переноса пятого сумматора.

2. Устройство для умножения, содержащее первый, второй и третий сумматоры.

первый и второй квадраторы, причем входы первой и второй групп первого сумматора соединены с входами первого и второго операндов устройства, входы первого квадратора соединены с выходами разрядов первого сумматора с первого по (п-|-1)-й, входы второго квадратора соединены с выходами разрядов первого сумматора с (п+2)-го по (2п+1)-й, выходы разрядов второго сумматора соединены с выходами устройства, отличающееся тем, что, с целью упрощения схемы, оно содержит третий квадратор, четвертый сумматор и две группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, причем входы первой группы третьего сумматора соединены с выходами разрядов с первого по (п-4-1)-й первого сумматора, входы второй группы третьего сумматора соединены с выходами разрядов с (п+2)-го по (2п+1)-й первого сумматора, выходы третьего сумматора соединены с входами третьего квадратора, выходы второго квадратора соединены с первыми входами разрядов с первого по 3«-й четвертого сумматора, вторые входы разрядов с (п+1)-го по (Зи+2)-й которого соединены с выходами третьего квадратора, первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с первого по п-й первой группы соединены с щиной значения «О устройства, первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с (п+1)-го по первой группы соединены с выходами первого квадратора, первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с первого по (Зп-|-2)-й второй группы соединены с выходами четвертого сумматора, первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с {Зп- + 3)-го по 4п-й второй группы соединены с щиной значения «1 устройства, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой и второй групп соединены с входами первой и второй групп второго сумматора, вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой и второй групп соединены с входом переноса второго сумматора, инверсным входом переноса четвертого сумматора, входом управления сложением - вычитанием первого сумматора и тактовым входом устройства.

фиг. J

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой преобразователь координат | 1985 |

|

SU1257638A1 |

| Устройство для деления | 1990 |

|

SU1746378A1 |

| Цифровой преобразователь координат | 1983 |

|

SU1163322A1 |

| Квадратор | 1981 |

|

SU1010620A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1290307A1 |

| Устройство для возведения в квадрат,извлечения квадратного корня,умножения и деления | 1981 |

|

SU1059571A1 |

| Устройство для умножения | 1989 |

|

SU1658148A1 |

| Устройство для деления | 1990 |

|

SU1728860A1 |

| Последовательное множительное устройство | 1980 |

|

SU888110A1 |

| Устройство для деления последовательных чисел | 1987 |

|

SU1462298A1 |

Изобретение относится к цифровой вычислительной технике. Целью изобретения является упрощение устройства. Устройство содержит сумматоры, квадраторы и элементы ИСКЛЮЧАЮЩЕЕ ИЛИ. Работа устройства основывается на тождестве: АВ (-fS) (4-б)/2 где табличная операция умножения заменяется табличным возведением в квадрат. Отличительным свойством устройства является возведение В квадрат в соответствии с тождеством: (Л±В;/2 2 С2 ()2 22 A 2+Y2-t- +2( + Y)2-2(;;:2-Y, где А и У - соответственно старшие и младшие разряды С. При этом умножение производится за два такта: в первом такте формируется значение (Л+в), а во втором - значение (Л-j5)/2p и само произведение, равное разности этих значений. 2 с. п. ф-лы, 3 ил. о. ьо 4; ;о ел

| Григорьев В | |||

| Л | |||

| Программное обеспечение микропроцессорных систем | |||

| М.: Энер- гоиздат, 1983, с | |||

| Приспособление, увеличивающее число оборотов движущихся колес паровоза | 1919 |

|

SU146A1 |

| Полупроводниковые запоминающие устройства и их применение./Под ред | |||

| А | |||

| Ю | |||

| Го донова | |||

| М.: Радио и связь, 1981, с | |||

| . | |||

Авторы

Даты

1986-08-07—Публикация

1984-07-23—Подача