гистра 1. Далее происходит сдвиг на один разряд вправо хранящейся информации в динамическом регистре 1 и в регистре 2 тетрады. При этом выходной сигнал последовательного сумматора 3 заносится в динамический регистр 1, а сигнал с выхода динамического регистра 1 запоминается в освобожденном от информации четвертом разряде регистра 2 тетрады на один такт, что эквивалентно умножению числа на два. Во втором такте преобразования сигналом, поступающим по шине 7, элемент И 4 открывается, на входы последовательного сумматора 3 поступают через открытый элемент И 6 код очередного разряда тетрады преобразуемого числа и через открытый элемент И 4 - код с выхода четвертого разряда регистра 2 тетрады, в котором хранится результат умножения числа на два. Сумма, образованная в результате сложения, с выхода последовательного сумматора 3 поступает на вход динамического регистра 1. Происходит второй сдвиг вправо на один разряд информации регистра 1 и 2. Третий такт работы устройства аналогичен второму. В четвертом такте сигналом, поступающим по шине 7, открывается элемент И 5. При этом на входы последовательного сумматора 3 с регистра 2 тетрады поступают: код с выхода четвертого разряда через элемент И 4 (результат умножения числа на два), код с выхода второго разряда через элемент И 5 (результат умножения числа на восемь) и код очередного (старшего) разряда тетрады преобразуемого числа через элемент И 6. Происходит четвертый сдвиг вправо.

В пятом и во всех последующих тактах, общее число которых равно числу разрядов преобразованного числа, сигналом по шине 7 элемент И 6 закрывается и на последовательный сумматор 3 поступают коды с выходов регистра 2 тетрады через элементы И 4, 5 и происходит в каждом такте сдвиг информации в регистрах I и 2 на один разряд вправо. Вследствие этого в динамическом регистре 1 оказывается число равное An-lQ+An-i, где АИ - разряды двоично-десятичного числа.

В следующем цикле в регистр 2 тетрады поступает очередная тетрада преобразуемого числа и работа устройства повторяется аналогично первому циклу. Процесс преобразования заканчивается прибавлением младщего разряда десятичного числа к содержимому динамического регистра 1, умноженному на десять.

Результат преобразования хранится в регистре 1.

Предлагаемое изобретение уменьшает время преобразования за счет того, что процессы умножения кода динамического регистра 1 на десять и сложения этого кода с кодом очередной тетрады преобразуемого числа совмещены во времени и выполняются в одном и том же цикле. Время преобразования Т определяется как:

,T fiгде t - длительность одного цикла;

п - количество разрядов двоично-десятичного числа.

При равных длительностях циклов по сравнению с известными аналогичными преобразователями предлагаемое устройство имеет в

2л 1 раз выше быстродействие.

Формула изобретения

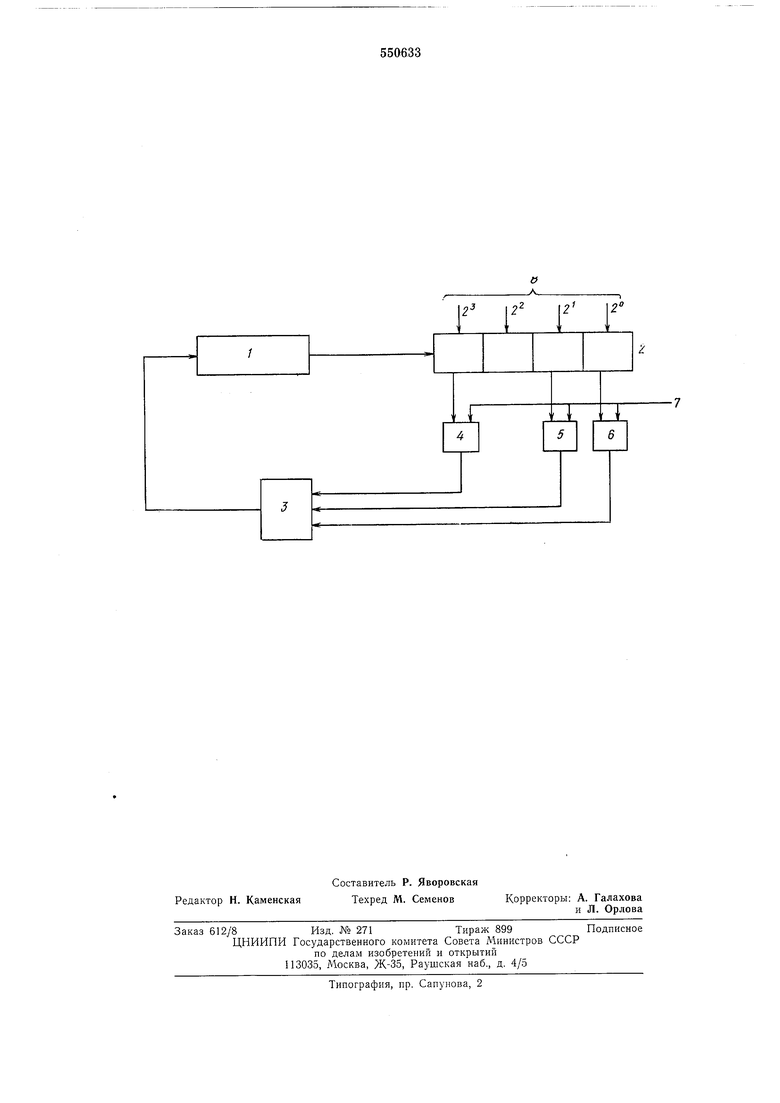

Устройство для преобразования двоичнодесятичных чисел в двоичные, содержащее динамический регистр, последовательный сумматор, выход которого соединен со входом динамического регистра, и регистр тетрады, отличающееся тем, что, с целью повышения быстродействия, оно содержит шину сигналов

управления и три элемента И, выходы которых соединены с соответствующими входами последовательного сумматора, первые входы элементов П соединены соответственно с выходами первого, второго и четвертого разрядов регистра тетрады, а вторые входы соединены с шиной сигналов управления, вход четвертого разряда регистра тетрады соединен с выходом динамического регистра.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР №269598 М. КЛ.2 G 06 F 5/02, опубл. 1968 г.

2.Авторское свидетельство СССР № 329525 М. КЛ.2 G 06F 5/02, опубл. 1970 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1978 |

|

SU752323A1 |

| Преобразователь правильной двоичной дроби в двоично-десятичную дробь и целых двоично-десятичных чисел в двоичные | 1978 |

|

SU734669A1 |

| Преобразователь правильной двоично-десятичной дроби в двоичную дробь и целых двоичных чисел в двоично-десятичные | 1978 |

|

SU741260A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1978 |

|

SU734670A1 |

| Устройство для преобразования двоичныхчиСЕл B дВОичНО-дЕСяТичНыЕ | 1979 |

|

SU809153A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU699520A1 |

| Преобразователь целых двоично- десятичных чисел в двоичные | 1978 |

|

SU750478A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1976 |

|

SU572781A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1978 |

|

SU767749A1 |

Авторы

Даты

1977-03-15—Публикация

1975-10-03—Подача