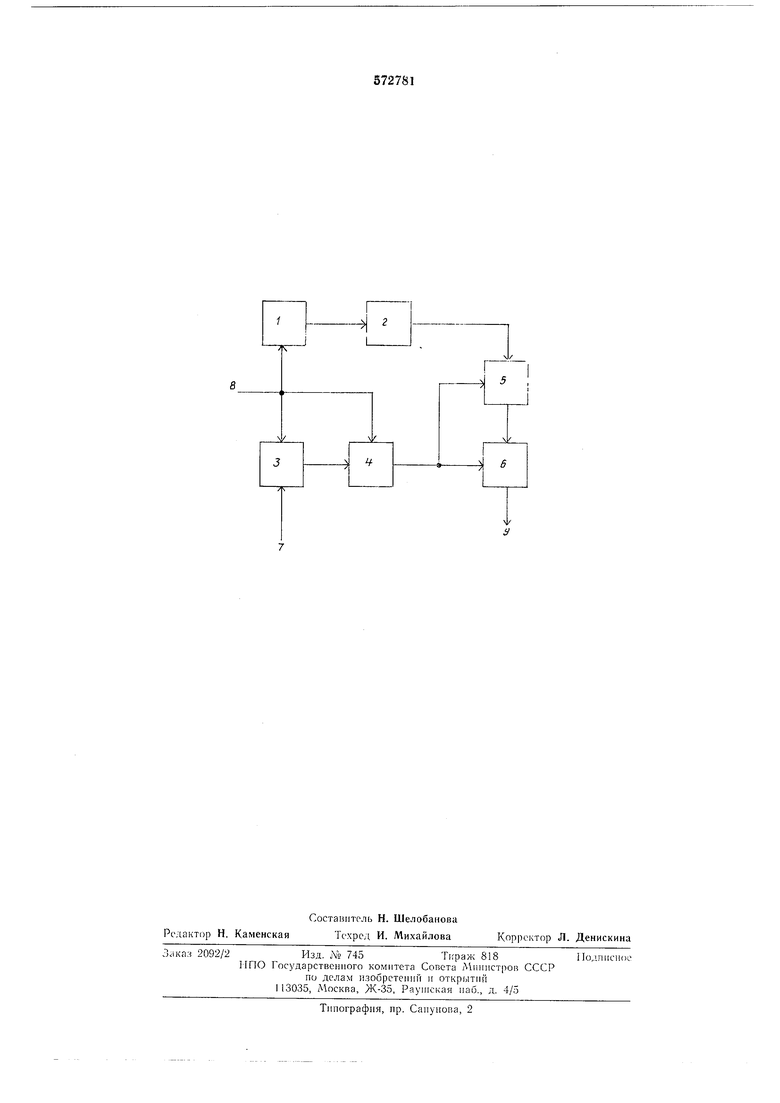

ды, блок управления преобразованием 4, сдвигатель 5, накапливающий двоичный параллельный сумматор 6.

Позициями 7, 8, 9 ободначены соответственно вход двоично-десятичных разрядов числа, управляющая шина и выход устройства.

Принцип работы преобразователя заключается в следующем.

Управляющий импульс, поступающий в каждом цикле на шину 8, записывает вводимый двоично-десятичный разряд преобразуемого числа в регистр 3 тетрады и запускает в работу блок управления преобразованием 4. Этот же управляющий импульс для данного разряда k переводит переключатель эквивалентов 1 на считывание из блока 2 соответствующего эквивалента (10+/г).

Количество двоичных эквивалентов определяется разрядностью десятичных чисел. Выбранный двоичный эквивалент поступает -параллельным кодом на вход сдвигателя 5 и используется далее в качестве сла гаемого в накапливающем сумматоре 6, формирующем двоичный код чисел. Сдвигатель 5 s частном случае реализован по схеме четырехвходового коммутатора для каждого двоично1го разряда, на информационные входы которого заведены соответствующие разряды двоичного эквивалента, дающие на выходе схемы по сигналам блока управления 4 параллельный код двоичного эквивалента без сдвига или со сдвигом кода на 1, 2 или 3 разряда в сторону старших разрядов. Блок управления 4, производя анализ содержимого четырех разрядов регистра 3 тетрады, вырабатывает в каждом такте преобразования импульсы управления сдвигателем 5, служащие одновременно сигналами сложения сумматору 6. Наличию логической единицы в четвертом (старшем) разряде регистра 3 соответствует импульс сдвига ва 3 разряда (т.е. умножение двоичного эквивалента на 8),наличию единицы в третьем разряде соответствует импульс сдвига на 2 разряда (умножение на 4), во втором разряде- имлульс сдвига на 1 разряд (умножение на 2), в первом (младше.м разряде) -импульс суммирования двоичного эквивалента без сдвига. Так как код одного двоично-десятичного разряда содержать не более трех двоичных единиц, то цикл преобразования одного двоично-десятичного разряда состоит из трех тактов, в течение которых суммируется до девяти кодов одного двоичного эквивалента.

В результате этого число тактов преобразования сводится к минимуму. Вслед за первы.м

десятичным разрядом точно так же за один цикл, состоящий из трех тактов, происходит преобразование каждого последующего двоично-десятич ного разряда исходного числа. При

этом для каждого нового цикла считывается из блока 2 очередной двоичный эквивалент (10±й)э. Так продолжается до тех пор, пока не будут преобразованы все двоично-десятичные разряды исходного числа, а в сумматоре

6 не сфор.мируется искомое двоичное число, которое считывается с выхода 9.

Предлагаемый преобразователь двоично-десятичных чисел в двоичные выгодно отличается от указанного прототипа, так как при сохранившейся простоте схемы устройства время -перевода как правильных и смешанных дробей, так и целых чисел уменьшается до значения Qkt и не зависит от количества двоичных разрядов, что повышает быстродействие

преобразователя и расширяет возможность его применения.

Формула изобретения

Преобразователь двоично-десятичных чисел в двоичные, содержащий регистр тетрады и переключатель эквивалентов, входы которых соединены с управляющей шиной, а выход переключателя эквивалентов соединен со входом

блока хранения двоичных эквивалентов десятичных чисел, отличающийся тем, что, с целью повышения быстродействия, в него введены блок управления преобразованием, сдвигатель и накапливающий двоичный параллельный сумматор, причем первый и второй входы блока управлевия преобразованием соединены соответственно с управляющей шиной и выходом регистра тетрады, а выход блока управления преобразованием подключен к первому входу сдвигателя и «о входу накапливаюше го двоичного параллельного сумматора, второй вход сдвигателя соединен с выходом блока хранения двоичных эквивалентов десятичных чисел, а выход сдвигателя подключен

ко второму входу накапливающего двоичного параллельного сумматора, выход которого является выходом устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 331382, кл. G 06F 5/02, 1969.

2.Авторское свидетельство СССР № 329525, кл.аОбР, 5/02,4970.

3.Ав торское свидетельство СССР № 473179, кл. G QGF 5/02, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода смешанных чисел в двоично-десятичный код | 1975 |

|

SU577524A1 |

| Преобразователь двоичного кода смешанных чисел в двоично-десятичный код | 1976 |

|

SU714391A2 |

| Преобразователь двоичного кода сме-шАННыХ чиСЕл B дВОичНО-дЕСяТичНый КОд | 1978 |

|

SU809149A2 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1300640A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1982 |

|

SU1048469A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый | 1979 |

|

SU798800A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1978 |

|

SU752323A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1978 |

|

SU734670A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1979 |

|

SU860053A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

Авторы

Даты

1977-09-15—Публикация

1976-04-05—Подача