1

Изобретение относится к области цифровой вычислительной техники... .

Известна .цифровая вычислительная система, содержащая коммутаторы, которые соединены с шинами номера коммутатора, номера внешнего- устройства, трансляции, связи с внешними устройствами, запроса коммутатора и разрешения занроса комцмутатора, и процессор, соединенный с коммутаторами посредством этих шин (1).

Наиболее близким техническим решением к данному изобретению является цифровая вычислительная система, которая содержит коммутаторы, соответствуюшие входы которых подключены к шине номера коммутатора, шине номера внешнего устройства, шине траислящии, шине связи с внешним устройством и шине запроса внешнего устройства, а соответстсвуюш,ие выходы соединены с шиной запроса коммутатора, шиной за)проса приоритетного внешнего устройства, шиной трансляции, шиной выборки внешнего устройства и соответствуюш;ей шиной разрешения запроса, соединяющей каждый коммутатор со всеми последующими коммутаторами, и процессор, подключенный к шине запроса приоритетного внешнего устройства, шине запроса коммутатора, шине номера внешнего устройства и шине,-номера коммутатора, и соединенный двусторон-. ней шиной обмена с одним из д оммутаторО:В,

каждый Из которых содержит блок управления, .первый выход которого соединен с первым входом блока номера коммутатора, второй вход которого по.дключен ко входу «Номер коммутатора коммутатора, а первый выход соединен с выходом «Запрос коммутатора коммутатора, второй выход блока управления соединен с первыми входа:ми блока выборки внешних устройств и блока спнхронизации запросов, второй вход которого подключен ко входу «Разрешение запроса коммутатора, а первый выход соединен с выходом «Разрешение запроса коммутатора, третий выход блока управления соединен со

вторым входом блока выборки внешних устройств, третий вход которого подключен ко входу «Номер внешнего устройства коммутатора, а выход соединен с выходом «Выборка внешнего устройсгва ком1мутатора,

вход и выход связи с внешними устройствами которого соединены с первыми входам и выходом блока связи с внешними устройствами, второй вход которого подключен ко второму выходу блока номера коммутатора,- вход

«Запрос внешнего устройства коммутатора соединен с первым входом блока приоритета, выход которого соединен с выходом «Запрос приоритетного внешнего устройства коммутатора, и с третьим входом блока спнхронизации запросов, второй выход которого соединен со вторым входом блока приоритета и с третьим входом блока номера коммутатора (2).

Известная цифровая вычислительная система не допускает гибкого иаменения количества внешних устройств и обеспечивает обмен информацией без участия процессо-ра лишь 1между фи ксированным количеством .внешних устройств.

Цель изобретения - расширение функциональных возможностей цифровой вычислительной системы.

Это достигается тем, что в предлагаемой цифровой -вычислительной системе каждый коммутатор содержит блок трансляции, блок синхронизации трансляции и блок организации параллельного обмена, .соответствующие ВХО.ДЫ которого (Подключены ко второму выходу блока управления, входу «Запрос внешнего устройства коммутатора и второму выходу блока связи с внешними устройстеами, четвертый вход которого подключен к первому выходу блока синхронизации трансляди,и, второй выход которого соединен со входом блока трансляции, а первый вход (под.ключен ко второму выходу блока управления, вход н выход «Трансляция коммутатора соединены с соответствуюш,ими входом и выходом блока связи с внешними устройства-ми, блока синхронизации трансляции, блока синхронизации запросов и блока трансляции, соответствуюш,ие вход и выход которого подключены .ко входу и выходу «Обмен коммутатора; кроме того блок синхролизации запросов содержит элементы И, ИЛИ, НЕ и триггер разрешения запросов, выход которого соединен с первым управляющим выходом блока синхронизации запросов, входы разрешения запроса которого соединены с соответствующими входами первого элемента И, соответствующий вход которого через элемент ИЛИ оодключен .ко входам запроса внешнего устройства блока синхронизации запросов, а выход соединен со входом элемента НЕ, первым входом второго элемента И и вторым управляющим выходом блока синхронизации запросов, выход элемента НЕ соединен с первым входом третьего элемента И и выходом разрешения запроса блока синхронизации запросов, вход сигнала синхронизации которого соединен со вторыми входами второго и третьего элементов И, выходы которых соединены с соответствующими входами триггера разрешения запросов, а также тем, что блок организации параллельного обмена содержит элементы И и ИЛИ, элементы задержки, схему пуска, триггер конца обмена, триггер управления пуском и схему сигналов обмена, выход которой соединен с выходом обмена блока организации параллельного обмена, первый вход конца работы устройства вывода которого через первый элемент ИЛИ, подключенный вторым входом к первому входу исключения внешнего устройства блока организации параллельного обмена, соединен с первым входом первого элемента И, подключенным вторым входом ко входу «Конец работы устройства ввода 5 блока организации параллельного обмена, второй вход конца работы устройства вывода Которого через второй элемент ИЛИ, подключенный вторым входом ко iBTOpOiMy входу исключения внещнего устройства блока организации параллельного обмена, соединен с третьим входом первого элемента И, выход которого соединен с первым входом схемы пуска, второй вход которой подключен ко входу автономного пуска блока организации 15 параллельного обмена, первый и второй входы исключения внешнего устройства которого через третий и, соответственно, четвертый элементы ИЛИ, .подключенные вторыми входами к первому и, -соответственно, второму

0 входам запроса блока организации параллельного обмена, соединены с первым и вторым входами второго элемента И, входы останова и прекращения работы ввода блока организации параллельного обмена через ня25 тый элемент ИЛИ -соединены с единичным входом триггера конца обмена, нулевой вход которого подключен к выходу схемы пуска, а выход соединен с первыми входами третьего и четвертого элементов И, выход последнего

0 из которых соединен с первым вхо.дом схемы сигналов обмена, второй вход которой подключен к выходу пятого элемента И, а выход сюединен со вторым входом третьего элемента И, выход которого соединен с выходом конца вьшода блока организаций параллельного обмена, вход запроса вводного устройства которого соединен с первым входом пятого элемента И, выход второго элемента И соединен со вторыми входами четвертого и пятого элементов И и первым входом шестого элемента И, выход которого соединен с третьи/м входом схемы иуска, выход которой соединен с первыми входами седьмого и восьмого элементов И, выходы

5 которых соединены, соответственно, с выходом пуска устройства ввода и выходом пуска устройства вывода блока организации параллельного обмена :непосредствен«о, а с нулевым и единичным входом триггера управления пуском - через соответствующие элементы задержки, единичный выход триггера управления пуск-ом соединен со вторыми входами шестого и седьмого элементов И, а его пулевой выход соединен со вторым входом

5 восьмого элемента И.

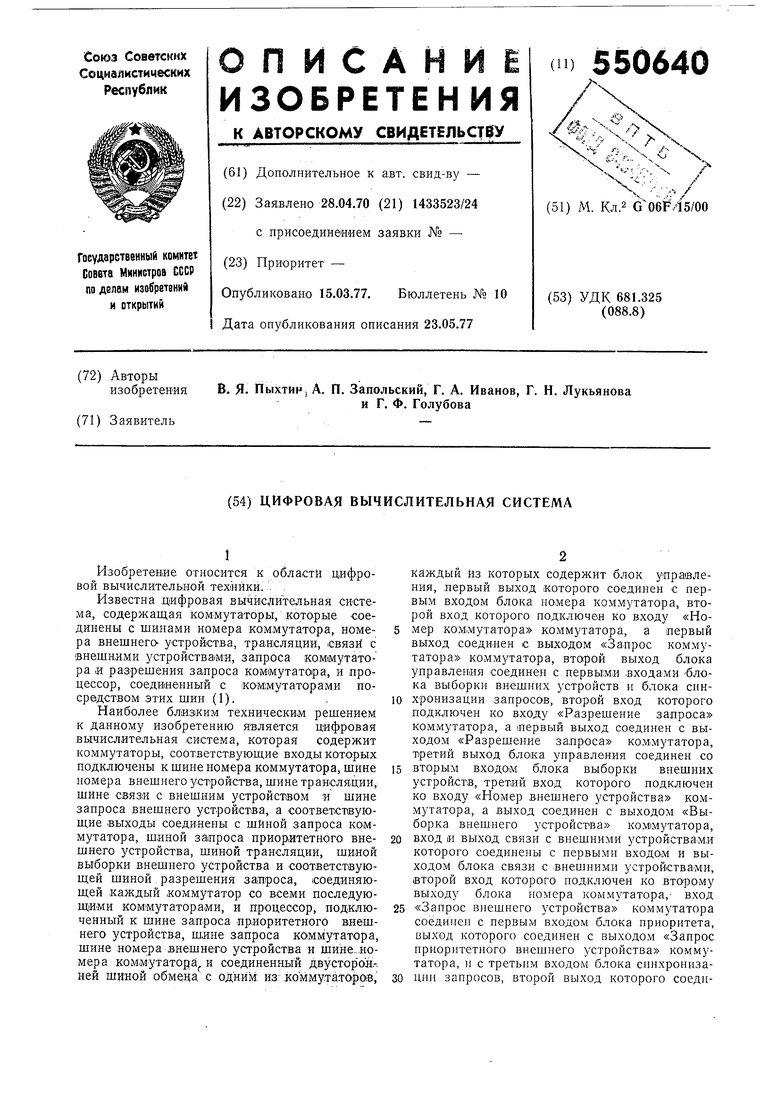

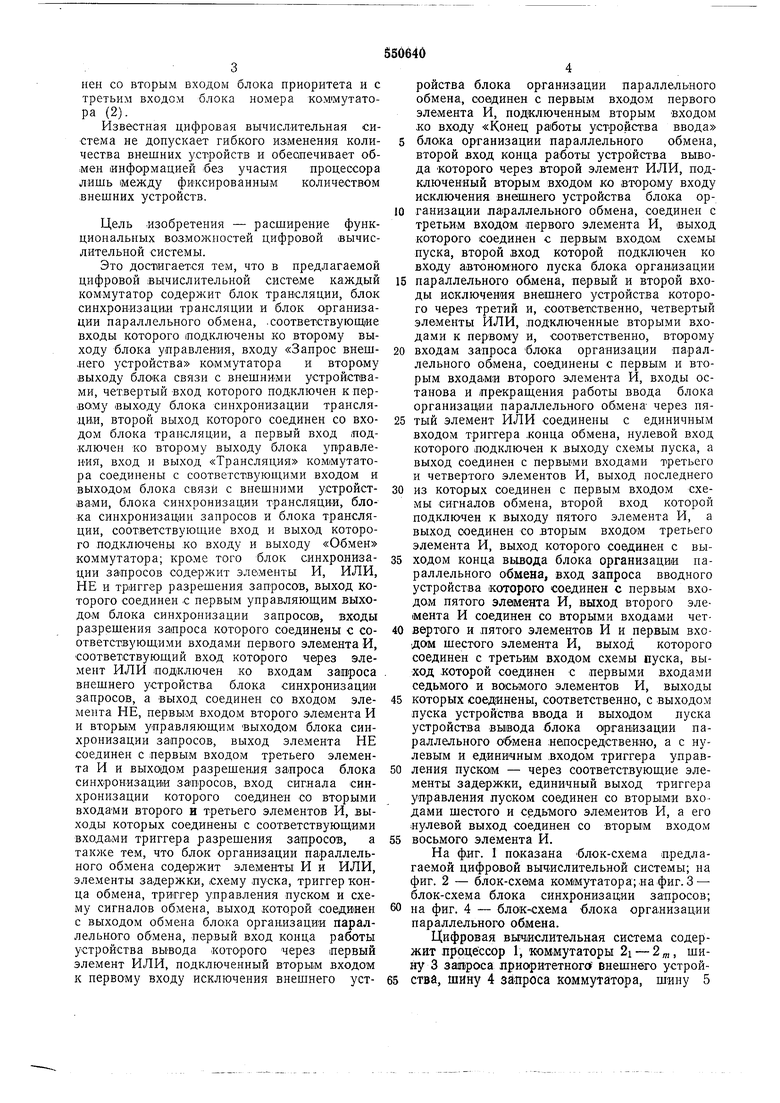

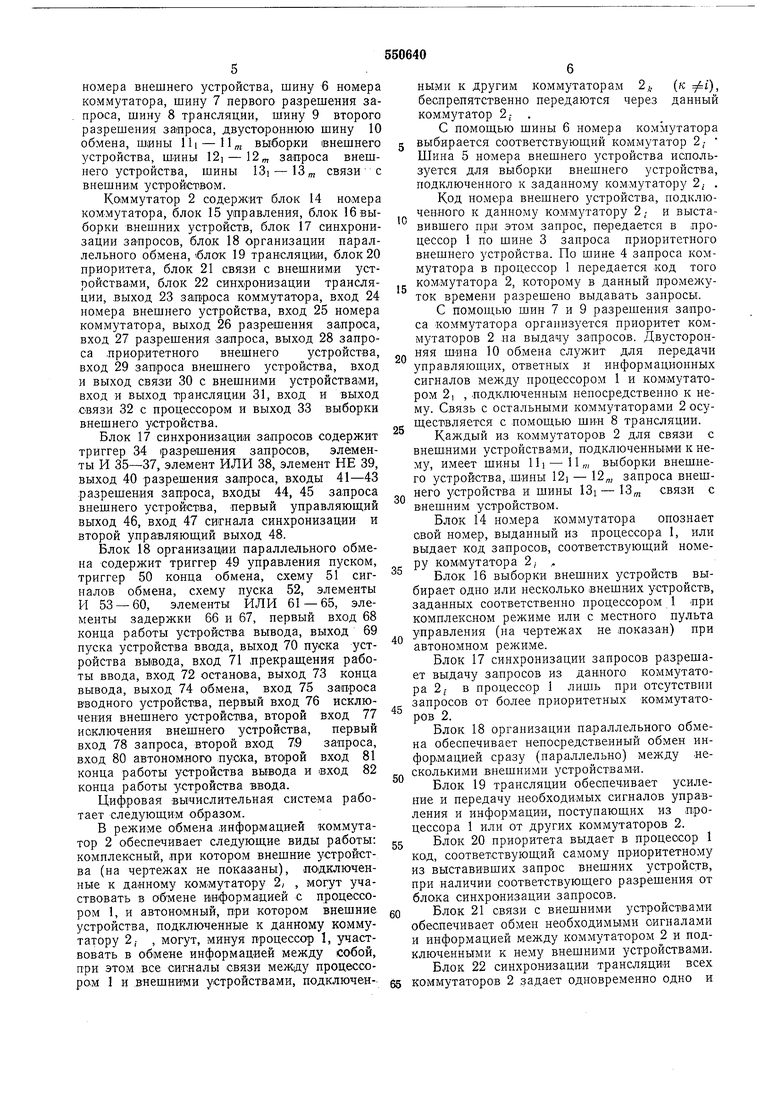

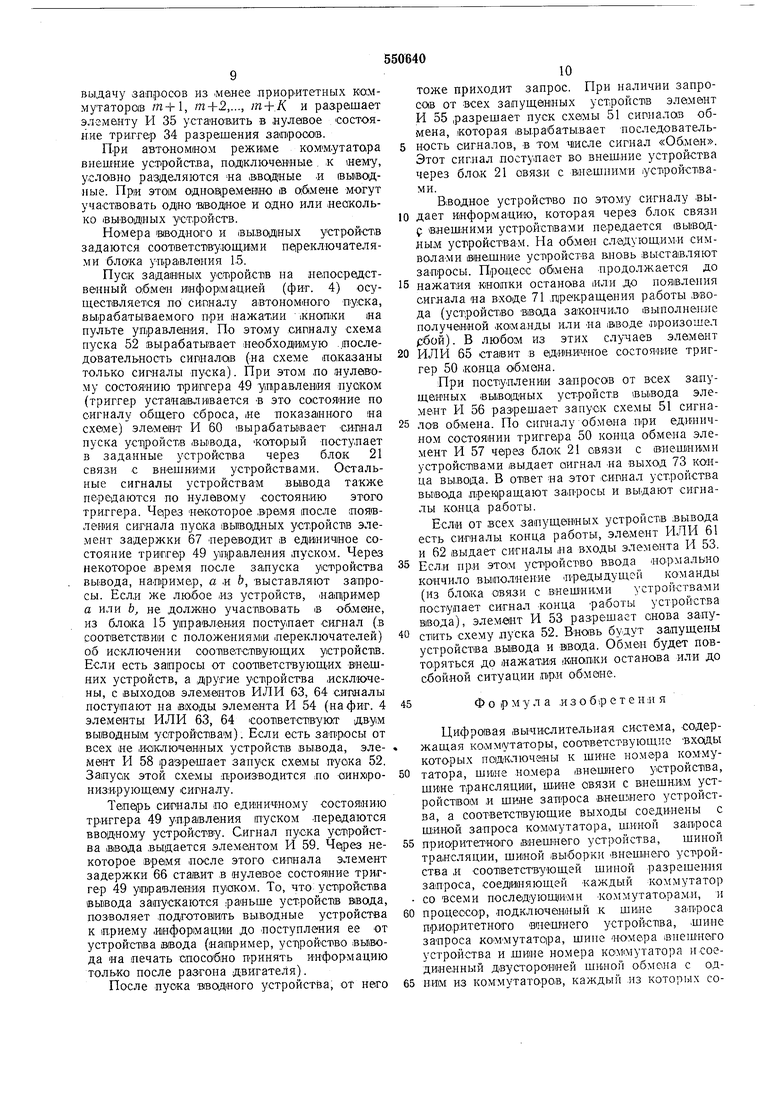

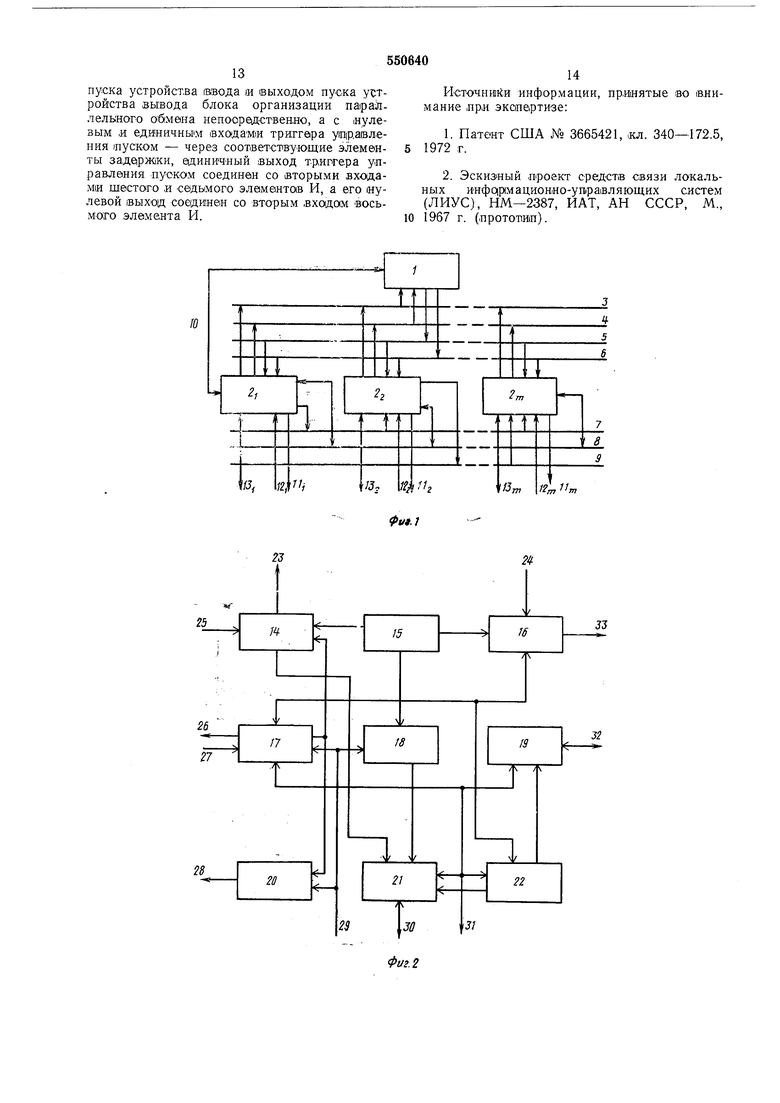

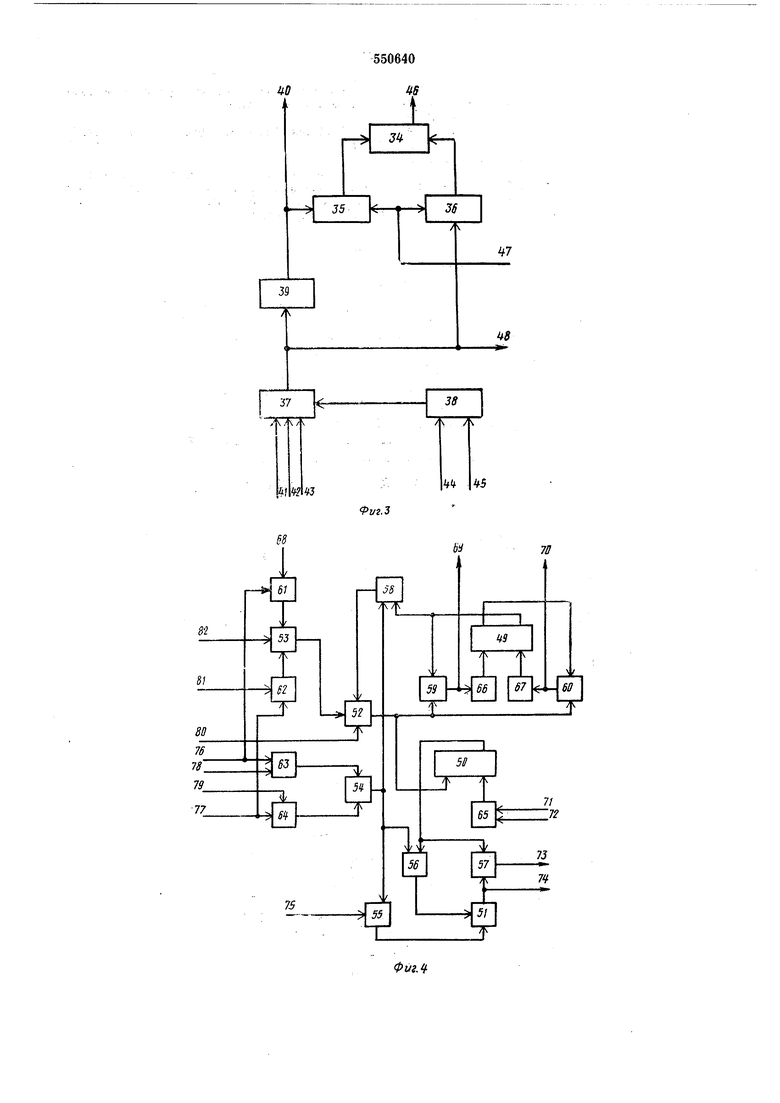

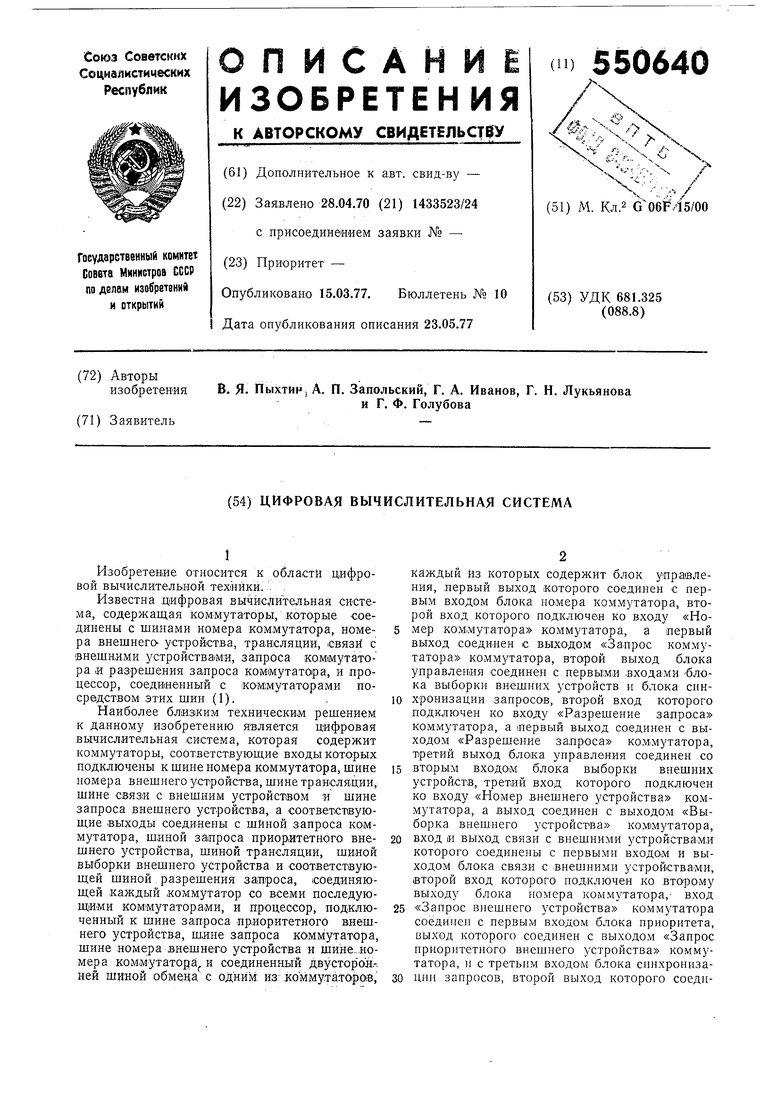

На фиг. 1 показана блок-схема предлагаемой цифровой выч-ислительной системы; на фиг. 2 - блок-схема коммутатора;,на фиг. 3 - блок-схема блока синхронизации запросов;

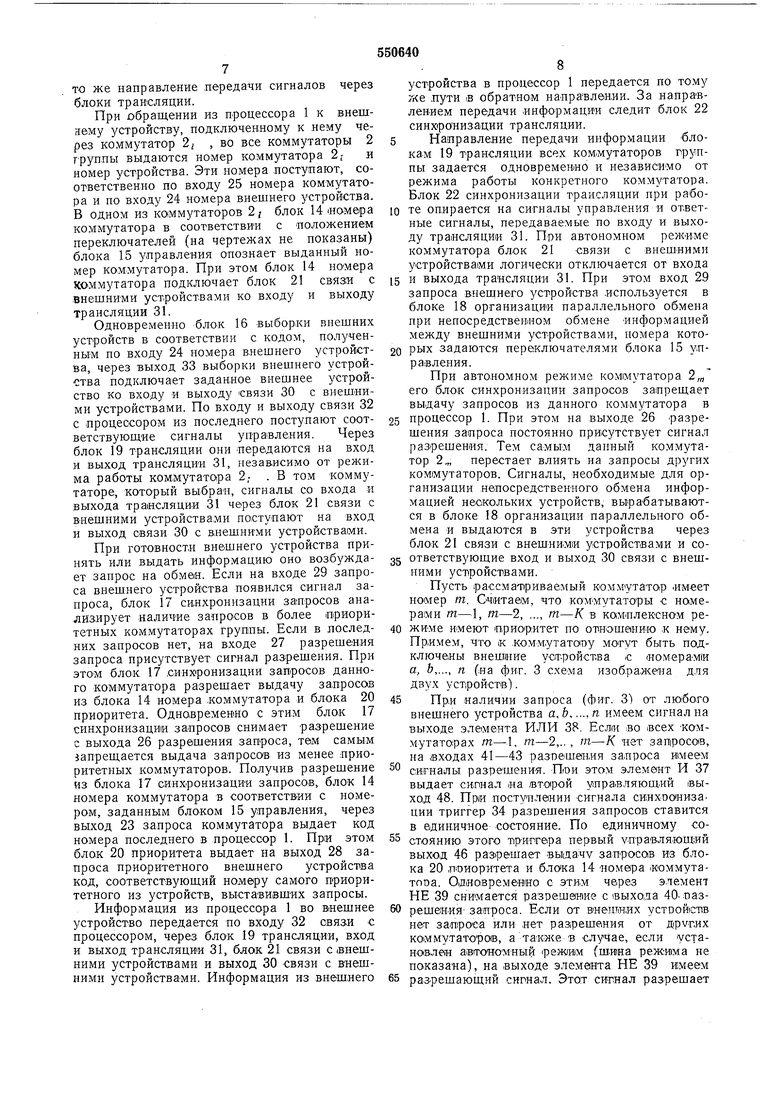

0 на фиг. 4 - блок-схема блока организации параллельного обмена.

Цифровая вьгаислительная система содержат процессор 1, коммутаторы 2i - 2 „, шину 3 запроса приоритетного внешнего устройства, шяну 4 запроса коммутатора, шину 5 номера внешнего устройства, шину 6 номера коммутатора, шину 7 первого разрешения за. проса, шину 8 трансляции, шину 9 второго разрешения запроса, двустороннюю шину 10 обмена, ШИНЫ Hi -11 выборки внешнего устройства, шины 12 - 12 „ запроса внешнего устройства, шины 13 - 13 „ связи с внешним устройств-ом. Коммутатор 2 содержит блок 14 но-мера коммутатора, блок 15 управления, блок 16 выборки внешних устройств, блок 17 синхронизации запросов, блок 18 организации параллельного обмена, блок 19 трансляции, блок 20 приоритета, блок 21 связи с внешними устройствами, блок 22 синхронизации трансляции, .выход 23 запроса коммутатора, вход 24 номера внешнего устройства, вход 25 номера коммутатора, выход 26 разрешения запроса, вход 27 разрешения -запроса, выход 28 запроса приоритетного внешнего устройства, вход 29 запроса внешнего устройства, вход и выход связи 30 с внешними устройствами, вход и выход Т1рансляци,и 31, вход и выход связи 32 с процессором и выход 33 выборки внешнего устройства. Блок 17 синхронизации запросов содержит триггер 34 разрешения запросов, элементы И 35-37, элемент ИЛИ 38, элемент НЕ 39, выход 40 разрешения запроса, входы 41-43 разрешения запроса, входы 44, 45 запроса внешнего устройства, первый управляюш,ий выход 46, вход 47 сигнала синхронизации и второй управляющий выход 48. Блок 18 организации параллельного обмена содержит триггер 49 управления пуском, триггер 50 конца обмена, схему 51 сигналов обмена, схему пуска 52, элементы И 53 - 60, элементы ИЛИ 61 - 65, элементы задержки 66 и 67, первый вход 68 конца работы устройства вывода, выход 69 пуска устройства ввода, выход 70 пуска устройства вывода, вход 71 прекращения работы ввода, вход 72 останова, выход 73 конца вывода, выход 74 обмена, вход 75 запроса вводного устройства, первый вход 76 исключения внешнего устройства, второй вход 77 исключения внешнего устройства, первый вход 78 запроса, второй вход 79 запроса, вход 80 автономного пуска, второй вход 81 конца работы устройства вывода и вход 82 конца работы устройства ввода. Цифровая -вычислительная система работает следующим О:бразом. В режиме обмена информацией коммутатор 2 обеспечивает следующие виды работы: комплексный, при котором внешние устройства (на чертежах не показаны), подключенные к данному коммутатору 2, , могут участвовать в обмене И1нформацией с процессором 1, и автономный, при котором внешние устройства, подключенные к данному коммутатору 2; , могут, минуя процессор 1, участвовать в обмене информацией между собой, при этом все сигналы связи между процессором 1 и .внешними устройствами, подключенными к другим коммутаторам 2. (к i), беспрепятственно передаются через данный ком-мутатор 2,С помощью шины 6 номера коммутатора выбирается соответствующий коммутатор 2,Шина 5 номера внешнего устройства используется для выборки внешнего устройства, подключенного к заданному коммутатору 2,- . Код номера внешнего устройства, подключенного к данному ком-мутатору 2,. и выставившего при этом запрос, передается в процессор 1 по шине 3 запроса приоритетного внешнего устройства. По шине 4 запроса коммутатора в процессор 1 передается код того ком-мутатора 2, которому в данный промежуток времени разрешено выдавать запросы. С помощью шин 7 и 9 разрешения запроса коммутатора организуется приоритет коммутаторов 2 на выдачу запросов. Двусторонняя щина 10 обмена служит для передачи управляющих, ответных и информационных сигналов между процессором 1 н коммутатором 2, , -подключенным непосредственно к нему. Связь с остальными коммутаторами 2 осуществляется с помощью шин 8 трансляции. Каждый из коммутаторов 2 для связи с внешними устройствами, подключенными к нему, имеет шины lli - 11,„ выборки внешнего устройства, шины 12i - 12„, запроса внешнего устройства и шины 13i - 13,„ связи с внешним устройством. Блок 14 номера коммутатора опознает свой номер, выданный из процессора 1, или выдает код запросов, соответствующий номеру коммутатора 2, ,. Блок 16 выбо.рки внешних устройств выбирает одно или несколько внешних устройств, заданных соответственно процессором 1 при комплексном режиме или с местного пульта управления (на чертежах не показан) при автономном режиме. Блок 17 синхронизации запросов разрешает выдачу запросов из данного коммутатора 2,- в процессор 1 лишь при отсутствии запросов от более приоритетных коммутаторов 2. Блок 18 организации параллельного обмена обеспечивает непосредственный обмен информацией сразу (параллельно) между -неколькими .внешними устройствам-и. Блок 19 трансляции обеспечивает усилеие и передачу .необходимых сигналов управения и информации, поступаюших из проессора 1 или от других коммутаторов 2. Блок 20 приоритета выдает в процессор 1 од, соответствующий самому приоритетному з выставивщих запрос внещних устройств, ри наличии соответствующего разрешения от лока синхронизации запросов. Бло.к 21 связи с внешними устройствами беспечивает обмен необходимыми сигналами информацией между коммутатором 2 и подлюченными к нему внешними устройства.ми. Блок 22 синхронизации трансляции всех оммутаторов 2 задает одновременно одно и

то же направление .передачи сигналов через блоки трансляции.

При обращении из процессора 1 к внешнему устройству, подключенному к .нему через коммутатО р 2; , во все коммутаторы 2 Груп.пы выдаются номер коммутатора 2; и номер устройства. Эти номера .поступают, соответственно по входу 25 номера коммутатора и по входу 24 номера внешнего устройства. В одном из коммутаторов 2 блок 14 «омара коммутатора в соответствии с положением переключателей (на чертежах не показаны) блока 15 управления опознает выданный номер коммутатора. При этом блок 14 номера коммутатора подключает блок 21 связи с внешними устройствами ко входу и выходу трансляции 31.

Одновременно блок 16 выборки внешних устройств в соответствии с кодом, полученным по входу 24 номера в.нешнего устройства, через выход 33 выборки внешнего устройства подключает заданное внешнее устройство ко входу и выходу СВЯЗИ 30 с внешними устройствами. По входу и выходу связи 32 с процессором из последнего поступают соответствуюшие сигналы управления. Через блок 19 трансляции они передаются на вход и выход трансляции 31, независимо от режима работы коммутатора 2,- . В том коммутаторе, который выбран, сигналы со входа и выхода траисляци-и 31 через блок 21 связи с внешними устройства.ми поступают на вход и выход связи 30 с внешними устройствами.

При готовности внешнего устройства принять или выдать информацию оно возбуждает запрос на обме1Н. Если на входе 29 за.проса внешнего устройства появился сигнал занроса, блок 17 синхронизации запросов аналиаирует наличие запросов в более приоритетных коммутаторах групяы. Если в последних запросов нет, на входе 27 разрешения запроса присутствует сигнал разрешения. При это-м блок 17 синхронизации запросов данного коммутатора разрешает выдачу запросов из блока 14 номера .коммутатора и блока 20 приоритета. Одно-времевно с эти.м бло.к 17 синхронизации запросов снимает разрешение с выхода 26 разрешения запроса, тем самым запрешается выдача запросов из менее .приоритетных коммутаторов. Получив разрешение из блока 17 синхронизации запросов, блок 14 номера коммутатора в соответствии с номером, заданным блоком 15 управления, через выход 23 запроса коммутатора выдает код номера последнего в процессор 1. При этом бло.к 20 приоритета выдает на выход 28 запроса приоритетного внешнего устройства код, соответствующий номеру самого приоритетного из устройств, выставивших запросы.

Информация из процессора 1 во внешнее устройство передается но входу 32 связи с процессором, через блок 19 трансляции, вход и выход трансляции 31, блок 21 связи с внешними устройствами и выход 30 связи с внешними устройствами. Информация из внеш.него

устройства в процессор 1 передается по тому же .пути iB обратном направлении. За направлением передачи информации следит блок 22 синхронизации трансляции.

5 Направление передачи информации -блока.м 19 трансляции всех коммутаторов группы задается одновременно и независимо от режима работы конкретного коммутатора. Блок 22 синхронизации трансляции при работе опирается на сигналы управле.ния и ответные сигналы, передаваемые по входу и выходу трансляции 31. При автономном режиме коммутатора блок 21 связи с внешними устройствами логически отключается от входа

15 и выхода трансляции 31. При этом вход 29 запроса в.нешнего устройства .используется в блоке 18 организации параллельного обмена при непосредственном обмене информацией между внешними устройствами, номера которых задаются переключателями блока 15 управления.

При авто.номном режиме коммутатора 2,„ его блок синхронизации запросо.в запрешает выдачу запросов из данного коммутатора в

5 процессор 1. При этом на выходе 26 разрешения запроса постоянно присутствует сигнал разрешения. Тем самым данный коммутатор 2 перестает влиять на запросы других коммутаторов. Сигналы, необходимые для организации .непосредственного обмена информацией нескольких устройств, вырабатываются в блоке 18 орга.низации параллельного обмена и выдаются в эти устройства через блок 21 связи с внешними устройствами и соответствующие вход и выход 30 связи с внешними устройствами.

Пусть рассматриваемый коммутатор имеет номер т. Считаем, что коммутаторы с номерами т-1, т-2, ..., т-К в комплексном режиме имеют приоритет по отношению .к нему. Примем, что iK .коммутатору могут быть подключены внешние устройства с иомерами а, Ь,..., п (на фиг. 3 схема изоб.ражена для двух устройств).

При наличии запроса (фиг. 3) от любо.го внешнего устройства а,Ь....,п имеем сигнал на выхо.де элемента ИЛИ 38. Если во всех -коммутаторах т-1, m-2,.. , m-К нет aanipocoiB, на входах 41-43 разрешения залроса вмеем сигналы разрешения. Пои этом элемент И 37 выдает сигнал «а второй у1Пра.в.ляюШИЙ выход 48. При .поступлении сигнала синхронизапии триггер 34 разрешения запросов ставится в единичное состояние. По единичному состоянию этого Т1рилгера первый управляющий ВЫХО.Д 46 разрешает выдачу запросов и-з блока 20 ЛРиоритета и блака 14 номера «оммутатора. Одновременно с этим через элемент НЕ 39 снимается разрешэние с выхода 40. ваз0 решения- запроса. Если от внешних устройст1в нет запроса или .нет раз1решения от других коммутаторов, а также в случае, если установьлен автономный реж/вм (ш.и1на режима не показана), на выходе элемента НЕ 39 кмеем разрешаюший сигнал. Этот сигнал разрешает

выдачу запросов из менее приоритетных коммутаторов т+, т+2,..., т + К и разрешает эл-гменту И 35 установить в нулевое состояние триггер 34 разрешения заирОСов.

При автономном режиме коммутатора внешние устройства, но1дклк ченяые , к «ему, условно разделяются -на вводные .и выводные. При STOiM о,днов(ременно в обмене могут участвовать одно вводное и одно или неаколько ВЫВОД1НЫХ устройств.

Номера ВВОДНОГО и 1вы.во1дных устройств задаются соот1ветст(ву.юш,.ими п.е)реключателями блока управления 15.

Пуск заданных усТ(рой.ст1В на непосредственный обмен информацией (фиг. 4) осуш,ест(вляется по скпналу автономного пуска, вырабатываемого при нажатии жнапки на нульте управлевия. По этому сигналу схема пуска 52 вырабатывает необходимую .последовательность сипналов (на схеме показаны только сигналы пуска). При этом по иулевому состоянию триггера 49 уцравления пуском (триггер устана1вли1вается -в это со1стояние по сигналу 0)бщего сброса, не показанного на схеме) элемент И 60 вырабатывает сигнал пуска уст|ройст/в .вьшода, который поступает в заданные устройства через блок 21 связи с внешними устройствами. Остальные сигналы устройствам вывода также передаются по нулевому состоянию этого триггера. некоторое .время после иоявлешия сигнала пуска 1ВЫ1вО|Дных уст;ройст1В элемент задержки 67 .переводит IB единич1ное состояние триггер 49 урралления луском. Через некоторое время пОСле запуска устройства вывода, например, а и Ь, выставляют затаросы. Если же любое из устройств, нащример а пли bj не должно участ1вовать в обмене, из блока 15 управления поступает сигнал (в соответствии с положениями переключателей) об исключении соот|ве;тст1вующих устройств. Если есть запросы от соответствующих внешних устройств, а другие устройства искл-ючены, с выходов элементов ИЛИ 63, 64 сипналы поступают на вкоды элемента И 54 (на фиг. 4 элементы ИЛИ 63, 64 соответствуют двум выводным устройствам). Если есть запросы от всех не исключенных устройств вывода, элемент И 58 разрешает запуск схемы пуока 52. Запуск этой схемы производится по -onHXipoнизирующему сигналу.

Teneipb сигналы по еди1нично,му состоянию триггера 49 управления пуском передаются вводному устройству. Сигнал пуска устройства ввода выдается элементом И 59. некоторое время после этого сипнала элемент задержки 66 ставит в нулевое состояние триггер 49 уоравления пуском. То, что- уст1рой|ства вывода запускаются раньше устройств ввода, позволяет подготовить выводные устройства к приему информации до поступления ее от устройства 1ввода (например, уст1ройство вывода на печать способно принять информацию только после разгона двигателя).

После пуока вводного устройства, от него

тоже приходит запрос. При наличии запросов от всех запущенных устройств элемент И 55 разрешает пуск схемы 51 сипналав обмена, .которая (Вырабатывает последовательность сигналов, в том Ч1исле сигнал «Обмен. Этот сигнал поступает во внешние устройства через блок 21 связи с внешними устройствами.

Вводное устройство по этому сигналу выдает информацию, которая через блок связи f внешними устройствами передается выводным устройствам. Па обмен следующими символами внешние уст1ройства вновь выставляют запросы. Процесс обмена продолжается до

5 нажатия кнопки останова или до появления сигнала на входе 71 лрекращения работы ,ввода (устройство ввода закончило выполнение полученной команды или на 1В|Воде произошел рбой). В любом из этих случаев элемент

0 ИЛИ 65 ставит в единичное состояние триггер 50 конца обмена.

При поступлении запросов от всех запущенных выво1Д«ых устройств вывода элемент И 56 разрешает запуск схемы 51 сигналов обмена. По сипналу обмена при едшшчном состоянии триггера 50 конца обмена элемент И 57 через блок 21 связи с (внешними устройствами ;выдает сигнал на выход 73 конца вывода. В ответ на этот сигнал устройства вывода прек|рашают запросы и выдают сигналы конца работы.

Если от всех запущенных устройств вывода есть сигналы конца работы, элемент ИЛИ 61 и 62 выдает сигналы па входы элемента И 53. 5 Если при этом устройство ввода нормально кончило выполнение предыдущей команды (из блока овязи с внешними устройствами поступает сигнал конца работы устройства ввода), элемент И 53 разрешает снова запустить схему пуСка 52. Вновь будут запушены устройства вывода и ввода. Обмен будет повторяться до нажатия К|Нопки останова или до сбойной ситуации при обме1не.

Формула изобретен ;и я

45

Цифровая вычислительная система, содержащая коммутаторы, соответствующле входы

кото-рых подключены к шине номера коммутатора, ши)не номера внешнего устройства, шине трансляции, шине связи с внешним устройством и шине запроса внешнего устройства, а соответствующие выходы соединены с шиной запроса коммутатора, шиной запроса

55 приоритетного внешнего устройства, шиной трансляции, шииой выборки внешнего устройства и соответствующей шиной разрешения запроса, соед|И1Няющей -каждый коммутатор со всеми последующими -коммутаторами, и

60 процессор, подключенный к шипе заПроса приоритетного виешнего устройства, .шине запроса ко-ммутатсра, шипе номера внешнего устройства и щине номера коммутатора и соединенный двусторонней шиной обмоиа с од65 Н-И1М из коммутаторов, каждый из которых со11

держит блок управления, первый выход которого соединен с первым входом блока номера ком1мутатора, .второй вхад кото|рого под слючен ко в-ходу «Номе|р ком мутатора коммутатора, а первый выход соединен с выходом «Запрос коммутатора «ом1мутатора, второй выход блока упра/вления соединен с первыми входами блока выборки внешних устройств и блока сиихроннвадии заиросов, второй вход которого подключен ко входу «Разрешение запроса коммутатора, а .первый выход со едииен с выходом «Разрешение запроса коммутатора, третий выход блока уира,вления соединен со втарЫ1М входом блока выборжи внешних устройств, третий вход KOTQporo подключен ко входу «Номер внешнего устройства коммутатора, а выход соединйн с выходом «Вы1бор ка внешнего уст1ройст1ва коммутатора, вход и выход связи с .В1неш1Н,И1М)И устройствами которого соединены с первыми входом и выходом блока связи с внешними устройствами, второй вход которого .подключен ко второму выходу блока номера коммутатора, вход «Запрос внешнего успройства коммутатора соединен с первы м входом блока приоритета, выход которого соединен с выходом «Запрос приоритетного внешнего устройства коммутатора, и с третьим входом бло1ка синхронизации запросов, второй выход которого соединен со вторым входом блока приоритета и с третьим входом блока номера коммутатора, о т л и ч а ю ш; а я с я тем, что, с цельк) расширения фуекциональных возможностей, в ней каждый коммутатор содержит блок трансляции, блок синхронизации -лрансляц ии л блок организации параллельного обмена, соответствуюшие входы которого подключены ко второму выходу блока управления, входу «Запрос внешнего уст1ройст1ва коммутатора и второму выходу блока связи с внешними устройствами, чет1вертый вход которого лод ключен к первому выходу блока синхронизации трансляции, второй выход которого соединен со входом блока трансляции, а первый вход подключен ко второму выходу блока управления, вход и выход «Трансляция коммутатора сое/динены с соответствующими входом и выходом блока свя1зи с внешними устройствами, блока синхронизации трансляции, блока синхронизации запросов и блока трансляции, соответспвуюШИе вход и выход которого подключены ко входу и выходу «Обмен коммутатора.

2. Система по н. 1, от лич а юш,а яс я тем, что блок си1нхронизации запросов содержит элементы И, ИЛИ, НЕ и триггер разрешения запросов, выход которого сое|динен с первым управляющим выходом блока свнхроннзацаи запросов, входы разрешения за- проса которого соеди1нены с 1соответст1вуюшими входами первого элемента И, соответствуюший вход которого через элемент ИЛИ подключен ко входам запроса внешнего устройства блока синхронизации запросов, а выход соединен со входом элемента НЕ, первым

12

входом второго элемента И и вторым управляющим выходом блока синхронизации запросов, выход элемента НЕ соединен с первым входом, третьего элемента И и выхоб дом раарешвЕия запроса блока .аиих,ранизации запросов, вход 1СИ:пнала оинх)ронизации которого соедин-ен со вторыми входами второго и третьего элементов И, выходы которых соединены с соответствующими входами триггера 10 разрешения запросов.

3. Система по п. 1, о т л ич а ю щ а я с я тем, что блок организации параллельного обмена содержит элементы И и ИЛИ, элементы задержки, схему пуска, триггер конца обмена, 15 триггар управления пуском и схему сигналов обмена, выход, которой 1соеди«е1н с выходом обмена блока орга1Н.иза1ЦИ1и параллелыного обмена, первый вход конца работы устройства вывода которого через первый элемент ИЛИ,

0 подключ.енный вторым .входом к первому входу исключения внешнего устройства блока организации параллельного обмена, соединен с первым входом первого элемента И, подключенным вторым входом ко входу «Конец

5 работы устройст1ва влвода блока организаци1И параллельного обмана, второй вход конца работы устройства вывода которого через второй элемент ИЛИ, подключенный вторым входом «о второму входу исключения внешнего устройства блока организации параллельного обмена, соединен с третьим входом первого элемента И, выхо/д которого соединен с первым входом схемы пуока. второй вход которой подключен ко входу автономного пуска

5 блока организации параллельного обмена, первый и второй входы исключения внешнего устройства которого через третий и, соот ветственно, четвертый элементы ИЛИ, подключенные вто)рыми входами к первому и, ооот0 ветственно, второму вкодам запроса блока организации па|раллель(ного обмена, соединены с первым и вторым (входами второго элемента И, входы останова ,и прекращения работы ввода блока организации параллельного об5 мена через пятый элемент ИЛИ соединены с

единичным входом триггера «оица обмена,

нулевой вход которого подключен к выходу

. схемы пуска, а выхо.д соединен с .пе рвьими

входами третьего и четвертого элементов И,

0 выход послед него из которых соединен с neipBbLM входом схемы сигналов обмена, второй вход которой подключен к выходу пятого элемента И, а выход соединен со вторым входом третьего элемента И, выход которого соединен с выходом конца вывода блока организации параллельного обмена, вход запроса ВВО.ДНОГО устройства которого соединен с первым входом пятого элемента И, выход BTOipoго элемента И соединен со вторыми входами

o четвертого и пятого элементов И и пе1рвым входом шестого элемента И, выход которого сое динен с третьим входом схемы пуска, выход которой соединен с первыми входами седьмого и восьмого элементов И, выходы которых соединены, соответственно, с выходом пуска устройства (ввода м выходом пуска устройства вывода блока организации naipaiiлелвного обмена непооредственно, а с «улезым ,и единичным 1Вхо1даМ1И триггера урр.авления inyCKOM - через соотеетству-ющие элементы заде|рЖ|Ки, единиЧНый выход триггера управления пуском соединен со вторыми входами шестого и седьмого элементов И, а его нулевой выход соедннен со вторым входом восьмого элемента И. 5 10 Источники информации, пранятые во внимание ,пр,и экспертизе: 1.Патент США № 3665421, ,кл. 340-172.5, 1972 г. 2.Эскизный ироект средств связи локальных ИНфО(р1мациоН|НО-уп1равляк щих систем (ЛИУС), НМ-2387, ИАТ, АН СССР, М., 1967 г. (прототип).

да

0, /2, 7/f/J.

J

Фи. /

р«

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения модулей процессора | 1982 |

|

SU1056176A2 |

| Устройство для сопряжения | 1978 |

|

SU813401A2 |

| Устройство для обмена данными | 1974 |

|

SU506847A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1987 |

|

SU1432580A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Устройство для сопряжения | 1978 |

|

SU809139A2 |

| Устройство для связи процессоров | 1986 |

|

SU1481785A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1982 |

|

SU1269142A1 |

| Многоканальное устройство для сопряжения модулей процессора | 1980 |

|

SU898412A1 |

Авторы

Даты

1977-03-15—Публикация

1970-04-28—Подача