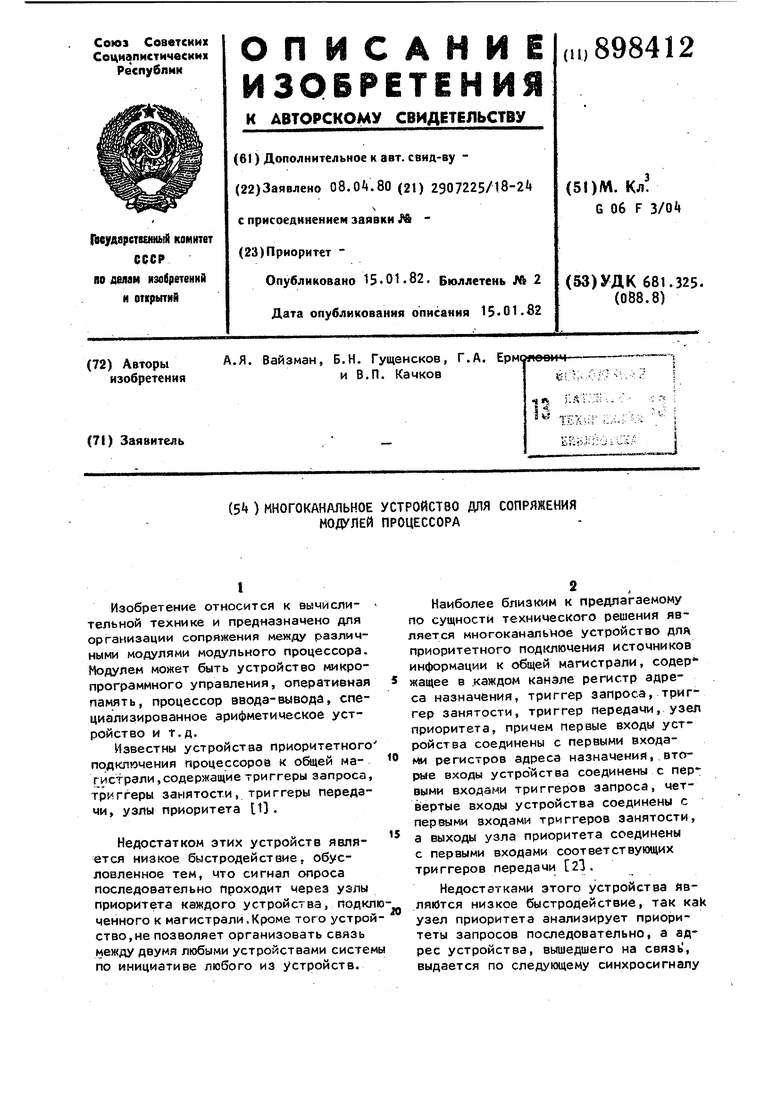

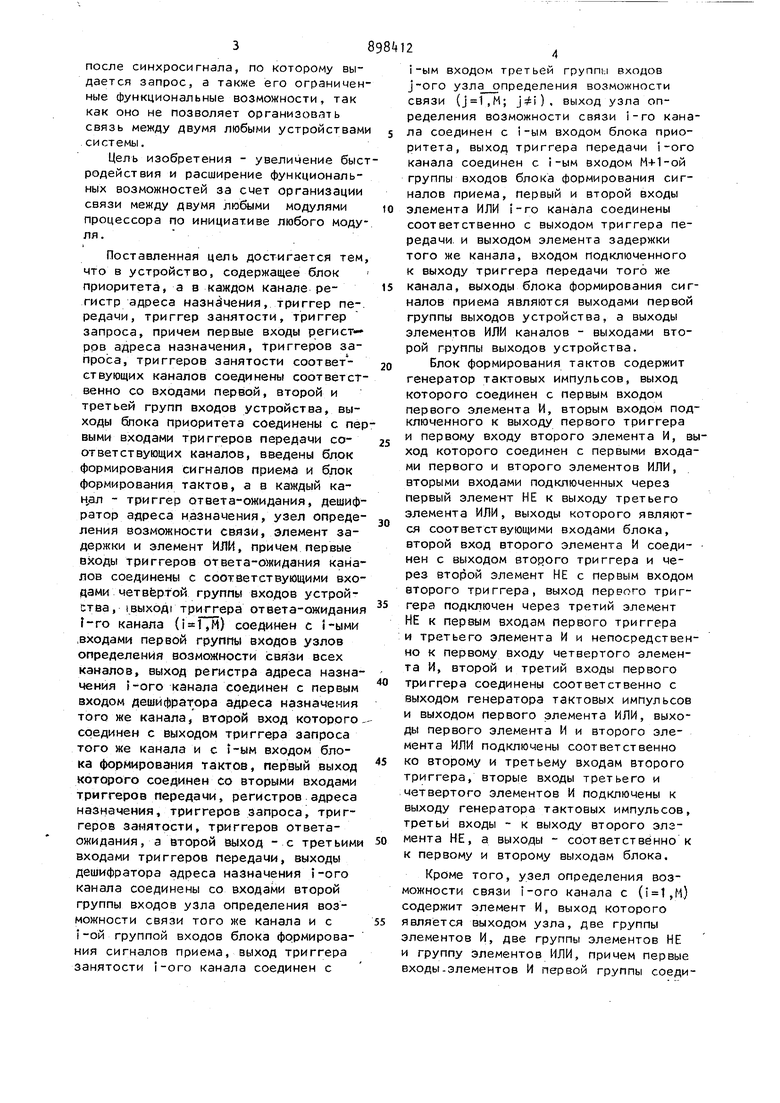

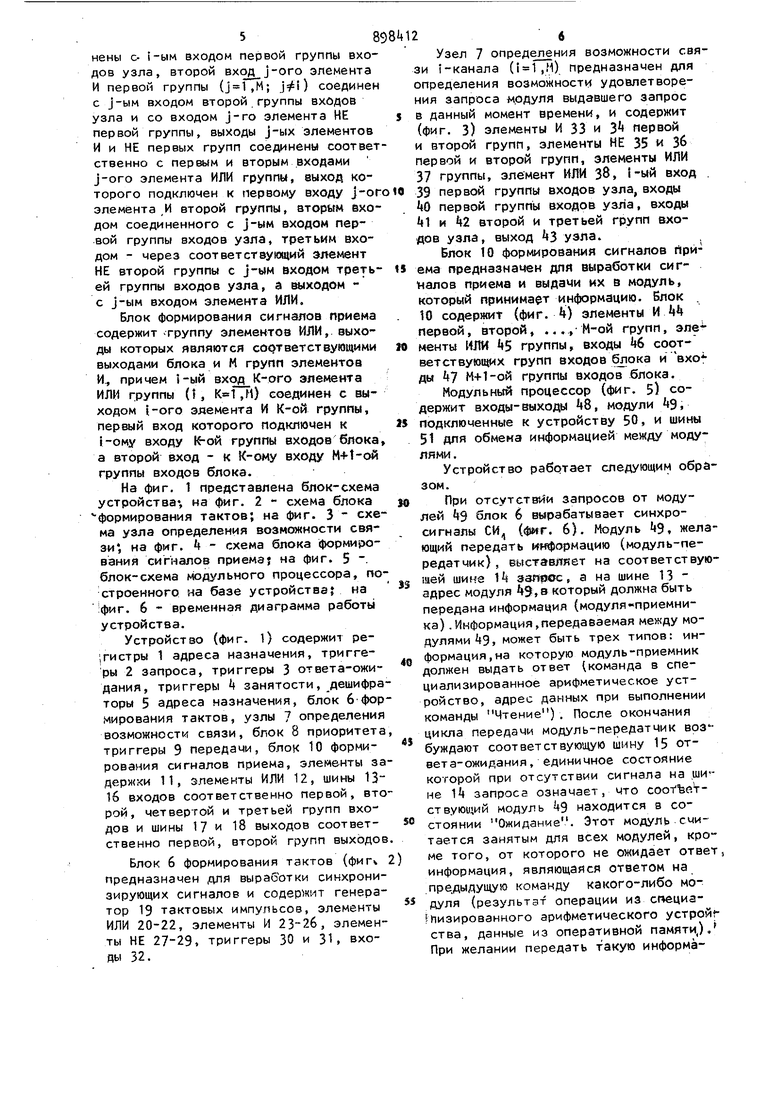

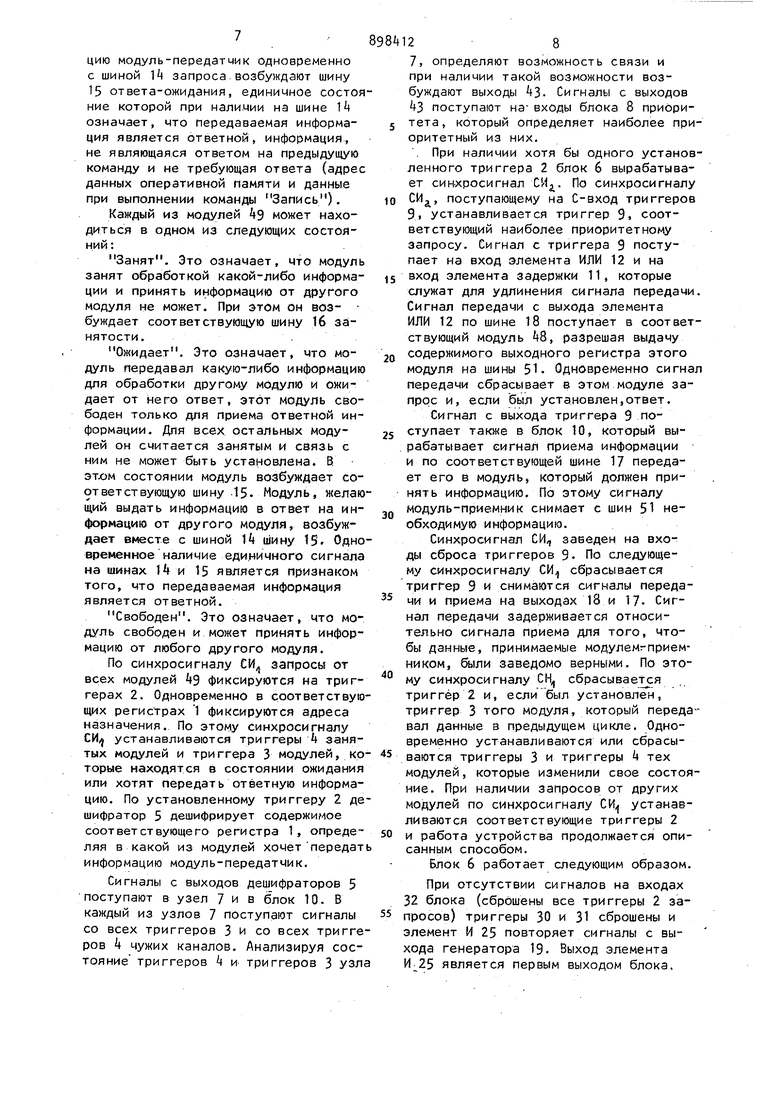

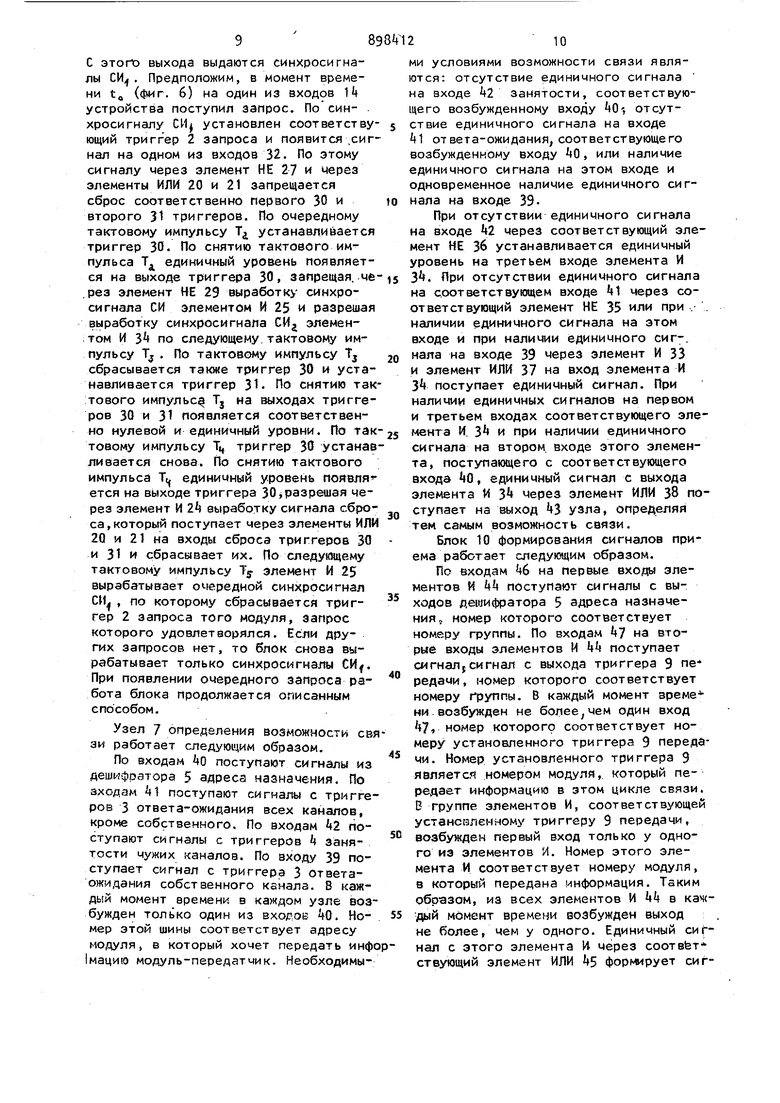

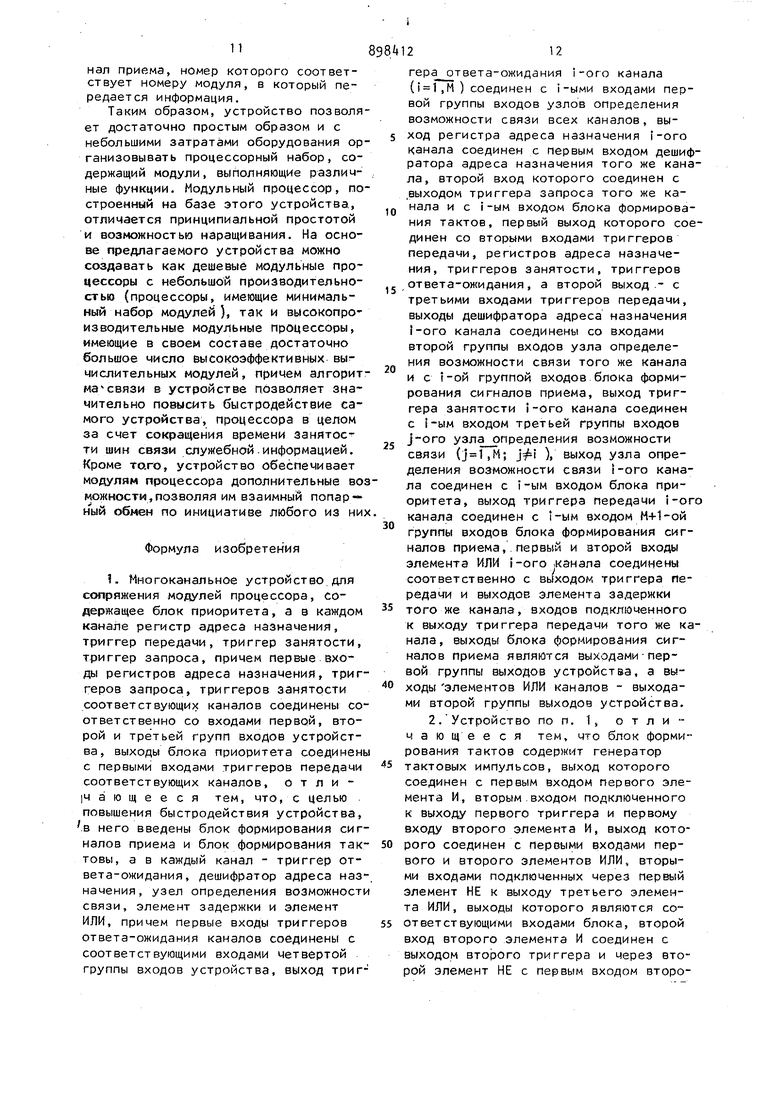

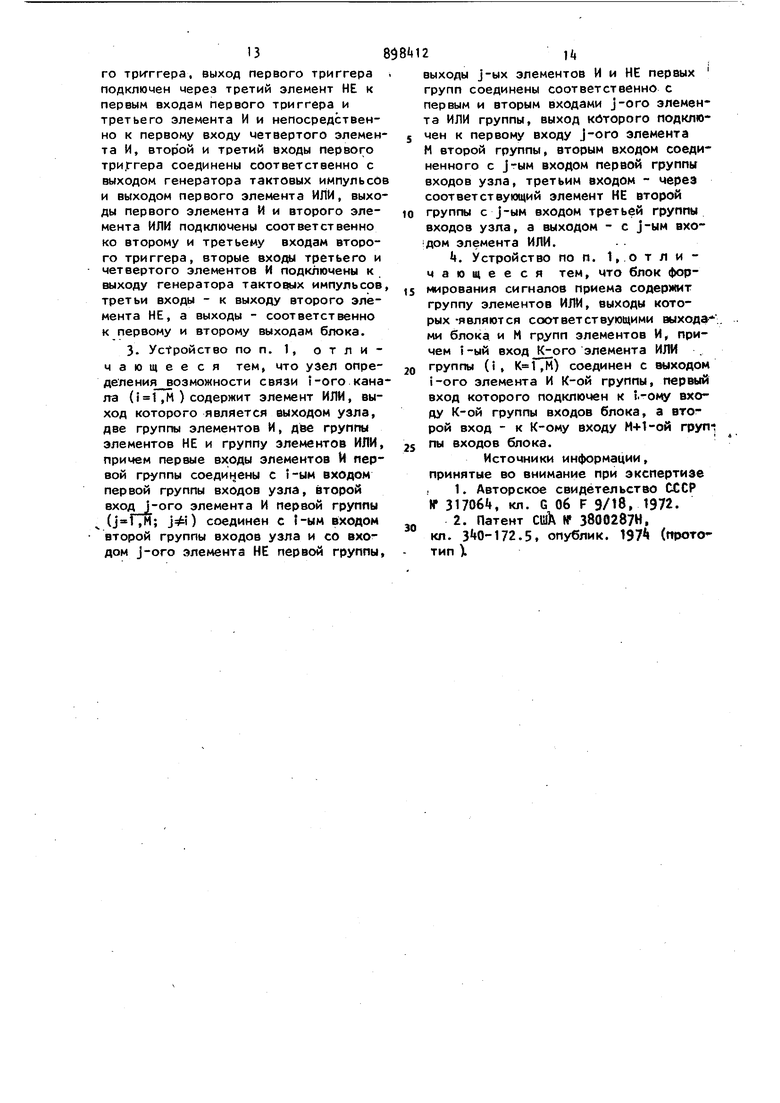

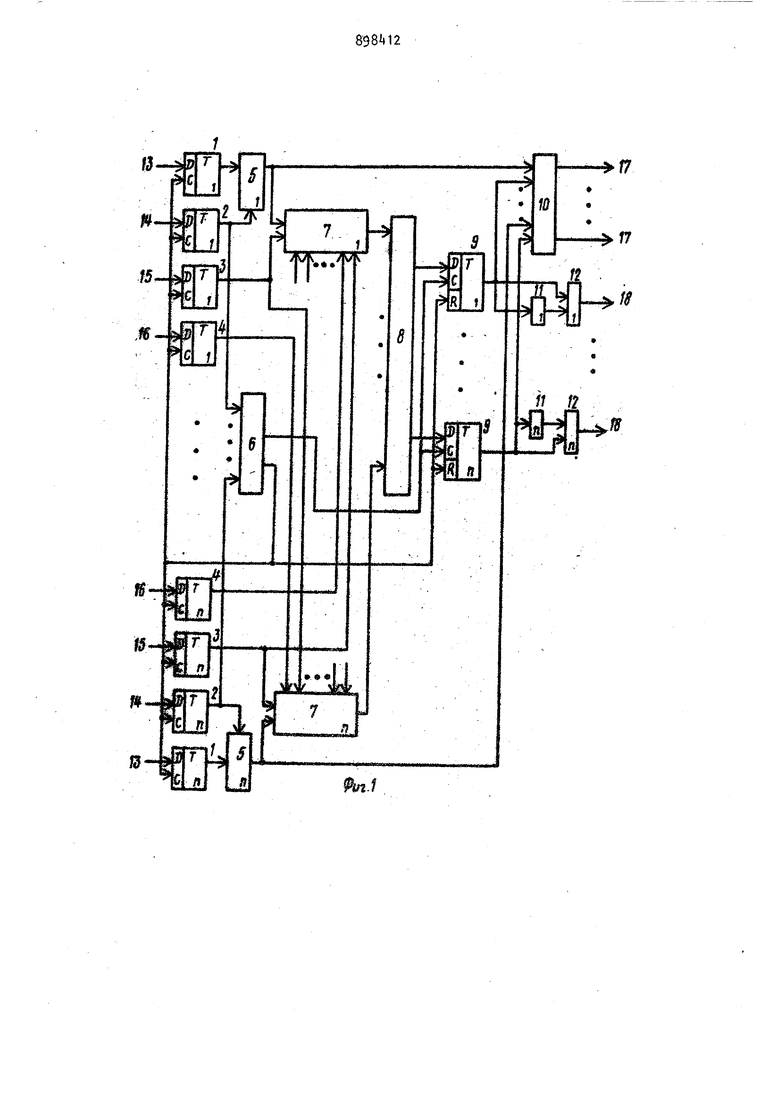

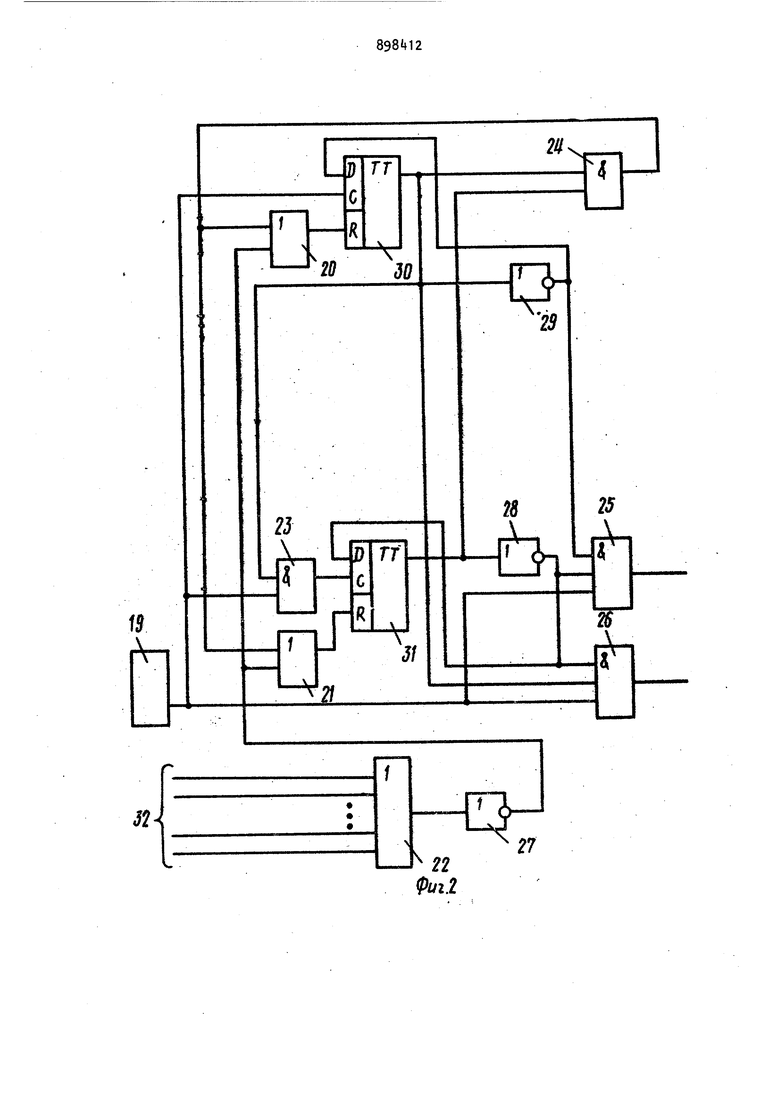

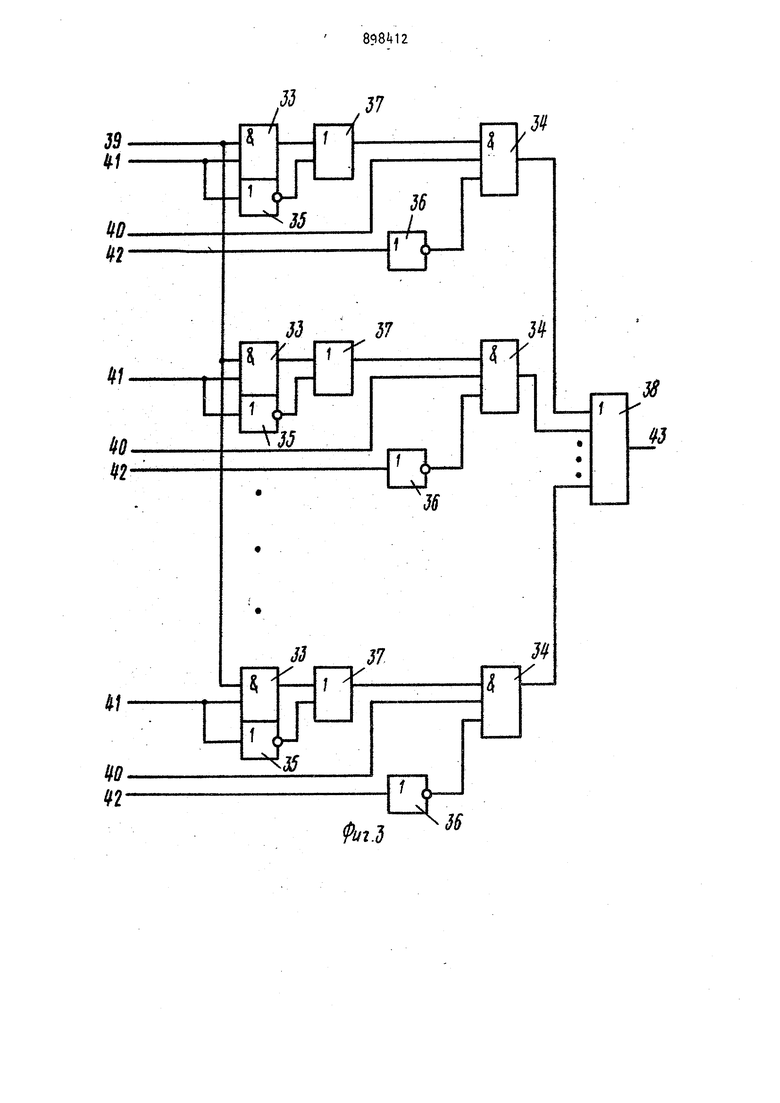

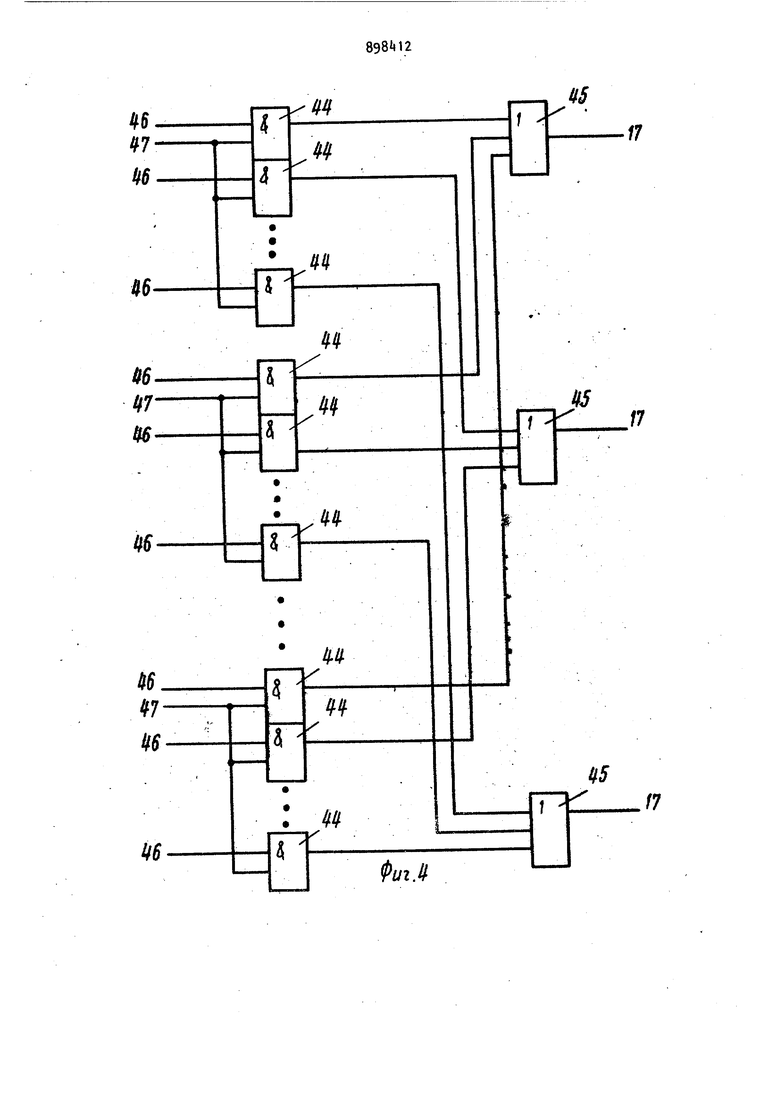

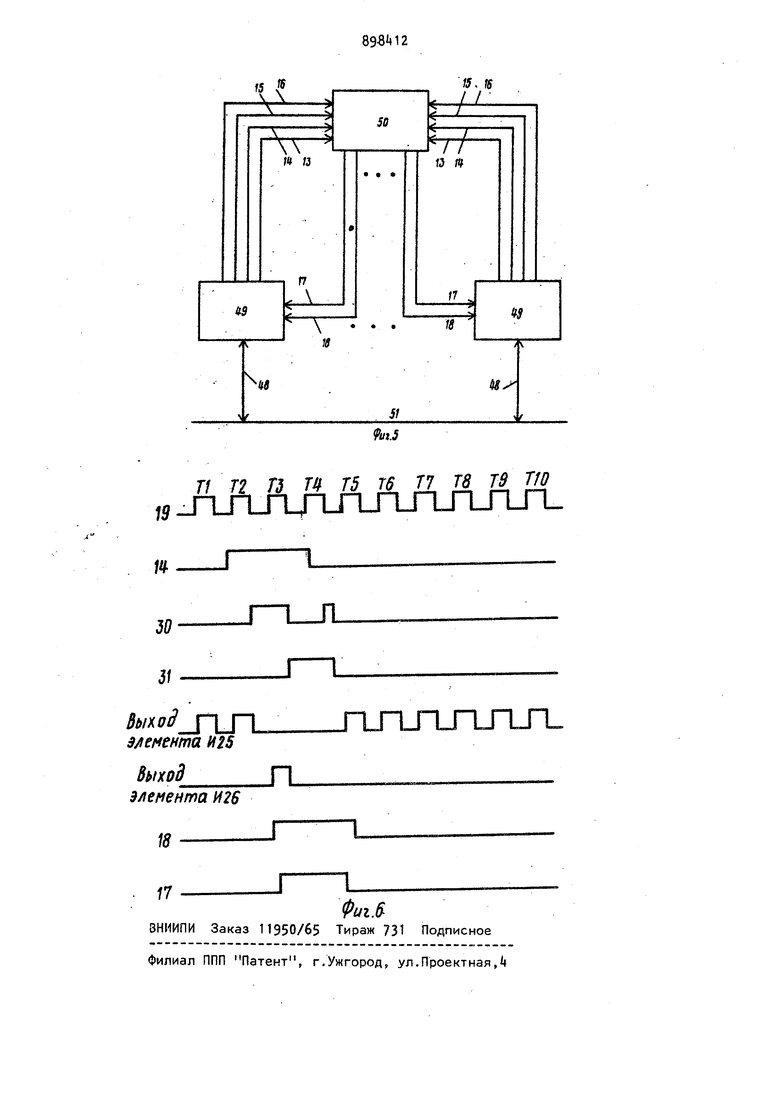

Изобретение относится к вычислительной технике и предназначено для организации сопряжения между различными модулями модульного процессора. Модулем может быть устройство микропрограммного управления, оперативная память, процессор ввода-вывода, специализированное арифметическое устройство и г.д. Известны устройства приоритетного подключения процессоров к общей магистрали, содержащие триггеры запроса, триггеры занятости, триггеры передачи, узлы приоритета 11. Недостатком этих устройств является низкое быстродействие, обусловленное тем, что сигнал опроса последовательно проходит через узлы приоритета каждого устройства, подкл ченного к магистрали.Кроме того устрой ство, не позволяет организовать связь между двумя любыми устройствами систем по инициативе любого из устройств. Наиболее близким к предлагаемому по сущности технического решения является многоканальное устройство для приоритетного подключения источников информации к общей магистрали, содер жащее в .каждом канале регистр адреса назначения, триггер запроса, триггер занятости, триггер передачи, узел приоритета, причем первые входы устройства соединены с первыми входами регистров адреса назначения, вторые входы устройства соединены с пер выми входами триггеров запроса, четвертые входы устройства соединены с первыми входами триггеров занятости, а выходы узла приоритета соединены с первыми входами соответствующих триггеров передачи 23. Недостатками этого устройства являйтся низкое быстродействие, так каК узел приоритета анализирует приоритеты запросов последовательно, а адрес устройства, вышедшего на свя31, выдается по следующему синхросигналу после синхросигнала, по которому выдается запрос, а также его ограничен ные функциональные возможности, так как оно не позволяет организовать связь между двумя любыми устройствам системы. Цель изобретения - увеличение быс родействия и расширение функциональных возможностей за счет организации связи между двумя любыми модулями процессора по инициативе любого моду ля. Поставленная цель достигается тем что в устройство, содержащее блок приоритета, а в каждом канале регистр адреса назн51чения, триггер передачи, триггер занятости, триггер запроса, причем первые входы регист- ррв адреса назначения, триггеров з апроса, триггеров занятости соответствующих каналов соединены соответст венно со входами первой, второй и третьей групп входов устройства, выходы блока приоритета соединены с пе выми входами триггеров передачи соответствующих каналов, введены блок формирования сигналов приема и блок формирования тактов, а в каждый каНал - триггер ответа-ожидания, дешиф ратор адреса назначения, узел опреде ления возможности свйзи, элемент задержки и элемент ИЛИ, причем первые входы Триггеров ответа-ожидания кана лов соединены с соответствующими вхо дами четвёртой группы входов устройства, I выход (триггера ответа-ожидани F-ro канала (,M) соединен с i-ыми .входами первой группы входов узлов определения возможности связи всех каналов, выход регистра адреса назначения i-oro канала соединен с первым входом дешифратора адреса назначения того же канала, второй вход которого соединен с выходом триггера запроса того же канала и с i-ым входом блока формирования тактов, первый выход которого соединен со вторыми входами триггеров передачи, регистров адреса назначения, триггеров запроса, триггеров занятости, триггеров ответаожидания , а второй выход - с третьими входами триггеров передачи, выходы дешифратора адреса назначения 1-ого канала соединены со входами второй группы входов узла определения возможности связи того же канала и с i-ой группой входов блока формирования сигналов приема, выход триггера занятости i-oro канала соединен с i-ым входом третьей группы входов j-oro узла определения возможности связи (,M; ), выход узла определения возможности связи i-ro канала соединен с i-ым входом блока приоритета, выход триггера передами 1-ого канала соединен с i-ым входом М4-1-ой группы входов блока формирования сигналов приема, первый и второй входы элемента ИЛИ i-ro канала соединены соответственно с выходом триггера передачи, и выходом элемента задержки того же канала, входом подключенного к выходу триггера передачи того же канала, выходы блока формирования сигналов приема являются выходами первой группы выходов устройства, а выходы элементов ИЛИ каналов - выходами второй группы выходов устройства. Блок формирования тактов содержит генератор тактовых импульсов, выход которого соединен с первым входом первого элемента И, вторым входом подключенного к выходу первого триггера и первому входу второго элемента И, выход которого соединен с первыми входами первого и второго элементов ИЛИ, вторыми входами подключенных через первый элемент НЕ к выходу третьего элемента ИЛИ, выходы которого являются соответствующими входами блока, второй вход второго элемента И соединен с выходом второго триггера и через второй элемент НЕ с первым входом второго триггера, выход первого триггера подключен через третий элемент НЕ к первым входам первого триггера и третьего элемента И и непосредственно к первому входу четвертого элемента И, второй и третий входы первого триггера соединены соответственно с выходом генератора тактовых импульсов и выходом первого элемента ИЛИ, выходы первого элемента И и второго элемента ИЛИ подключены соответственно ко второму и третьему входам второго триггера, вторые входы третьего и четвертого элементов И подключены к выходу генератора тактовых импульсов, третьи входы - к выходу второго элэмента НЕ, а выходы - соответственно к к первому и второму выходам блока. Кроме того, узел определения возможности связи |-ого канала с (,М) содержит элемент И, выход которого является выходом узла, две группы элементов И, две группы элементов НЕ и группу Элементов ИЛИ, причем первые входы-элементов И первой группы соеди589нены с- i-ым входом первой группы входов узла, второй элемента И первой группы ,M; ) соединен с j-ым входом второй.группы входов узла и со входом j-ro элемента НЕ первой группы, выходы j-ых элементов И и НЕ первых групп соединены соответственно с первым и вторым входами j-oro элемента ИЛИ группы, выход которого подключен к первому входу j-oro элемента ,И второй группы, вторым бходом соединенного с j-ым входом первой группы входов узла, третьим входом - через соответствующий элемент НЕ второй группы с j-ым входом третьеи группы входов узла, а выходом с J-UM входом элемента ИЛИ. Блок формирования сигналов приема содержит группу элементов ИЛИ, выходы которых являются соответствующими выходами блока и М групп элементов И причем 5-ый вход К-ого элемента ИЛИ группы ({, ,Н) соединен с выходом {-ого элемента И К-ой группы, первый вход которого подключен к г-ому входу (еой группы входов блока а второй вход - к К-ому входу M-ft-ой группы входов блока. На фиг. 1 представлена блок-схема устройства-, на фиг. 2 - схема блока формирования тактов; на фиг. 3 схе ма узла определения возможности связи, на фиг. - схема блока формирования сигналов приема на фиг. 5 . блок-схема модульного процессора, по строенного на базе устройства на ;фиг. 6 - временная диаграмма работы устройства. Устройство (фиг. } содержит ре;гистры 1 адреса назначения, триггеры 2 запроса, триггеры 3 ответа-ожидания, триггеры k занятости, дешифра торы 5 адреса назначения, блок 6 фор мирования тактов, узлы 7 определения возможности связи, блок 8 приоритета триггеры 9 передачи, блок 10 формирования сигналов приема, элементы за держки 11, элементы ИЛИ 12, шины 13 16 входов соответственно первой, вто рой, четвертой и третьей групп входов и шины 17 и 18 выходов соответственно первой, втором групп выходов Блок 6 формирования тактов (фигч предназначен для выраоотки синхронизирующих сигналов и содержит генератор 19 тактовых импульсов, элементы ИЛИ 20-22, элементы И , элементы НЕ 27-29, триггеры 30 и 31, входы 32. 2 Узел 7 определения возможности связи -канала (1 1 ,М) предназначен для определения возможности удовлетворения запроса модуля выдавшего запрос в данный момент времени, и содержит (фиг. З) элементы И 33 и 3 первой и второй групп, элементы НЕ 35 и 36 первой и второй групп, элементы ИЛИ 37 группы, элемент ИЛИ 38, i-ый вход . 39 первой группы входов узла, входы первой группы входов узла, входы 1 и второй и третьей групп входов узла, выход k3 узла. Блок 10 формирования сигналов Прйема предназначен для выработки сигналов приема и выдачи их в модуль, который принимает информацию. Блок 10 содержит (фиг. t) элементы И первой, второй, ...,-М-ой групп, эяе менты ИЛИ группы, входы k( соответствующих групп входов блока и it7 М+1-ОЙ группы входов блока. Модульньгй процессор (фиг. 5) содержит входы-выходы 48, модули , подключенные к устройству 50, и шины 51 для обмена информацией между модулями . Устройство работает следую1дим образом. При отсутствии запросов от модулей kS блок 6 вырабатывает синхросигналы СИ (фиг. 6). Модуль 3, желающий передать информацию (модуль-передатчик), выста вййет на соответствующей шине 1 ззпцос5 а на шине 13 адрес модуля 4,в который должна быть передана информация (модуля-приемника) .Информация,передаваемая между модулями 49, может быть трех типов: информация, на которую модуль-приемник должен выдать ответ (команда в специализированное арифметическое устройство, адрес данных при выполнении команды Чтение), После окончания цикла передачи модуль-передатчик возбуждают соответствующую шину 15 ответа-ожидания, единичное состояние которой при отсутствии сигнала на шине 1 запроса означает, что cooffeeVствующий модуль 9 находится а состоянии Ожидание. Этот модуль считается занятым для всех модулей, кроме того, от которого не ожидает ответj информация, являющаяся ответом на пре.дыдущую команду какого-либо модуля (результат операции из слециа Иизированного арифметического устройг ства, данные из оперативной памяти,), При желании передать такую информа . цию модуль-передатчик одновременно с шиной запроса. возбуждают шину 15 ответа-ожидания, единимное состояние которой при налимий на шине 14 означает, что передаваемая информация является ответной, информация, не являющая.ся ответом на предыдущую команду и не требующая ответа (адрес данных оперативной памяти и данные при выполнении команды Запись).

Каждый из модулей 49 может находиться в одном из следующих состояний :

Занят. Это означает, что модуль занят обработкой какой-либо информации и принять информацию от другого модуля не может. При этом он воз- буждает соответствующую шину 16 занятости.

Ожидает. Это означает, что модуль передавал какую-либо информацию для обработки другому модулю и ожидает от него ответ, этот модуль свободен только для приема ответной информации. Для всех остальных модулей он считается занятым и связь с ним не может быть установлена. В эт-ом состоянии модуль возбуждает соответствующую шину .15. Модуль, желающий выдать информацию в ответ на информацию от другого модуля, возбуждает вместе с шиной 14 шину 15. Одновременное наличие единичного сигнала на шинах 14 и 15 является признаком того, что передаваемая информация является ответной.

Свободен. Это означает, что модуль свободен и может принять информацию от любого другого модуля.

По синхросигналу СИ запросы от всех модулей 49 фиксируются на три ггерах 2. Одновременно в соответствующих регистрах 1 фиксируются адреса назначения. По этому синхросигналу СИ устанавливаются триггеры 4 занятых модулей и триггера 3 модулей, ко торые находятся в состоянии ожидания или хотят передать ответную информацию. По установленному триггеру 2 дешифратор 5 дешифрирует содержимое соответствующего регистра 1, определяя в какой из модулей хочетпередат информацию модуль-передатчик.

Сигналы с выходов дешифраторов 5 поступают в узел 7 и в блок 10. В каждый из узлов 7 поступают сигналы со всех триггеров 3 и со всех триггеров 4 чужих каналов. Анализируя состояние триггеров 4 и триггеров 3 узл

128

7, определяют возможность связи и при наличии такой возможности возбуждают выходы 43. Сигналы с выходов 43 поступают на-входы блока В приоритета, который определяет наиболее приоритетный из них.

. При наличии хотя бы одного установленного триггера 2 блок 6 вырабатывает син-хросигнал СИ. По синхросигналу СИд, поступающему на С-вход триггеров 9i устанавливается триггер 9, соответствующий наиболее приоритетному запросу. Сигнал с триггера 9 поступает на вход элемента ИЛИ 12 и на вход элемента задержки 11, которые служат для удлинения сигнала передачи Сигнал передачи с выхода элемента ИЛИ 12 по шине 18 поступает в соответствующий модуль 48, разрешая выдачу содержимого выходного регистра этого модуля на шины 51. Одновременно сигна передачи сбрасывает в этом модуле запрос и, если был установлен,ответ.

Сигнал с выхода триггера 9 поступает также в блок 10, который вырабатывает сигнал приёма информации и по соответствующей шине 17 передает его в модуль, который должен принять информацию. По этому сигналу модуль-приемник снимает с шин 51 необходимую информацию.

Синхросигнал СИ, заведен на входы сброса триггеров 9. По следующему синхросигналу СИ сбрасывается триггер 9 и снимаются сигналы передачи и приема на выходах 18 и 17. Сигнал передачи задерживается относительно сигнала приема для того, чтобы данные, принимаемые модулемгприемником, были заведомо верными. По этому синхросигналу СН сбрасывается триггер 2 и, установлен, триггер 3 того модуля, который передавал данные в предыдущем цикле. Одновременно устанавливаются или сбрасываются триггеры 3 и триггеры 4 тех модулей, которые изменили свое состояние. При наличии запросов от других модулей по синхросигналу СИ устанавливаются соответствующие триггеры 2 и работа устройства продолжается описанным способом.

Блок 6 работает следующим образом.

При отсутствии сигналов на входах 32 блока (сброшены все триггеры 2 запросов) триггеры 30 и 31 сброшены и элемент И 25 повторяет сигналы с выхода генератора 19. Выход элемента И.25 является первым выходом блока. 98 С этого выхода выдаются синхросигналы СИ, Предположим, в момент времени to (фиг. 6) на один из входов Н устройства поступил запрос. Посин- . хросигналу СИ установлен соответству ющий триггер 2 запроса и появится .сиг нал на одном из входов 32. По этому сигналу через элемент НЕ 27 и мерез элементы ИЛИ 20 и 21 запрещается сброс соответственно первого 30 и второго 31 триггеров. По очередному тактовому импульсу Т устанавливается триггер 30. По снятию тактового импульса Тд единичный уровень появляется на выходе триггера 30, запрещая, че ,рез элемент НЕ 29 выработку синхросигнала СИ элементом И 25 и разрешая выработку синхросигнала СИ элементом И З по следующему тактовому импульсу Tj . По тактовому импульсу Tj сбрасывается также триггер 30 и устанавливается триггер 31- По снятию так тового импульсу TJ на выходах тригге ров 30 и 31 появляется соответственно нулевой и единичный уровни. По так товому импульсу Тц триггер 30 устана ливается снова. По снятию тактового импульса Ttj единичный уровень появля ется на выходе триггера 30 jразрешая через элемент И 2k выработку сигнала сбро са, который поступает через элементы ИЛ 20 и 21 на входы сброса триггеров 30 и 31 и сбрасывает их. По следующему тактовому импульсу Tj- элемент И 2S вырабатывает o epeднoй синхросигнал СИ , по которому сбрасывается триггер 2 запроса того модуля, запрос которого удовлетворялся. Если других запросов нет, то блок снова вырабатывает только синхросигналы СИ. При появлении очередного запроса работа блока продолжается описанным способом. Узел 7 определения возможности св зи работает следующим образом. По входам 0 поступают сигналы из дешифратора 5 адреса назначения. По аходам 1 поступают сигналы с тригге ров 3 ответа-ожидания всех каналов, кроме собственного. По входам 2 поступают сигналы с триггеров t занятести чужих каналов. По входу 39 поступает сигнал с триггера 3 ответаожидания собственного канала. В каждый момент времени в каждом узле воз бужден только один из входов 40. Номер этой шины соответствует адресу модуля в который хочет передать инф 1маци 0 модуль-передатчик. Необходимыми условиями возможности связи являются: отсутствие единичного сигнала на входе k2 занятости, соответствующего возбужденному входу 40, отсутствие единичного сигнала на входе k ответа-ожидания, соответствующего возбужденному входу lO, или наличие единичного сигнала на этом входе и одновременное наличие единичного сигнала на входе 39. При отсутствии единичного сигнала на входе k2 через соответствующий элемент НЕ 36 устанавливается единичный уровень на третьем входе элемента И 3. При отсутствии единичного сигнала на с.оответствукядем входе tl через соответствующий элемент НЕ 35 или при . . наличии единичного сигнала на этом входе и при наличии единичного сиг-, нала на входе 39 через элемент И 33 и элемент ИЛИ 37 на вход элемента И З поступает единичный сигнал. При наличии единичных сигналов на первом и третьем входах соответствующего элемента И. 3 и при наличии единичного сигнала на втором, входе этого элемента, поступающего с соответствующего входа kQ, единичньтй сигнал с выхода элемента И 3 через элемент ИЛИ 38 поступает на выход 3 узла, определяя тем самым возможность связи. Блок 10 формирования сигналов приема работает следующим образом. По входам 4б на первые входы элементов И kk поступают сигналы с выходов дешифратора 5 адреса назначения,, номер которого соответствует номеру группы. По входам 7 на вторые входы элементов И Ц поступает CMrHajijсигнал с выхода триггера 9 пе редачи, номер которого соответствует номеру группы. В каждый момент време ни.возбужден не более чем один вход 7, номер которого соответствует номеру установленного триггера 9 передачи. Номер, установленного триггера 9 является номером модуля, который передает информацию в этом цикле связи. В группе элементов И, соответствующей установленному триггеру 9 передачи, возбужден первый вход только у одного из элементов И. Номер этого элемента И соответствует номеру модуля, в которьгй передана информация. Таким образом, из всех элементов И в каждый момент времени возбужден выход не более, чем у одного. Единичный сигнал с этого элемента И через соотвёт ствующий элемент ИЛИ kS фор((рует сигнал приема, номер которого соответствует номеру модуля, в который передается информация. Таким образом, устройство позволя ет достаточно простым образом и с небольшими затратами оборудования ор ганизовывать процессорный набор, содержащий модули, выполняющие различные функции. Модульный процессор, по строенный на базе этого устройства, отличается принципиальной простотой и возможностью наращивания. На основе предлагаемого устройства можно создавать как дешевые модульные процессоры с небольшой производительностью (процессоры, имеющие минимальный набор модулей ), так и высокопро изводительные модульные процессоры, имеющие в своем составе достаточно большое число высокоэффективных вы числительных модулей, причем алгорит ма связи в устройстве позволяет значительно повысить быстродействие самого устройства, процессора в целом за счет сокращения времени занятости шин связи служебной.информацией, Кроме To.ro, устройство обеспечивает модулям процессора дополнительные во можности, позволяя им взаимный попар ный обмен по инициативе любого из ни Формула изобретения , Многоканальное устройство.для сопряжения модулей процессора, содержащее блок приоритета, а в каждом канале регистр адреса назначения, триггер передачи, триггер занятости, триггер запроса, причем первые входы регистров адреса назначения, триг геров запроса, триггеров занятости соответствующих каналов соединены со ответственно со входами первой, второй и третьей групп входов устройства, выходы блока приоритета соединен с первыми входами триггеров передачи соответствующих каналов, о т л и Чающееся тем, что, с целью повышения быстродействия устройства, .в него введены блок формирования сиг налов приема и блок формирования так товы, а в каждый канал - триггер ответа-ожидания, дешифратор адреса наз начения, узел определения возможност связи, элемент задержки и элемент ИЛИ, причем первые входы триггеров ответа-ожидания каналов соединены с соответствующими входами четвертой группы входов устройства, выход триг гера ответа-ожидания i-oro канала (1 1,М) соединен с i-ыми входами первой группы входов узлов определения возможности связи всех каналов, выход регистра адреса назначения i-oro канала соединен с первым входом дешифратора адреса назначения того же канала, второй вход которого соединен с выходом триггера запроса того же канала и с i-ым входом блока формирования тактов, первый выход которого соединен со вторыми входами триггеров передачи, регистров адреса назначения, триггеров занятости, триггеров ответа-ожидания, а второй выход.- с третьими входами триггеров передачи, выходы дешифратора адреса назначения 1-ого канала соединены со входами второй группы входов узла определения возможности связи того же канала и с t-ой группой входов блока формирования сигналов приема, выход триггера занятости i-oro канала соединен с i-ым входом третьей группы входов j-oro узла определения возможности связи (j 1 ,М; ), выход узла определения возможности связи 1-ого канала соединен с i-ьгм входом блока приоритета, выход триггера передачи i-oro канала соединен с -ым входом М+1-ой группы входов блока формирования сигналов приема,.первый и второй входы элемента ИЛИ i-oro канала соединены соответственно с вь1ходом триггера передачи и выходов элемента задержки того же канала, входов подключенного к выходу триггера передачи того же канала, выходы блока формирования сигналов приема являются выходамипервой группы выходов устройства, а выходы элементов ИЛИ каналов - выходами второй группы выходов устройства. 2.Устройство по п. I, отличающее ся тем, что блок формирования тактов содержит генератор тактовых импульсов, выход которого соединен с первым входом первого элемента И, вторым , входом подключенного к выходу первого триггера и первому входу второго элемента И, выход которого соединен с первыми входами первого и второго элементов ИЛИ, вторыми входами подключенных через первый элемент НЕ к выходу третьего элемента ИЛИ, выходы которого являются соответствующими входами блока, второй вход второго элемента И соединен с выходом второго триггера и через второй элемент НЕ с первым входом второго триггера, выход первого триггера подключен через третий элемент НЕ к первым входам первого триггера и третьего элемента И и непосредственно к первому входу четвертого элемен та И, второй и третий входы первого триггера соединены соответственно с выходом генератора тактовых импульсо и выходом первого элемента ИЛИ, выхо ды первого элемента И и второго элемента ИЛИ подключены соответственно ко второму и третьему входам второго триггера, вторые входы третьего и четвертого элементов И подключены к выходу генератора тактовых импульсов третьи входы - к выходу второго элемента НЕ, а выходы - соответственно к первому и второму выходам блока. 3. Уctpoйcтвo по п. 1, отличающееся тем, что узел определения возможности связи 1-ого кана яа (,М ) содержит элемент ИЛИ, выход которого является выходом узла, две группы элементов И, две группы элементов НЕ и группу элементов ИЛИ, причем первые входы элементов И первой группы соединены с t-ым входом первой группы входов узла, второй вход го элемента И первой группы ( ) соединен с 1-ым входом второй группы входов узла и со входом J-oro элемента НЕ первой группы. 1/, выходы j-ых элементов И и НЕ первых групп соединены соответственно с первым и вторым входами j-oro элемента ИЛИ группы, выход которого подключен к первому входу j-oro элемента М второй группы, вторым входом соединенного с j-ым входом первой группы входов узла, третьим входом - через соответствующий элемент НЕ второй группы с j-ым входом третьей группы входов узла, а выходом - с j-ым входом элемента ИЛИ. , Устройство по п. 1,,о т л и чающееся тем, что блок формирования сигналов приема содержит группу элементов ИЛИ, выходы которых -являются соответствующими выхода , ми блока и М групп элементов И, причем -ый вход элемента ИЛИ группы (i, ,М) соединен с выходом i-oro элемента И К-ой группы, первый вход которого подключен к 1-ому входу К-ой группы входов блока, а второй вход - к К-ому входу М+1-ОЙ rpyn-t пы входов блока. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР (Г Зиоб, кл. G Об F 9/18, 1972. 2.Патент СШХ № 3800287Н, кл. 3 0-172.5. опублик. 197 (rtpoTOтип X

Й-$P

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения модулей процессора | 1982 |

|

SU1056176A2 |

| Устройство связи многопроцессорной вычислительной системы | 1988 |

|

SU1501081A1 |

| Устройство связи многопроцессорной вычислительной системы | 1988 |

|

SU1529243A1 |

| Устройство связи для вычислительной системы | 1980 |

|

SU924694A1 |

| Устройство для сопряжения каналов ввода-вывода с внешними устройствами | 1985 |

|

SU1277128A1 |

| Устройство связи для вычислительнойСиСТЕМы | 1979 |

|

SU802957A1 |

| Устройство для обмена данными между оперативной памятью и внешним устройством | 1984 |

|

SU1180908A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для обмена данными между оперативной памятью и внешними устройствами | 1985 |

|

SU1295404A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

JJ

//2.J

Jl

„АААЛАААААЛ

J-LJl

30

Авторы

Даты

1982-01-15—Публикация

1980-04-08—Подача