(S4J УСТРОЙСТВО ДЛЯ СИНХРОШ13АЦ|-1И СЧИТЫВАНИЯ ИНФОРМАЦИИ В ДОМЕННЫХ НАКОПИТЕЛЯХ

рем, a разрв гжость каяспого посседующего регистра адреса, начиная с третьего, равиз упвоешюй разрядности предьшуииего репсстра адреса, с расположекнымн в них хагчиками считьа а1шя, выходы которых подключены к другим входам остальных злементов сравнения.

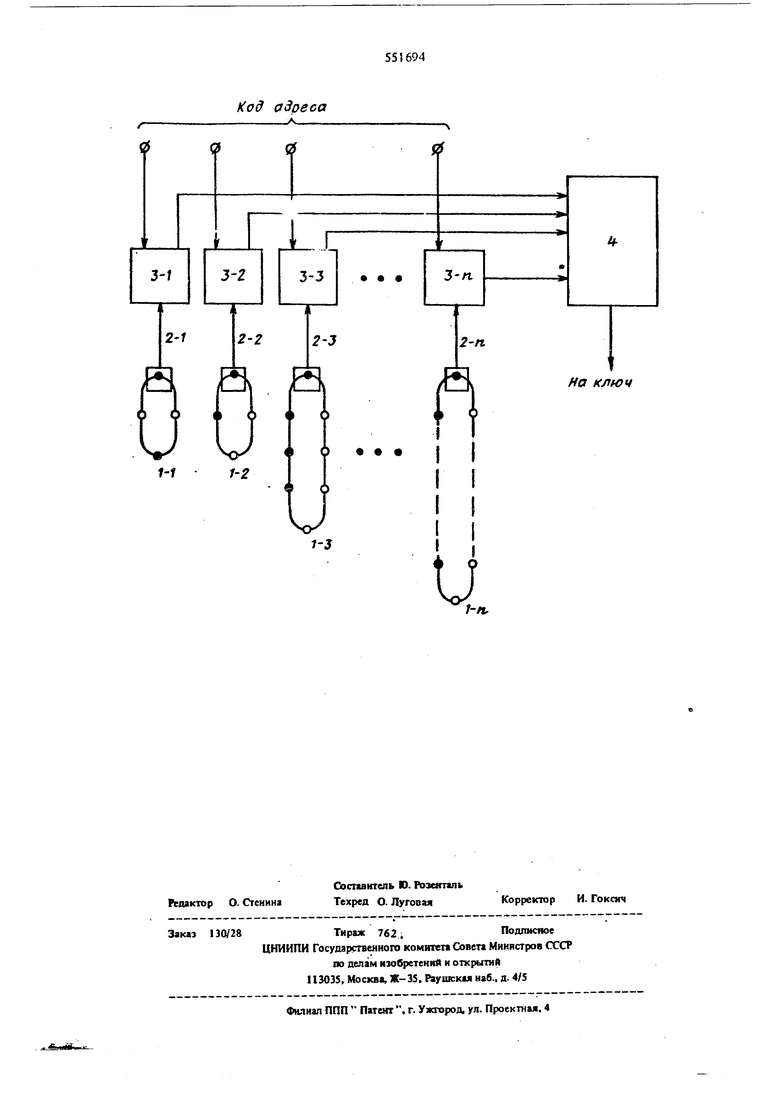

На чертеже изображена схема предлагаемого устройства для синхроиизацни считьюания информации в доменных накопителях.

Устррйство содерж1п п fog , N замкнутых ре1истров адреса i, - 1п в каждом из которых расположено по одному датшку считьгаания 2, -ь 2п, выходы которых соединены со входами элементов сравнения 3, + Зп, другие входы которых соединены со входом утромства. Выходы элементов сравнения подключены ко BXOIQ элемента И 4, выход которого соединен с выходом устройства. Первые хша регистра адреса имеют разрядность равную четырем- Каждый последующий регистр адреса имеет разрядность вдвое большую, чем предыдуший. Каждый регистр адреса заполнен строго определенной последовательностью доменов. .Для 1-го регистра эта последовательность представляет едгоши (наличие домена), и такое же количестве нулей (отс тствие домеча).

Устройство работает следующим образом.

В рабочем состоянии домены в регистрах адреса синхронно циркулируют, с выходов дапиков cfmтываиия получаем временную последовательность сигналов, реализующих N двухпозиционных п-разрядных кодов адреса. Kaждo y из N кояов адреса поставлено в соответствие кодовое слово в накопителе. Сигналы с п датчиков считывания поступают на п элементов сравнения, где необходимый кол адреса срзвиив.яется v --;(:,; кодом адреса. При (говиадеиии необходим : па адреса с текущим кодом адреса элемент И - ; л которым поданы сигналы с элементов ср; знения, выдает сигнал на садтьгеанке Heo6xoaHN oro кода п накопителе.

Предложенное устройство для сиихронизагщи операции считывания информац.чи позволяет значительно сократить габариты ЗУ и тем самьич повы сить плотность записи информации, что приведет к уменьшению стоимости бита информации и упрошеиню устройства.

Формула изобретения

Устройство для синхрк;низаш1И считывания информации в доменных накопителях, содержашее элементы сравнения, одни входы которых соединены со входом устройства, и регистр адреса с датчиком считьшания, выход которого подключен к другому входу одного из элементов сравнения, отличающееся тем, что, с целью уттрощения устройства, оно содержит элемент И, входы которого соединены с выходами элементов сравнения, а выход - с выходом устройства, и дополнительные (Pog J N - 1) регистров адреса, где N - число кодовых слов в накопителе, разрядность первых двух из которых равиа четырем, а разрядность каждого последуюц1его регистра адреса, начиная с третьего, равна удвоенной разрядности предыдущего регистра адреса, с расположенными в них датчиками считывания, выходы которых подключены к к другим входам остлльиых элементов сравнения.

u

/-Л.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления для доменной памяти | 1984 |

|

SU1265856A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1805503A1 |

| Устройство для контроля доменной памяти | 1982 |

|

SU1022216A1 |

| Устройство управления для памяти на цилиндрических магнитных доменах | 1984 |

|

SU1265855A1 |

| Запоминающее устройство с последовательным доступом | 1981 |

|

SU982084A1 |

| Постоянное запоминающее устройство | 1980 |

|

SU1080214A1 |

| Устройство для задержки информации | 1985 |

|

SU1287137A1 |

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

| Устройство для коррекции ошибок в блоках памяти | 1985 |

|

SU1257708A1 |

| Устройство управления буферным накопителем для доменной памяти | 1981 |

|

SU1275536A1 |

Авторы

Даты

1977-03-25—Публикация

1975-08-04—Подача