1

Изобретение относится к области вычислительной техники и может быть применено в цифровых вычислительных машинах иоследовательно-параллельного действия.

Известны устройства для деления, в которых осуществляется носледовательный ввод делимого в регистры устройства.

Недостатком этих устройств является время выполнения операции деления, равное 2.

Наиболе близким техническим решением к изобретению является устройство, содержащее сумматор, регистр делителя, вспомогательный регистр, регистр частного и блок управления, вход которого подключен к первому выходу регистра частного, первый вход которого подключен к первому выходу сумматора, первая группа поразрядных входов которого подключена к первым поразрядным выходам вспомогательного регистра, поразрядные входы которого подключены к поразрядным выходам сумматора.

Для повышения быстродействия в предлагаемое устройство введены дополнительно сумматор, регистр сдвига, элементы И и элемент ИЛИ, причем поразрядные выходы регистра делителя подключены к первой группе поразрядных входов дополнительного сумматора, вторая группа поразрядных входов которого подключена к соответствующим поразрядным выходам регистра сдвига, первый

вход которого подключен к выходу первого элемента И, первый вход которого подключен к входу устройства, а второй вход первого элемента И подключен к первому выходу блока управления. К первым входам второго и третьего элементов И, вспомогательного регистра и регистра частного, второй выход блока управления подключен к первым входам четвертого и пятого элементов И, выходы которых подключены к соответствующим вторым и третьим входам регистра частного и вспомогательного регистра и к второму входу регистра сдвига, второй вход пятого элемента И подключен к выходу элемента ИЛИ, два входа которого подключены к соответствующим выходам вспомогательного регистра и к второму входу третьего элемента И, другие два выхода вспомогательного регистра подключены соответственно к второму и третьему входам четвертого элемента И, к второму входу второго элемента И, выходы второго и третьего элементов И подключены к соответствующим входам регистра делителя, выходы доиолнительного сумматора

подключены к второй группе поразрядных входов сумматора.

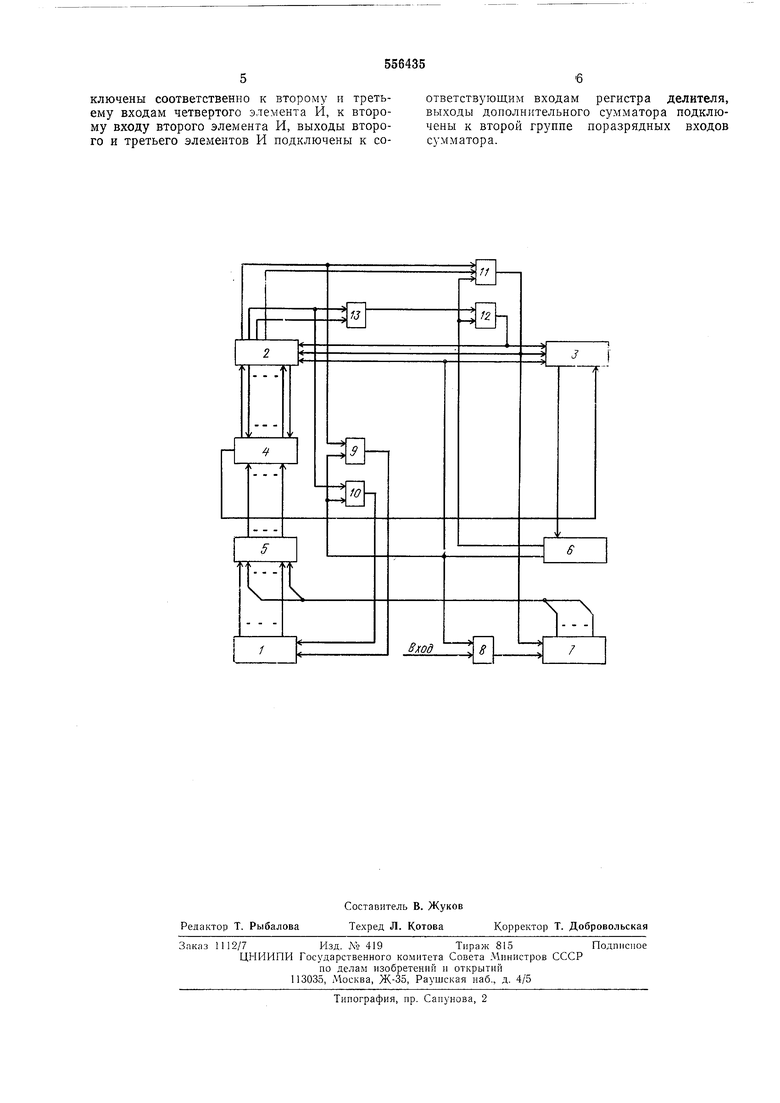

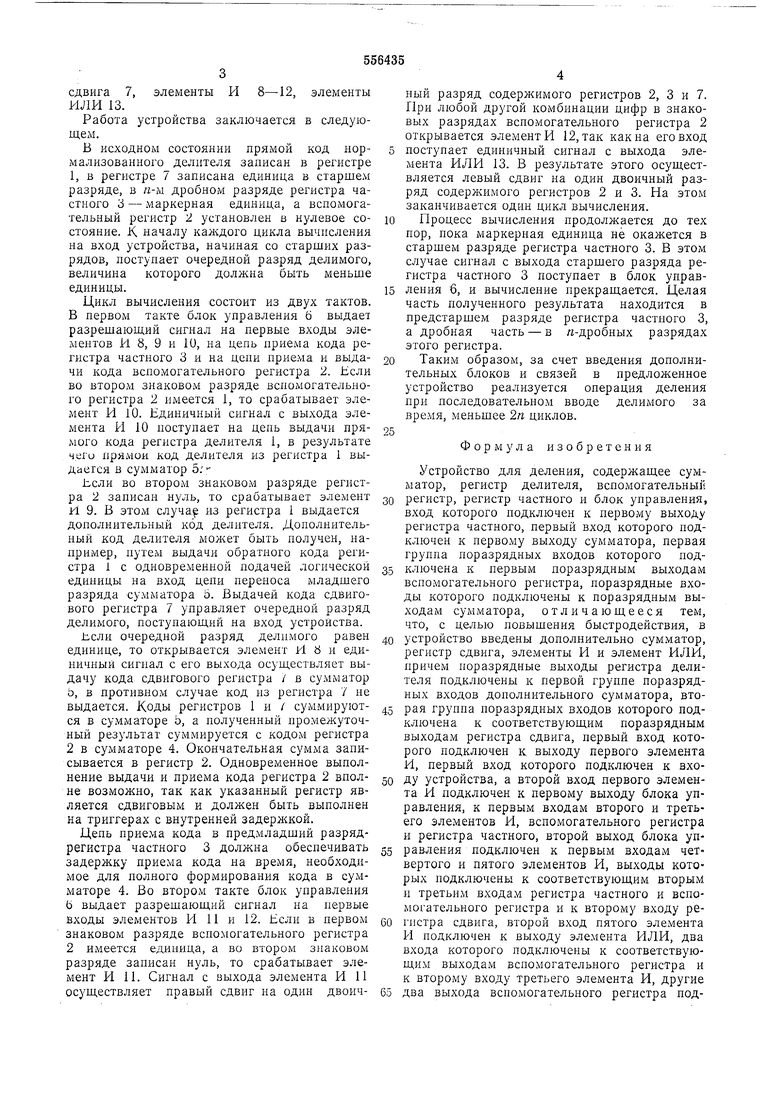

Иа чертеже показана схема устройства. Схема содержит регистр делителя 1, вспомогательный регистр 2, регистр частного 3,

сумматоры 4, 5, блок управления 6, регистр сдвига 7, элементы И 8-12, элементы ИЛИ 13. Работа устройства заключается в следующем. В исходном состоянии прямой код нор- 5 мализованного делителя записан в регистре 1, в регистре 7 записана единица в старшем разряде, в я-м дробном разряде регистра частного 3 - маркерная единица, а вспомогательный регистр 2 установлен в нулевое со- ю стояние. К началу каладого цикла вычисления на вход устройства, начиная со старших разрядов, поступает очередной разряд делимого, величина которого должна быть меньше единицы. Цикл вычисления состоит из двух тактов. В первом такте блок управления 6 выдает разрешающий сигнал на первые входы элементов И 8, 9 и 10, на цепь приема кода регистра частного 3 и на цепи приема и выда- 20 чи кода вспомогательного регистра 2. Нсли во втором знаковом разряде вспомогательного регистра 2 имеется 1, то срабатывает элемент И 10. Единичный сигнал с выхода элемента И 10 поступает на цепь выдачи пря- 95 люго кода регистра делителя 1, в результате чеги прямой код делителя из регистра 1 выдаегся в сумматор б;Ьсли во втором знаковом разряде регист ра 2 записан нуль, то срабатывает элемент JQ И 9. В этом случае из регистра 1 выдается дополнительный код делителя. Дополнительный код делителя может быть получен, например, путем выдачи обратного кода регистра 1 с одновременной подачей логической 35 единицы на вход цепи переноса младшего разряда сумматора 5. Выдачей кода сдвигового регистра 7 управляет очередной разряд делимого, поступающий на вход устройства. Ьсли очередной разряд делимого равен о единице, то открывается элемент И и и единичиый сигнал с его выхода осуществляет выдачу кода сдвигового регистра / в сумматор 5, в противном случае код из регистра 7 не выдается. Коды регистров 1 и / суммируют- ся в сумматоре Ь, а полученный промежуточный результат суммируется с кодом регистра 2 в сумматоре 4. Окончательная сумма записывается в регистр 2. Одновременное выполнение выдачи и приема кода регистра 2 впол- 50 не возможно, так как указанный регистр является сдвиговым и должен быть выполнен на триггерах с внутренней задерлшой. Цепь приема кода в предмладший разрядрегистра частного 3 должна обеспечивать 55 задержку приема кода на время, необходимое для полного формирования кода в сумматоре 4. Во втором такте блок управления b выдает разрешающий сигиал на первые входы элементов И И и 12. Ьсли в первом QQ знаковом разряде всномогательного регистра 2 имеется единица, а во втором знаковом разряде записан нуль, то срабатывает элемент И И. Сигнал с выхода элемента ИИ осуществляет правый сдвиг на один двоич- 65 15 ный разряд содержимого регистров 2, 3 и 7. При любой другой комбинации цифр в знаковых разрядах вспомогательного регистра 2 открывается элемент И 12, так как на его вход поступает единичный сигнал с выхода элемента ИЛИ 13. В результате этого осуществляется левый сдвиг на один двоичный разряд содержимого регистров 2 и 3. На этом заканчивается одни цикл вычисления. Процесс вычисления продолжается до тех иор, пока маркерная единица не окажется в старшем разряде регистра частного 3. В этом случае сигнал с выхода старшего разряда регистра частного 3 поступает в блок управления б, и вычисление прекращается. Целая часть полученного результата находится в предстаршем разряде регистра частного 3, а дробная часть - в л-дробных разрядах этого регистра. Таким образом, за счет введения дополнительных блоков и связей в предложенное устройство реализуется операция деления при последовательном вводе делимого за время, меньшее 2п циклов. Формула изобретения Устройство для деления, содержащее сумматор, регистр делителя, вспомогательный регистр, регистр частного и блок управления, вход которого подключен к первому выходу регистра частного, первый вход которого подключен к первому выходу сумматора, первая группа поразрядных входов которого подключена к первым поразрядным выходам вспомогательного регистра, поразрядные входы которого подключены к поразрядным выходам сумматора, отличающееся тем, что, с целью повышения быстродействия, в устройство введены дополнительно сумматор, регистр сдвига, элементы И и элемент ИЛИ, причем иоразрядные выходы регистра делителя подключены к первой группе поразрядных входов дополнительного сумматора, вторая группа поразрядных входов которого подключена к соответствующим поразрядным выходам регистра сдвига, первый вход которого подключен к выходу первого элемента И, первый вход которого подключен к вхоДУ устройства, а второй вход первого элемента И подключен к первому выходу блока управления, к первым входам второго и третьего элементов И, вспомогательного регистра и регистра частного, второй выход блока управления подключен к первым входам четвертого и пятого элементов И, выходы которых подключены к соответствующим вторым ц третьим входам регистра частного и вспомогательного регистра и к второму входу регистра сдвига, второй вход пятого элемента и подключен к выходу элемента ИЛИ, два входа которого подключены к соответствующим выходам вспомогательного регистра и к второму входу третьего элемента И, другие два выхода вспомогательного регистра подключены соответственно к второму и третьему входам четвертого элемента И, к второму входу второго элемента И, выходы второго и третьего элементов И подключены к со6

ответствующим входам регистра делителя, выходы дополнительного сумматора подключены к второй группе поразрядных входов сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1983 |

|

SU1141403A1 |

| Устройство для деления | 1976 |

|

SU662938A1 |

| Делительное устройство | 1983 |

|

SU1198512A1 |

| Устройство для деления чисел | 1981 |

|

SU1012241A1 |

| Устройство для вычисления дробнойРАциОНАльНОй фуНКции | 1979 |

|

SU842796A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для деления с плавающей запятой | 1979 |

|

SU860063A1 |

| Устройство для деления чисел | 1979 |

|

SU911518A1 |

| Устройство для деления двоичных чисел | 1980 |

|

SU1048472A1 |

Авторы

Даты

1977-04-30—Публикация

1974-09-13—Подача