достаточно иметь один контрольный разряд в каждой «-разрядной ячейке.

Однако таким образом нельзя исправить постоянные отказы более высокой кратности, что является недостатком ЗУ.

Для повышения надежности запоминающего устройства в нем выходы входного регистра подключены к одним из входов сумматора, другие входы которого соединены с выходамИ выходного регистра и входами блока коррекции ИНформации, выходы блока коррекции информации подключены к счетным входам выходного регистра, выходы блока кодирования соединены с входами входного регистра, выходы сумматора через буферный накопитель соединены с входами блока кодировамия информации.

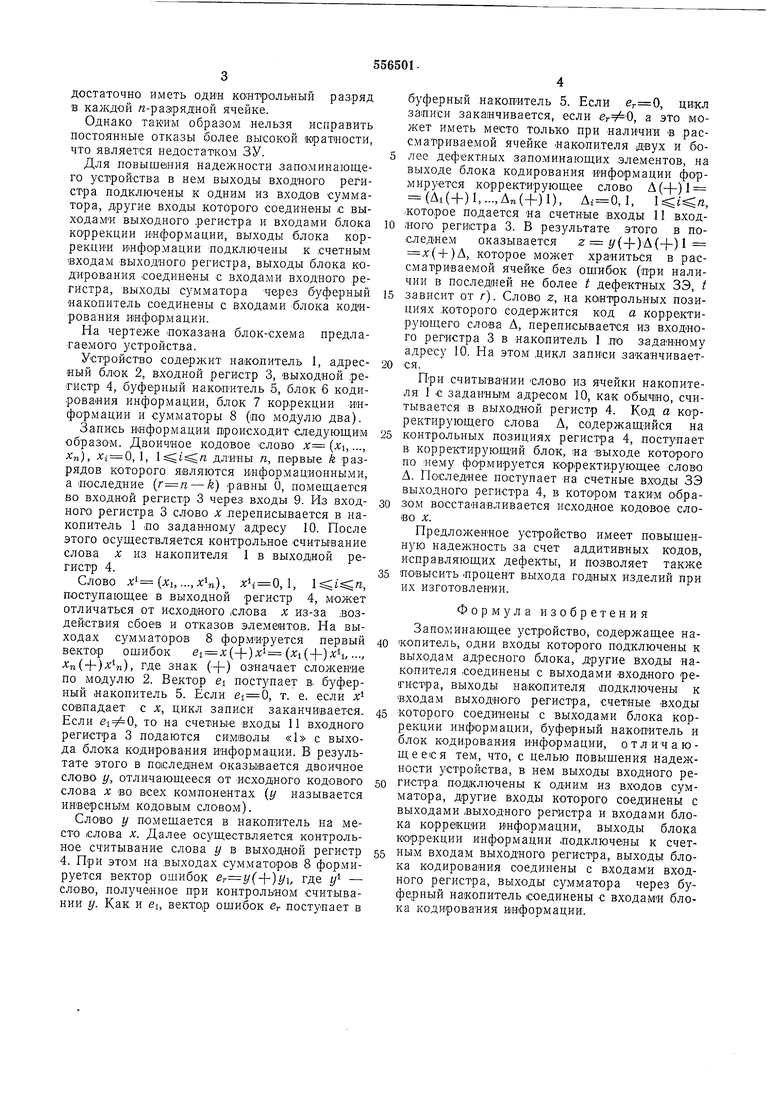

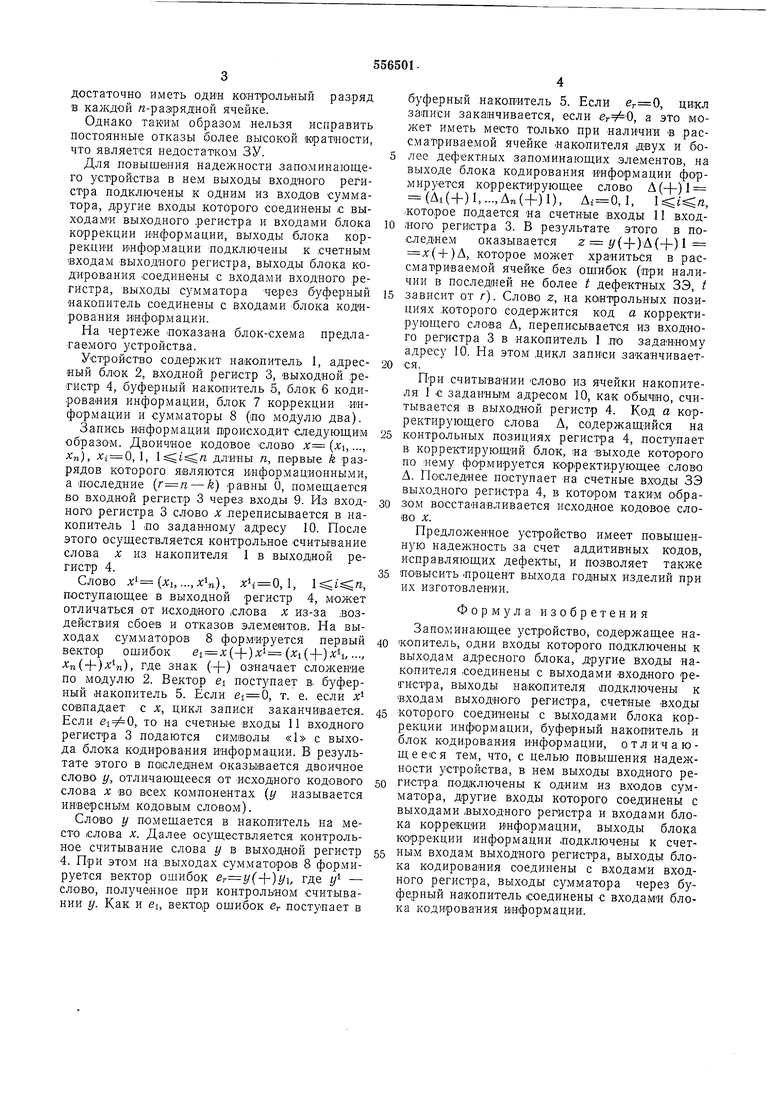

На чертеже показана блок-схема предлагаемого устройства.

Устройство содержит накопитель 1, адресный блок 2, входной регистр 3, выходной регистр 4, буферный накопитель 5, блок 6 кодирования информации, блОК 7 коррекции информации и сумматоры 8 (но модулю два).

Зались информации происходит Следующим образом. Двоичное кодовое слово х (xi,..., Хп), Хг 0, 1, длины п, пбрвые k разрядов которого являются информационными, а последние ( - k) равны О, помещается во входной регистр 3 через входы 9. Из входного регистра 3 слово х переписывается в накопитель 1 по заданному адресу 10. После этого осуществляется контрольное считывание слова X из накопителя 1 в выходной регистр 4.

Слово Х (Xi, ...,), , 1, ,

поступающее в выходной регистр 4, может отличаться от исходного слова х из-за .воздействия сбоев и отказов элементов. На выходах сумматоров 8 формируется первый вектор ошибок (-)(xi(),..., Хп{+), где знак (--f-) означает сложение по модулю 2. Вектор ei поступает в. б ферный накопитель 5. Если , т. е. если х совпадает с х, цикл записи заканчивается. Если , то на счетные входы 11 входного регистра 3 подаются сим1волы «1 с выхода блока кодирования информации. В результате этого в последнем оказьввается двоичное слово у, отличающееся от исходного кодового слова X во всех компонентах (у называется инверсным кодовым словом).

Слово у помещается в накопитель на место слова X. Далее осуществляется контрольное считывание слова у в выходной регистр 4. При этом на выходах сумматоров 8 формируется вектор ошибок (+)ь где у - слово, полученное при контрольном считывании у. Как и fii, вектор ошибок вг поступает в

буферный накопитель 5. Если , цикл записи заканчивается, если , а это может иметь место только при наличии в рассматриваемой ячейке накопителя двух и 5олее дефектных запоминающих элементов, на выходе блока кодирования информации формируется корректирующее слово А(-|-)1 (Ai(+)l,-..,A™(+)l), Аг-0,1, , -которое подается на счетн-ые входы 11 входиого регистра 3. В результате этого в последнем оказывается г г/(-|-) A(-j-) 1 х( + )А, которое может храниться в рассматриваемой ячейке без ошибок (при наличии в последней не более t дефектных ЗЭ, /

зависит от г). Слово z, на контрольных позициях которого содержится код а корректирующего слова А, переписывается из входного регистра 3 в накопитель 1 по заданному адресу 10. На этом дикл записи заканчивается.

При считывании слово из ячейки накопителя 1 с заданным адресом 10, как обычно, считывается в выходной регистр 4. Код а корректирующего слова А, содержащийся на

контрольных позициях регистра 4, пост)пает в корректирующий блок, на выходе которого по нему формируется корректирующее слово А. Последнее поступает на счетные входы ЗЭ выходного регистра 4, в котором таким о-бразом восстанавливается И1сходное кодовое слово X.

Предложенное устройство имеет повыщенную надежность за счет аддитивных кодов, исправляющих дефекты, и позволяет также

повысить процент выхода годных изделий при их изготовлении.

Формула изобретения

Запоминающее устройство, содержащее нако;питель, одни входы которого подключены к выходам адресного блока, другие входы накопителя соединены с выходами входного регистра, выходы накопителя подключены к «ходам выходного регистра, счетные входы

-которого соединены с выходами блока коррекции информации, буферный накопитель и блок кодирования информации, отличающееся тем, что, с целью повыщения надежности устройства, в нем выходы входного регистра подключены к одним из входов сумматора, другие входы которого соединены с выходами выходного регистра и входами блока коррекции информации, выходы блока коррекции информации подключены к счетным входам выходного регистра, выходы блока кодирования соединены с в.ходами входного регистра, выходы сумматора через буферный накопитель соединены с входами блока кодирования информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1980 |

|

SU926726A1 |

| Запоминающее устройство | 1981 |

|

SU972590A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU970478A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1043743A1 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1161994A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1805503A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1325569A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1238163A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1048520A1 |

| Запоминающее устройство с коррекцией информации | 1982 |

|

SU1070610A1 |

Авторы

Даты

1977-04-30—Публикация

1975-03-06—Подача