Изобретение о.тносится к запоминающим устройствам (ЗУ).

Известно запоминающее устройство с самоконтролем, содержащее основной и резервный накопители, блок постоянной памяти, блоки переадресации tlj«

Основным недостатком этого устройства является необходимость программирования блока постоянной памяти в процессе производства.

Наиболее близким техническим решением к изобретению является ЗУ, содержащие накопитель, соединенный с входным и выходным регистрами, элементы И и схемы сравнения.

Принцип работы этого ЗУ состоит в следующем.

Каждое слово сразу же после его записи в накопитель по заданному адресу считывается в выходной регистр и поступает на уст эойство .обнаружения ошибок. При отсутствии сяиибок или их необнаружении цикл записи заканчивается. При обнаружении ошибок записанное в накопитель слово инвертируется (заменяется на дополнение), факт инверсии слова обозначается записью 1 в специальном разряде записываемого слова, на этом цикл записи за-канчивается.

При выборке считанное из накопителя слово инвертируется, если в его индикаторном разряде оказывается символ 1 и не инвертируется, если О.

Таким образом, исправление двоичных постоянных отказов (дефектный запоминающий элемент. ЗЭ постоянно находится в состоянии О или 1 не10зависимо от того, что в него записывается) основано на предложении, что обрабатываемая информация, представленная в инверсной форме, не содержит ошибок t2j.

15

Недоста:тком этого ЗУ является то, что большая часть постоянных отказов кратности 2 и выше, то есть групповых, в ячейках накопителя не корректируется и приводит к оШибкги

20 считываемой информации. Это снижает надежность устройства.

Цель изобретения - повьаиение на;дежности ЗУ, а именно обеспечение безсхйибочных режимов, записи, хра25нения информации в накопителе, любое слово которого имеет до 1 t 3 смеж ных дефектов указанного выше типа.

Поставленная цель достигается тем, что в запс 4инающем устройстве с

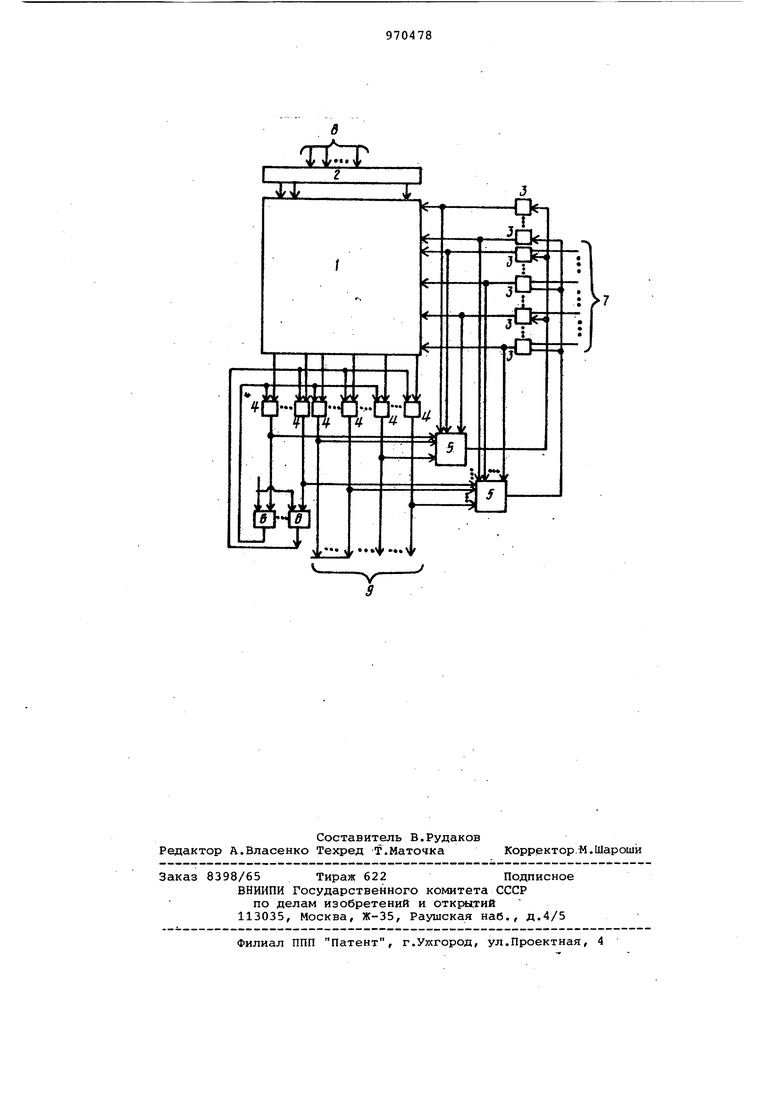

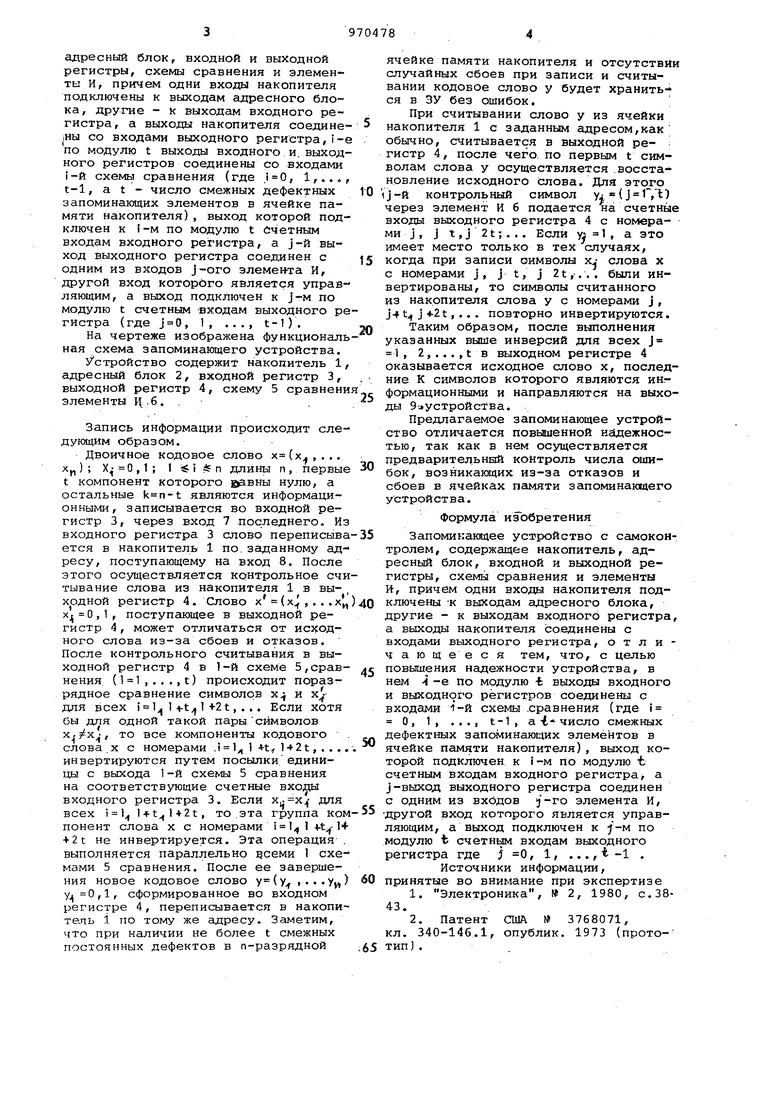

30 самоконтролен, содержащее накопитель. адресный блок, входной и выходной регистры, схемы сравнения и элементы И, причем одни входы накопителя подключены к выходам адресного блока, другие - к выходам входного регистра, а выходы накопителя соедине 1ны со входами выходного регистра,iпо модулю t выходы входного и. выход ного регистров соединены со входами i-й схемы сравнения (где ,, 1,.., t-1, at- число смежных дефектных запоминающих элементов в ячейке памяти накопителя), выход которой подключен к i-M по модулю t Счетным входам входного регистра, а j-й выход выходного регистра соединен с одним из входов j-oro элемента И, другой вход которого является управляющим, а выход подключен к j-м по модулю t счетным -входам выходного ре гистра (где , 1, ..,, t-1). На чертеже изображена функциональ ная схема запоминающего устройства, Устройство содержит накопитель 1 адресный блок 2, входной регистр 3, выходной регистр 4, схему 5 сравнени элементы Ц,б. .. Запись информации происходит следующим образом. Двоичное кодовое слово х(х.,... Xj,) ; X,- 0 ,1 ; I i п длины п , первые t компонент которого нулю, а остальные являются информационными, записывается во входной регистр 3, через вход 7 последнего. Из входного регистра 3 слово переписыва ется в накопитель 1 по.заданному адресу, поступающему на вход 8. После этого осуществляется контрольное счи тывание слова из накопителя 1 в выходной регистр 4. Слово х (х , . . .х1 ,1f поступающее в выходной регистр 4, может отличаться от исходного слова из-за сбоев и отказов. После контрольного считывания в выходной регистр 4 в 1-й схеме 5,срав нения (,...,t) происходит поразрядное сравнение символов х и х -для всех 1+-2t, . . . Если хотя бы для одной такой пары символов X, , то все компоненты кодового слова X с номерами .i 1 1 ty l + 2t,.., инвертируются путем посылки единицы с выхода 1-й схемы 5 сравнения на соответствующие счетные входы входного регистра 3. Если x, для всех 1 1 , то.эта группа ком понент слова х с номерами i I 1 21 не инвертируется. Эта операция выполняется параллельно дсеми 1 схе мами 5 сравнения. После ее завершения новое кодовое слово у(у .Уу ,1, сформированное во входном регистре 4, переписывается в накопи тель 1 по тому же адресу. Заметим, что при наличии не более t смежных постоянных дефектов в п-разрядной ячейке памяти накопителя и отсутствии случайных сбоев при записи и считывании кодовое слово у будет храниться в ЗУ без ошибок. При считывании слово у из ячейки накопителя 1 с заданным адресом,как обычно, считывается в выходной ре- гистр 4, после чего, по первым t символам слова у осуществляется .восстановление исходного слова. Для этого j-й контрольный символ У4 ( ) через элемент И 6 подается на счетные входы выходного регистра 4 с номерами j , j t, j 21; . .. Если yj 1 , a это имеет место только в тех случаях, когда при записи символы х слова х с номерами j, j t, j 2t,-... были инвертированы, то символы считанного из накопителя слова у с номерами j, J41 J 4-2t, .. . повторно инвертируются. Таким образом, после выполнения указанных выше инверсий для всех J 1, 2, . .. , t в выходном регистре 4 оказывается исходное слово х, последние К символов которого являются информационными и направляются на выходы Эаустройства. Предлагаемое запоминающее устройство отличается повьшенной надежностью , так как в нем осуществляется предварительнБГй койтроль числа свпибок, возникаквдих из-за отказов и сбоев в ячейках памяти запоминающего устройства. Формула изобретения Запоминающее устройство с самоконтролем, содержащее накопитель, адресный блок, входной и выходной регистры, схемы сравнения и элементы И, причем одни входы накопителя подключены -к выходам адресного блока, другие - к выходам входного регистра, а выходы накопителя соединены с входами выходного регистра, отличающееся тем, что, с целью повышения надежности устройства, в нем 4 -е по модулю -fe выходы входного и выходного регистров соединены с входами 1-й схемы .сравнения (где i О, 1, ..., t-1, а-i число смежных дефектных запсялинающих элементов в ячейке памяти накопителя), выход которой подключен к i-м по модулю t счетным входам входного регистра а j-выход выходного регистра соединен с одним из входов з-го элемента И, другой вход которого является управляющим, а выход подключен к -м по модулю t счетным входам выходного регистра где j 0, 1, ..., i -1 . Источники информации, принятые во внимание при экспертизе 1. Электроника, 2, 1980, с.3843. 2.Патент США 3768071, кл. 340-146.1, опублик. 1973 (прототип) .

в

JL

ф «« ф

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1238163A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1157575A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU934554A1 |

| Запоминающее устройство с исправлением ошибок | 1981 |

|

SU982098A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU926726A1 |

| Буферное запоминающее устройство с самоконтролем | 1982 |

|

SU1084890A1 |

| Устройство для приема дискретной информации | 1987 |

|

SU1501298A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1363312A1 |

| Ассоциативное запоминающее устройство | 1977 |

|

SU662972A1 |

| Запоминающее устройство с самоконтролем | 1977 |

|

SU645208A1 |

Авторы

Даты

1982-10-30—Публикация

1981-04-15—Подача