(54) ЦИФРОВОЙ ИНТЕРПОЛЯТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для воспроизведения функций | 1976 |

|

SU570047A1 |

| Устройство для вычисления полиномиальной функции от аналогового аргумента | 1990 |

|

SU1737444A1 |

| Нелинейный интерполятор | 1985 |

|

SU1267446A1 |

| Специализированный процессор | 1981 |

|

SU1023339A1 |

| Устройство для вычисления полиномов | 1982 |

|

SU1067509A1 |

| Генератор функций | 1984 |

|

SU1241219A1 |

| Устройство для воспроизведения полиномов | 1980 |

|

SU930321A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| ЭС | 1973 |

|

SU369589A1 |

| Специализированный процессор | 1977 |

|

SU723581A1 |

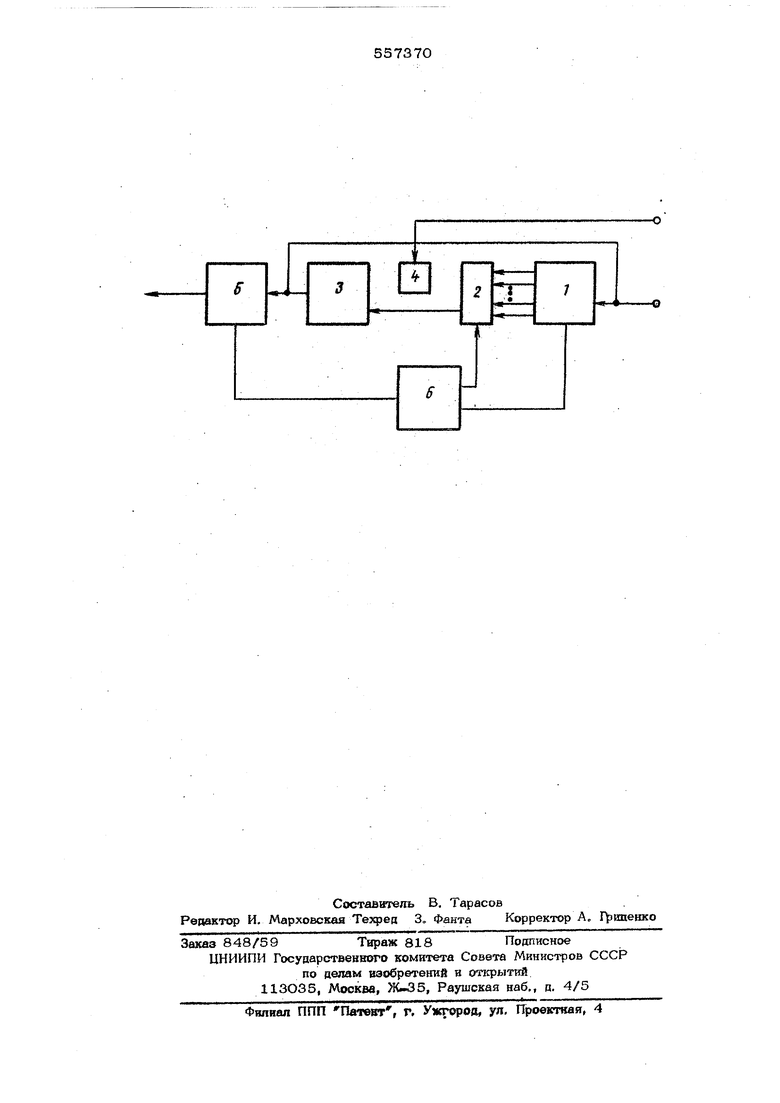

Изобретение относится к вычислительной технике, а именно к специализированным вычислителъныкз устройствам, выполняющим цифровую интерполяцию, а может использЬваться в устройствах управления, например, графопостроителями, дисплеями, станками с пр,огграммным управлением, Известно специализированное вычислительное устройство, выполняющее щ ровую 11нтерполяцию линий путем вычисления промежуточных значений между заданными точ ками, например устройство, выполняющее линейную интерполяцию l}. Использование в процедуре вычислеияя текущего значения полинома операции умно жения требует наличия в устройстве блока умножения, что сначительно усложняет кон струкцию а удорожает интерполятор. Наиболее блйзким по технической сущности к предложенному является цифровой интерполятор, снабженный запоминающим блоком koэффициeнтoв, вход которого является Ёходом устройства, а выход соединен со входом элемента И, первый выход которого подключен к первому входу сумматора, выход которого соединен со входом блока вывода, а утфавляюшие входы запоминающего блока коэффициентов, элемента И и блока вывода подключены к соответствуклцим выходам блока управления. Недостатком известного устройства является его сложность. Цель изобретения - упрощение цифрового интерполятора. Поставленная цель достигается тем, что цифровой интерполятор содержит регистр сдвига, причем вход регистра сдвига соединен со вторым выходом элемента И, а выход - со вторым входом сумматора, выход которого подключен ко входу запоминающего блока коэффициентов. На чертеже представлена блок-схема интерполятора. Интерполятор содержит последовательно соединенные запоминающий блок коэффициентов 1 для хранения текущих значений коэффициентов, элемент И 2, сумматор 3, второй вход которого соединен с выходом элемента И 2 через регистр сдвига 4, а выход дополнительно соединен со входом блоке памяти, блок вывоца. 5, а также бло управления 6, подключенвый к блоку па мяти, вентильной схеме и блоку вывода. В блок 1 перед началом работы вводят с0 начальные значения коэффициентов (к 0,1,2...Ш,где m - степень ннтер пхжируемого полинома), определенные по фсфмуле: Hii Ku m .,iVi.(U. lJ(,)t...(.i) Где IQ - аначенве аргумента в начально точке i, Ой проиэвоцной ч. « значение to в начальной точке пблввома р - прнрашевие аргумента, выбирае мое но формулеа где Q основание системы счисления, а 2 любое делое число. В регистр сдвига 4 вводится величина сдвига, равная ё , Вычисление полинома производится на основе соотношений c«(i-p)).c,,,(i.p);p, где k m -i, И1- 2,, 1. 0. Устройство работает следующим образом. По скг-налаы блока управления 6 из бл ка 1 через элемент И 2 на первый вход сумматора 3 поступает злаченне коэффициепта С а регистр сдвига 4 значение коэффициента С, , где оно сдвигается на разрядов. Сдвинутое значение коаффициевта С поступает на второй вхо сумматора. Результат сложения с выхода сумматора возвращается в блок 1 на мес прежнего значения коэффициента 0.. За гем на первый вход сумматора поступает значение С ,3 , а на второй - сдвинуто в сдвига новое значение козффициРезультат сложения возвращ ента С ется в блок ва место коэффициента С Далее эта процедура повторяется для 2... С„ - С. - CmкоЕффидиентов С Значение коэффициента С, являющееся значением полинома в текущей точке, оцгновременно с записью в блок 1 выводит ся через блок вывода 5. Для вычисления зна {ения полинома в следующей точке процедура повторяетдя. Предложенное устройство отличается от известных тем, что в нем операция умножения заменена более простой операцией сдвига; это позволяет избежать использования блока умножения - самого сложного и дорогого блока в подобных устройствах. В результате существенно утфошается конструкция устройств(а, повышается его надежность, и примерно на 4О- 5О% умешь шается стоимость изготовления. Кроме того, объем данных, вводимых в интерполятор для расчета последователи- наго ряда точек, значительно уменьшен, так как не требуется вводить в интерполятор значение Р на каждом шаге вычисления. Формула изобретения Цифровой интерполятор, содержащий запоминающий блок коэффициентов, вход которого является входом устройства, а выход соединен со входом элемента И, первый выход которого подключен к первому входу сумматора, выход которого соединен со входом блока вывода, а управляющие входы запоминающего блока коэффициентов, элемента И и блока вывода подключены к соответ ствующим выходам блока управления, о т л ичающийся тем, что, с целью упрощения цифрового интерполятора, он содержит регистр сдвига, причем вход регистра сдвига соединен со вторым выходом элемента И, а выход - со вторым входом сумматора, выход которого подключен ко входу запоминающего блока коэффициентов. Источники информации, принятые во внимание при экспертизе: 1.Патент США, кл. G 06 Р 15/46, № 3450865, 11. 1969. 2.Патент США, кл. G 06 Р 15/34, № 3813529, 8. 1974.

ш

Авторы

Даты

1977-05-05—Публикация

1975-06-05—Подача