стройства сравнения требуется tn триггеров, для цифровой суммирукл.цей схемы треуется примерно 4 п сумматоров по моду лю цва и столько же схем совпадения, т.е. всего около 9т1 функциональных элементов. Кроме того, для переключения порога обнаружения необходимо устанавливать /vn разрядное число, что требует сложной коммутации. Поэтому схема цифровог о коррелятора является громоздкой.

Целью изобретения является упрощение схемы, цифрового коррелятора.

Указанная цель достигается тем, чго иифровой коррвлягср содержит разрядные комбинированные триггеры памяти, тригге рьз отравления, первый и второй элементы И, сричем аервый и второй входы первого элемента И подключены соответственно к единичному н нулевому выходам сосециих разрядных триггерое памяти а третий и четвертый входы « соответст зенно к нупв вьгм выходам .триггеров управления прердз дущего и последующего разряцов, выход первого элемента И соединен с единичным взддом разрядного триггера управления, ну«. левой вход которого под слючен к выходу второго элемента И, выход Tpvirrepa управ. лония каждого разряда подключен ко вхо--ру асинхронвой установки нуля трштера jT- u-iH-TE предыдущего разряда и ко входу асиихроИ).-ой установки ециви ы триггера памЕти пес ч дующего разряда, единичдый зыход триггера памяти каждого разряда соедатген с соответствующим входом пере™ клкугателя, выход которого соединен с пер-вым входом порогового блока и с первым входом второго разрядного элемента И, второй вход которого понключек к нулевому выходу триггера памяти прерыдущего разряда, прямые и инверсные разрядные . ходы блока сравнен .подключены соответ ственно к первому и второму входам раз рядных комбинированных трргггеров памяти, второй вход порогового блока подключен к генератору тактовых импульсов,

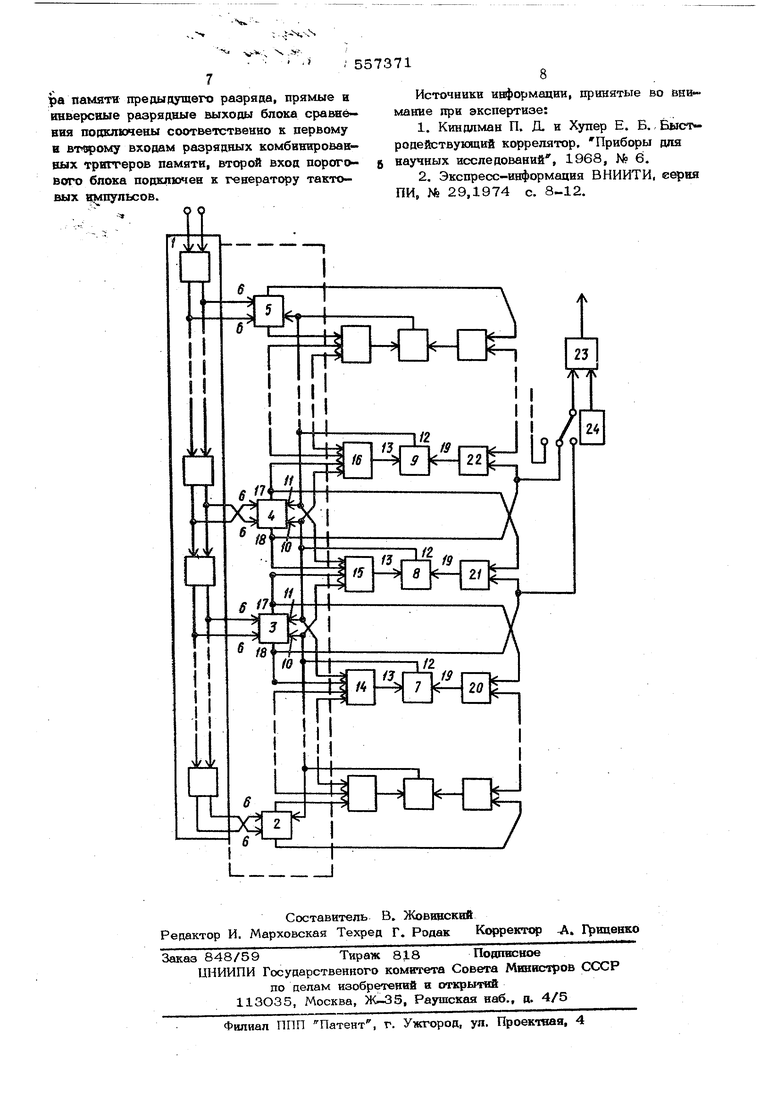

На чертеже представпеца функциоиапь «ная электрическая схема цифрового коррелятора. Коррелятор содержит бло.к сравае-ишя 1 кодового слова с опорныг-.ь выполнен кый на комбинированных трщ-Герах памяти 2, 3, 4, 5 , входы б синхронного ввода ин|)ормации которых подключены к выуо«дам блока сравнения (обрааующие блок пре° образования результата сравнения). Кане, дая пара соседних трт геров памяти охвачена обратной связью через трттеры управления 7, 8, 9 {например .Sj-l, охвачена обратной связью через ipurrep з фавле - ния 8)s np-i этом вхоп асинхроЕ ной установки нуля 10 КЗ-Седого триггера памяти,

яагфимер 4, и вход асинхронной установки единицы 11 триггера памяти 3 подключены к нулевому выходу 12 триггера управлеН1ш 8. Единичный вход 13 каждого триггера управления 7, 8, 9 подключен к выходу соответствующего элемента И 1А, 15, 16. Входы каждого элемента И, например 15, соединены с нулевым выходом 17 триггера памяти 3, единичным выходом 18 триг-, гера памяти 4 н нулевыми выходами 12 триггеров управлеивя 7 н 9, Нулевой вход 19 каждого трштера управления 7, 8, 9 подключен к выходу соответствующего эле мента И 20, 21, 22, входы каждого из которых, например элемента И 21, соединены с единичным выходом 18 триггера памвти 3 и нулевым выходом 17 триггера памяти 4. Единичные выходы 18 триггеров памяти 3..J5 через перекяючатеяь подключены ко вхоцу элемента И 23, выполняющему рол.ь порогового бпока. На второй ьхоц этого блока подань. инвертированные импульсы от геиэратора тактовых импуль сов 24, Выход э }:емента И 23 является выходом коррелятора.

Работа коррелятора происходит следую щим образом.

В началь5Пз1й момент времени блок нею .Я 1 се держит текущую информацию, триггерхл иамятк содержат информщпло, прэобразова1Д1ую предыдущим тактом, триг- геры управления 7, 8, 9 находятся в ну левом состоянии.

При действии тактового импульса в ycTV5 ройстве сравнения устанавливается очередное информационное, слово, а в триггеры памяти 2.5 записывается результат сравне ния этого слова с опорным словом. Сравнение достигае1ч:я комбинированием полярно0 стай сигналов, снимаемЬ1. с выходов блока сравнения 1. С тех выходов, ко орые соот ветствуют единичным разрядам опориого кодового слова, снимается прямая информация при подаче на входы синхронного ввода 6 триг-геров памяти 2-5, а с остальных вы.ходон -- инвертнрэаанная Поэтому, если информационное слово, установ генное в уст ройстве сравнения совпадает с опорным во всех разрядных, то в триггеры памяти 25 запишутся единицьг. При несовпадении разрядов записываются нули. Число нулей, записан гых в триггеры памяти, равно числу разрядоВг в которых Ш1(})ормационное сл1 во отличается от опорного.

После записи в триггеры памяти слова, начинается процесс преобразования этогх) слова в другое слово того же веса, но с упорядоченным расположением единиц и нулей: единицы располагаются ь старших разрядах, а нули в младших. Указанный процесс происходит следук щим образом. Пусгь,например, в триггер 3 (разряда старшего относительно 4) записан ноль, а в триггер 4 - едиЕйца. Тогда яа входы эл мента И 15 поступят четыре единицьь Две из них с нулевого выхода 17 триггера 3 и единичного выхода 18 триггера 4, две другие - с нулевых выходов 12 триггеров у-правления 7 и 9. Сигналом с выхода элемента И 15 триггер 8 установится в единичное состояние, и на его выходе 12 поя вится ноль, которым триггеры 3 и 4 переключаются в противоположные исходнйм состояния: триггер 3 - в единичное, три гер 4 - в нулевое. Произойдет перемещени единицы из младшего разряда (триггер 4) в старший (триггер 3) и одновременно нуля из старшего в младший. Пока триггер 8 находится в единичном состоянии соседние элементы И 14 и 16 заблокированы нулевым потенциалом с выхода J2 этого . Благодаря этому процесс переключения рассматриваемых триггеров 3 и 4 це влияет на состояние Соседних трйгтеров до установления устойчивых потевдиалов на выходах триггеров 3,4. После иереклгочения триггеров о и 4 на входы элем8Н1а И 21 с единичного выхода триггера 3 и с нулевого выхода триггера 4 поступят единицы п управления воз вратится в пулевое состояние. Нулевой сигнал, блокир тсщей элементы И 14 и 16, снимется, и рассматриваемый процесс пере- мещения нулей в младшие разряды продолжится. Конечным результатом описанного процесса будет формирование Т -разрядногослова, содержащего нули в младШих разрядах, а единицы в старших (11...1ОО...О) Согласно сказанному выше чкспо нулей в слове будет равгю числу несовпадающих разрядов в принятом слове и опорном. Обнаружение кодового слова, совпадающего с опорным с точностью до j-rix разрядов, производится с помощью анахгаза состояния триггера ( тп - 1 )го памяти 4 (считая триггер младшего разряда первым) Единичное состояние этого триггера явля- ется фактом обнаружения кодового слова с порогом обиару}кеиия тп . Упомянуты анализ состояния ( тп -ь -1 )- го триггера осутпествляе1ся элементом И 23, на один вход которого через переключатель порога подключен едшгичиый выход тригге- ра памяти 4, а на второй вхоц инвертированные тактог ые импульсы от генератора 24. Благодаря этому в течение первого поЛутакта, когда cocTOSiUHe тг иггеров г.амя- ти 2..5 нестационарно, элемент I- 2Л заблокирован, а в течение второго полутакта, когда состояние триггеров памяти является установившимся, формируется сигнал обнаружения. Предложенный коррелятор значительно проще известного. В нем для реализации устройства сравнения требуется п триггеров, для преобразователя 2 п триггеров н 2п элементов И, т.е. всето fr; функциональных элементов, что примерно вдвое меньше, чем содержит прототип. Если учесть, что триттерные устройства всех широко применяемых схемотехнических комцлексов содержат элементы И, то выигриш в количестве используемых элементов получается еще большим. Кроме того, гфедложенный коррелятор отличается от известного простотой установки необходкл ого порога обкару« ения si возможностью осу;4ествления автоматического его перек/$ку екня с помощью логических схем, что расширяет ф,уикд1гональ№ге возможности коррелятира. Формула и зоб е а и я Цифровой коррелятор с ncpt-fc;-Oj;. порогом для обкаруженая К(:.нузогс слова, со держащий генератор ТЛКТСБЫХ мпульсов, блок сравнения кодового слова с опормым; входы которого являются входами устрой сгва, пороговый блок, переключатель, отличаюшийсз тем, что, с целью упрощения, цифровой коррелятор содержит разрядные триггеры памяти, триггеры управления, первый и второй элементы И, причем первый и второй BXOPJ-J первого элемента И подключены соответственно к единичному и нулевому выходам соседних разрядных TpitrrepoB памяти, а третий и четвертый входы - соочветственко к нулевым выходам триггеров т.равле;1ия предыдущего и последующего разрядов, выход первого элемента И соединен с еди шчныл входом разрядного Tpiirreps управления нулевой вход которого подключен к выходу Второго элемента И, выход тр1пгтера управления каждого разряда пог-хключен ко входу асинхронной установки нупп трэттера памяти предыдущего разряда и ко входу асинхронной установки единицы триггера памяи последующего разряда, единичный выход риггера памяти каждого разряда соединен соответствующим входом переключателя, ыход которого соедипск с первым входом орогового блока г с первым входом второо разрядного элемента И, лторой вход ко- ррогч) подключен к пулог.ому г-,,гходу тригге

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой коррелятор | 1983 |

|

SU1129621A1 |

| Устройство управления для доменной памяти | 1984 |

|

SU1265856A1 |

| Устройство для контроля монотонности кодов | 1988 |

|

SU1575223A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1675849A1 |

| Устройство управления замещением дефектных элементов изображения | 1986 |

|

SU1394462A1 |

| Генератор псевдослучайных чисел | 1981 |

|

SU1013955A1 |

| Устройство для преобразования двоичного кода в код магнитного носителя | 1980 |

|

SU1148572A3 |

| Многоканальный цифровой коррелятор кодовых символов | 1977 |

|

SU691867A1 |

| Сигнализатор совпадения фаз | 1987 |

|

SU1515120A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

Авторы

Даты

1977-05-05—Публикация

1975-11-10—Подача