1

Изобретение относится к вычислительной технике и может быть использовано при построении устройств управления основной памятью ЦВМ.

Известно устройство 1 для передачи информации из основной памяти в каналы ввода- вывода, содержащее последовательно соединенные блок приема сигналов сопровождения из основной памяти, блок управления и регистр считанной информации.

Однако такое устройство имеет низкое быстродействие.

Наиболее близким к изобретению по технической сущности и достигаемому результату является устройство 2, содержащее блок буферизации информации, первый вход которого соединен с первым входом устройства, коммутатор адреса, выходом подключенный к второму входу блока буферизации информации, регистр считанной информации, первый вход и выход которого связаны соответственно с выходом блока буферизации информации и первым выходом устройства, регистр кода сопровождения, выход которого соединен с вторым выходом устройства.

Недостаток известного устройства состоит в том, что для каждого канала принимается только одно информационное слово. При следующих обращениях от этого же канала, считывание информации осуществляется из основной памяти, тем самым понижается быстродействие вычислительной мащины.

Цель изобретения - повыщение быстродействия устройства.

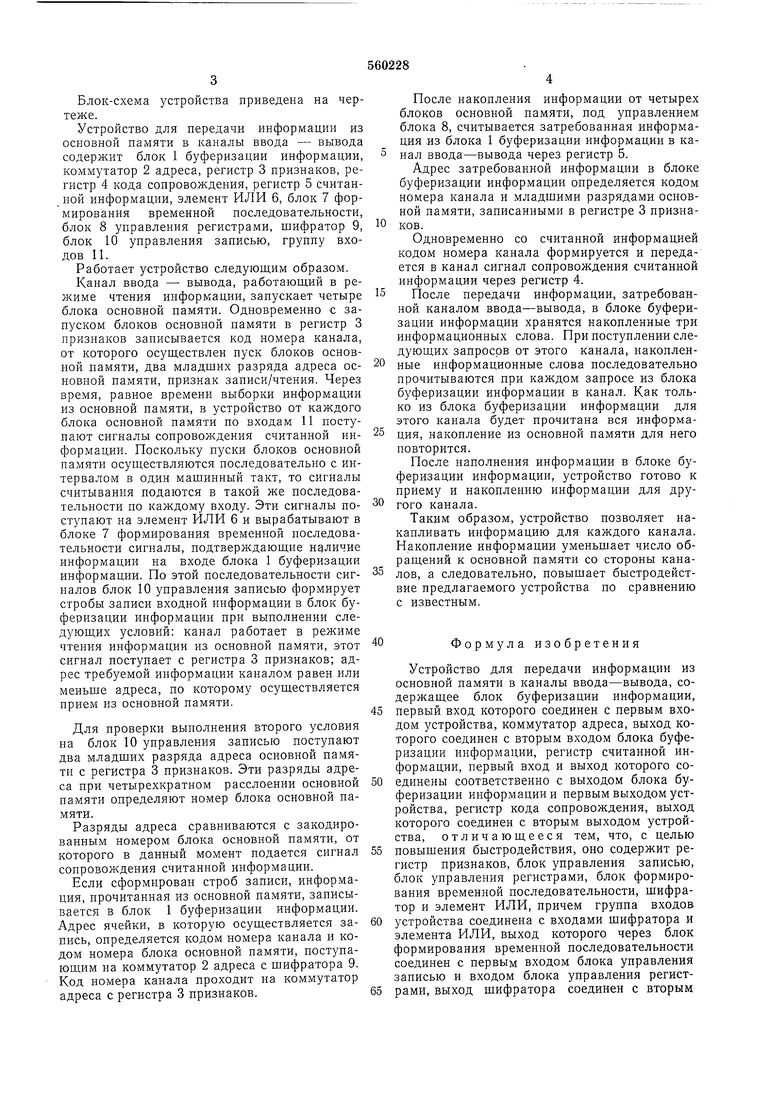

Это достигается тем, что в устройство ведены регистр признаков, блок управления записью, блок управления регистрами, блок формирования временной последовательности, щифратор и элемент ИЛИ. Группа входов устройства соединена с входами шифратора и элемента ИЛИ, выход которого через блок формирования временной последовательности связан с первым входом блока управления записью и входом блока управления регистрами, выход шифратора - с вторым входом блока управления записью и с первым входом коммутатора адреса. Первый выход регистра признаков подключен к третьему входу блока управления записью и второму входу коммутатора адреса, второй выход регистра признаков - к первому входу регистра кода сопровождения и третьему входу коммутатора адреса. Выход блока управления регистрами соединен с вторыми входами регистров считанной информации и кода сопровождения, а выход блока управления записью и вход регистра признаков - соответственно с третьим входом блока буферизации информации и с

0 вторым входом устройства. Блок-схема устройства приведена на чер теже. Устройство для передачи информации из основной памяти в каналы ввода - вывода содержит блок 1 буферизации информации коммутатор 2 адреса, регистр 3 признаков, регистр 4 кода сопровождения, регистр 5 считанной информации, элемент ИЛИ 6, блок 7 формирования временной последовательности, блок 8 управления регистрами, шифратор 9, блок 10 управления записью, группу входов 11. Работает устройство следующим образом. Канал ввода - вывода, работающий в режиме чтения информации, запускает четыре блока основной памяти. Одновременно с запуском блоков основной памяти в регистр 3 признаков записывается код номера канала, от которого осуществлен пуск блоков основной памяти, два младших разряда адреса основной памяти, признак записи/чтения. Через время, равное времени выборки информации из основной памяти, в устройство от каждого блока основной памяти по входам 11 поступают сигналы сопровождения считанной информации. Поскольку пуски блоков основной памяти осуществляются последовательно с интервалом в один машинный такт, то сигналы считывания подаются в такой же последовательности по каждому входу. Эти сигналы поступают на элемент ИЛИ 6 и вырабатывают в блоке 7 формирования временной последовательности сигналы, подтверждающие наличие информации на входе блока 1 буферизации информации. По этой последовательности сигналов блок 10 управления записью формирует стробы записи входной информации в блок буферизации информации при выполнении следующих условий: канал работает в режиме чтения информации из основной памяти, этот сигнал поступает с регистра 3 признаков; адрес требуемой информации каналом равен или меньше адреса, по которому осуществляется прием из основной памяти. Для проверки выполнения второго условия на блок 10 управления записью поступают два младших разряда адреса основной памяти с регистра 3 признаков. Эти разряды адреса при четырехкратном расслоении основной памяти определяют номер блока основной памяти. Разряды адреса сравниваются с закодированным номером блока основной памяти, от которого в данный момент подается сигнал сопровождения считанной информации. Если сформирован строб записи, информация, прочитанная из основной памяти, записывается в блок 1 буферизации информации. Адрес ячейки, в которую осуществляется запись, определяется кодом номера канала и кодом номера блока основной памяти, поступающим на коммутатор 2 адреса с шифратора 9. Код номера канала проходит на коммутатор адреса с регистра 3 признаков. После накопления информации от четырех блоков основной памяти, под управлением блока 8, считывается затребованная информация из блока 1 буферизации информации в канал ввода-вывода через регистр 5. Адрес затребованной информации в блоке буферизации информации определяется кодом номера канала и младшими разрядами основной памяти, записанными в регистре 3 признаков. Одновременно со считанной информацией кодом номера канала формируется и передается в канал сигнал сопровождения считанной информации через регистр 4. После передачи информации, затребованной каналом ввода-вывода, в блоке буферизации информации хранятся накопленные три информационных слова. При поступлении следующих запросов от этого канала, накопленные информационные слова последовательно прочитываются при каждом запросе из блока буферизации информации в канал. Как только из блока буферизации информации для этого канала будет прочитана вся информация, накопление из основной памяти для него повторится. После наполнения информации в блоке буферизации информации, устройство готово к приему и накоплению информации для друтого канала. Таким образом, устройство позволяет накапливать информацию для каждого канала. Иакопление информации уменьщает число обращений к основной памяти со стороны кана олов, а следовательно, повышает быстродействие предлагаемого устройства по сравнению с известным. Формула изобретения Устройство для передачи информации из основной памяти в каналы ввода-вывода, содержащее блок буферизации информации, первый вход которого соединен с первым входом устройства, коммутатор адреса, выход которого соединен с вторым входом блока буферизации информации, регистр считанной информации, первый вход и выход которого соединены соответственно с выходом блока буферизации информации и первым выходом устройства, регистр кода сопровождения, выход которого соединен с вторым выходом устройства, отличающееся тем, что, с целью повышения быстродействия, оно содержит регистр признаков, блок управления записью, лок управления регистрами, блок формироания временной последовательности, шифратор и элемент ИЛИ, причем группа входов стройства соединена с входами шифратора и лемента ИЛИ, выход которого через блок ормирования временной последовательности оединен с первым входом блока управления аписью и входом блока управления регистами, выход шифратора соединен с вторым

входом блока управления записью и с первым входом коммутатора адреса, первый выход регистра призпаков соединен с третьим входом блока управления записью и вторым входом коммутатора адреса, второй выход регистра признаков соединен с первым входом регистра кода сопровождения и третьим входом коммутатора адреса, выход блока управления регистрами соединен с вторыми входами регистров считанной информации и кода сопровождения, а выход блока управления записью и вход регистра признаков соединены соответственно с третьим входом блока буферизации информации и с вторым входом устройства.

Источники информации, принятые во внимание при экспертизе:

1.Патент США № 3376556, кл. 340-172.5, 1968.

2.Патент США № 3699530, кл. 340-172.5, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения основной памяти цифровой вычислительной машины с каналами ввода-вывода | 1977 |

|

SU689438A1 |

| Устройство для сопряжения каналовВВОдА-ВыВОдА C уСТРОйСТВОМ упРАВлЕНияОпЕРАТиВНОй пАМяТью МНОгОпРОцЕССОР-НОй ВычиСлиТЕльНОй МАшиНы | 1979 |

|

SU822168A1 |

| Устройство для сопряжения каналов ввода-вывода | 1975 |

|

SU559234A1 |

| Вычислительная система | 1977 |

|

SU670936A1 |

| Устройство буферизации команд процессора | 1983 |

|

SU1092506A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для сопряжения каналов ввода-вывода с устройством управления оперативной памятью | 1984 |

|

SU1265788A1 |

| Устройство сопряжения контролируемого процессора с основной памятью | 1980 |

|

SU877550A1 |

| Устройство для управления сверхоперативной буферной памятью мультипроцессорной ЭВМ | 1981 |

|

SU980097A1 |

Авторы

Даты

1977-05-30—Публикация

1976-01-04—Подача