ветсгвующйх вычислнтелыиых устройств, выход устройства управления соединен с первым входом репистра инструкций, второй вход которого соединен со вторым выходом запоминающего устройства, второй вход которого соединен с выходом репистра адреса.

В известных вычислительных системах определение момента окончания обработки п-роизБОДится с помогцью схем, обна.руживающ1их момент окончания переходного процесса, протекающего при вынолнении какой-либо операции, при этом для каждой операции необходима отдельная схема, учитывающая специфику выполнения этой операции. В связи с этим для обеспечения еозможности определения момента окончания операции необходимо большое количество оборудования.

Цель изобретения - уменьшепие количества оборудования.

Это достигается тем, что предлагаемая вычислительная система содержит Л дешифраторов, суммирующий блок, блок сравнения и счетчик тактов, иричем выходы коммутаторов соединены со входами соответствующих дешифраторов, выходы которых соединены с соответствующими входами суммирующего блока, выход которого соединен с первым входом блока сравнения, второй вход которого соединен с выходом счетчика тактов, а выход - со входом блока пуска и входо1м счетчика тактов.

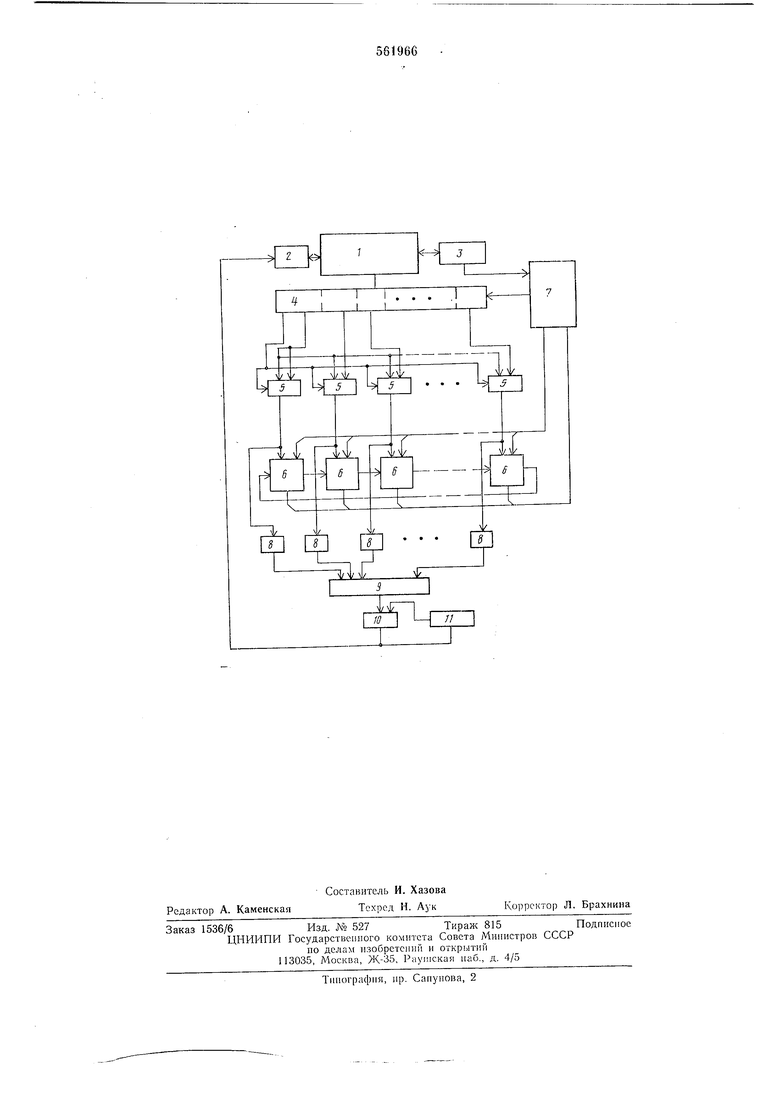

На чертеже показана схема предлагаемой вычислительной системы.

Вычислительная система содержит устройство управления 1, соединенное двусторонними связями с блоком пуска 2 и регистром адреса 3, регистр инструкций 4, разделенный на .V групп разрядов, N коммутаторов 5, N вычислительных устройств 6 и заноминающее устройство 7, причем первый выход первой группы разрядов регистра инструкций 4 соединен с первыми информационными входами- всех коммутаторов 5, вторые информационные входы которых соединены соответственно с 1-N групнами разрядов регистра инструкций 4. Управляющие входы всех коммутаторо:в 5 соединены с выходом «режим работы первой группы разрядов регистра инструкций 4. первые вход и выход запоминающего устройства 7 соединены соответственно с первыми выходаМИ и входами 1-Л вычислительных устройств 6, причем второй выход каждого вычислительного устройства 6 соединен со вторым входом последующего, а второй выход yV-ro вычислительного устройства 6 соединен со вторым входом первого вычислительного устройства 6, выходы каждого коммутатора 5 соединены с третьими входами соответствующих вычислительных устройств 6, выход устройства управления 1 соединен с первым входом регистра инструкций 4, второй вход которого соединен со вторым выходом запоминающего устройства 7, второй вход которого соединен с выходом регистра адреса 3.

Кроме того, вычислительная система содержит Л дещифраторов 8, суммирующий блок 9, блок сравнения 10 и счетчик тактов 11, причем выходы .коммутаторов 5 соединены со входами соответствующих дешифраторов 8, выходы которых соединены с соответствующими входами суммирующего блока 9, выход которого соединен с первым входом блока сравнения 10, второй вход которого соедипен с выходом счетчика тактов 11, а выход - со входом блока пуска 2 и входом счетчика тактов 11.

Вычислительная система работает следуюп им образом.

Начало каждого цикла обработки отмечается блоком иуска 2, разрешающего работу устройства управления 1. Инструкция, выполняемая В данном цикле, считывается из запоминающего устройства 7 по адресам регистра адреса 3 и принимается в регистр инструкций 4 при наличии соответствуюидьх сигналов устройства управления 1.

Содержимое регистра инструкций 4 через коммутаторы 5 поступает во все вычислительiHbie у стройства 6. Нри этом в зависимости от значения разряда «режим работы, входящего в состав регистра инструкций 4, на входы вычислительных устройств 6 нропускается либо код пер1зой группы разрядов регистра инструкций 4, либо код из той группы разрядов, номер которой совпадает с номером вычислительного устройства 6.

В соответствии с полученными инструкциями вычислительные устройства 6 выполняют операции над операндами, один из которых поступает из запоминающего устройства 7, а другой - из соседнего вычислительного устройства 6.

Таким образом, вычислительная система производит последовательную обработку Л операндов, причем результат операции, выполняемой в каждом вычислительном устройстве 6, является одним из операндов для операции, выполняемой в соседнем вычислительном устройстве 6.

Ввиду того, что длительность различных операций не одинакова, время обработки вычислительной системы групп из V операндов также не одинаково, так как содержимое всех V групп разрядов в регистре «нстрзкций 4 может быть различным.

Для определения момента окончания обработки содержимое каждой группы разрядов регистра инструкций 4 (инструкция вычислительного устройства 6) с коммутаторов 5 постунает на соответствующий дешифратор 8. Дешифраторы 8 производят преобразование кода числа, изображающего инструкцию Вычислительного устройства 6, в код числа, изображающего длительность выполняемой по этой инструкции операции в единицах времени, принятых для данной системы (например в долях такта).

Эти числа поступают в суммирующий блок 9, в качестве которого может быть использовам сумматор Л чисел, где подсчитывается суммарное время, неоСходимое для выподиения данной операции. Число с выхода суммирующего блока 9 ноступает в блок сравнения 10, в этот же блок подается сигнал с выхода счетчика тактов 11, подсчитывающего число тактов, прошедших с начала обработки группы операндов.

Когда число, поступающее из счетчика тактов И на входы блока сра;внения 10, становится больше (или равно) числа, поступающего «3 суммирующего блока 9, на выходе блока сравненпя 10 возникает сигнал окончания обработки, который поступает -в блок пуска 2. После этого блок пуска 2 может формировать сигнал начала нового цикла обработки для устройства управления 1.

Реализация предложенной вычислительной системы позволяет обеспечить высокое быстродействие системы при уменьшении количества оборудования, необходимого для выполнения блока окончания операций. Уменьшение оборудо 5ания достигается за счет того, что вместо узлов, индицирующих момент окончания операции в каждом вычислительном устройстве, применены дешифраторы 8, соединенные с выходами коммутаторов 5.

Формула изобретения

Вычислительная система для обработки чисел и .миогомерных векторов, содержащая устройство управления, соединенное двусторонними связями с блоком пуска и регистром адреса, регистр инструкций, разделенный па Л групп разрядов, Л коммутаторов. Л вычислительных устройств и запоминающее устройство, причем первый выход первой групны |разрядов регистра инструкций соединен с первыми информационными входами всех коммутаторов, вторые информационные вхолы которых соединены соответственно с 1-N г|)уппами разрядов регистра инструкций, а управляющие входы всех коммутаторов соединены с выходом «режим работы первой

группы разрядов регистра пнструкций, первые вход и выход запоминающего устройства соединены соответственно с первыми выходами и входами 1-Л вычислительных устройств, причем второй выход вычислительного устройства соединен со вторым входом последующего, а второй выход vV-ro вычислительного устройства соединен со вторым входом первого вычислительного устройства, выходы каждого коммутатора соедииены с третьими входами соответствующих вычислительных устройств, выход устройства управления соединен с первым входом регистра инструкций, ;второй вход которого соединен со вторым выходом запоминающего

устройства, второй вход которого соединен с .выходом регистра адреса, отличающаяс я тем, что, с целью уменьшения количества оборудования, она содержит Л дешифраторов, суммирующий блок, блок сравнения и

счетчик тактов, причем выходы коммутаторов соединены со входами соответствующих дешифраторов, выходы которых соединены с соответствующими входами суммирующего блока, выход которого соединен с первым входом

блока сравнения, второй вход которого соединен с выходом счетчика тактов, а выход i- со входом блока пуска и входом счетчика тактов.

Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство СССР № 330450, М. Кл.2 G 06F, 7/38, 03.06.70.

2.Л. Н. Преснухин, П. В. Нестеров, Цифровые вычислительные машины, «Высшая школ а, 1974, стр. 149-150 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления памятью | 1980 |

|

SU947866A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Система обработки нечеткой информации | 1987 |

|

SU1444803A1 |

| Устройство для исследования графов | 1984 |

|

SU1238099A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для формирования адресов процессора быстрого преобразования фурье | 1987 |

|

SU1499373A1 |

| Устройство для обмена информацией | 1983 |

|

SU1149239A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Арифметическое устройство по модулю | 1985 |

|

SU1285468A1 |

| Устройство для обработки информации | 1979 |

|

SU868765A1 |

Авторы

Даты

1977-06-15—Публикация

1975-01-03—Подача