(54) УСТРОЙСТВО СИНХРОНИЗАЦИИ С ДИСКРЕТНЫМ УПРАВЛЕНИЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации с дискретным управлением | 1978 |

|

SU758547A2 |

| Устройство синхронизации с дискретным управлением | 1974 |

|

SU562935A1 |

| Устройство поэлементного фазирования | 1980 |

|

SU928665A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

| Устройство тактовой синхронизации | 1981 |

|

SU978378A1 |

| Устройство тактовой синхронизации | 1985 |

|

SU1254589A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU906016A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1059689A1 |

| Устройство тактовой синхронизации | 1989 |

|

SU1720162A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU965005A2 |

1

Изобретение относится к технике .передачи сообщений дискретными сигНсшами и может использоваться в системах передачи кодограмм и команд телеуправления, в частности по коротковолновым радиоканалам.

Известно устройство синхронизации с дискретным управлением, содержащее селектор фронтов импульсов, дискриминатор ложной синхронизации, фазовый дискриминатор, усредняющий блок, делитель частоты, задающий генератор, три элемента ИЛИ и ключ 1 .

Однако данное устройство имеет недостаточную точность синхронизации.

По основному авт. св. № 758547 известно устройство синхронизации с дискретным управлением, содержащее селектор фронтов импульсов, выход которого подключен к входам дискриминатора ложной синхронизации и фазового дискриминатора, выходы которого через усредняющий блок подключены к одному из входов делителя частоты, к другому входу которого подключен выход задающего генератора, а выход делителя частоты подключен к управляющим входам фазового дискри-: минатора и дискриминатора ложной сиихронизации,содержащее также три элемента ИЛИ иключ,при этом выходаа фазового дискриминатора через первый элемент ИЛИ подключены к одному из входов ключа,к другому входу которого подключен выход дискриминатора ложной синхронизации,а выход ключа подключен к дополнительному входу делителя частоты через второй элемент, ИЛИ,к вто10рому входу которого подключен второй выход усредняющего блока, первый и второй выхода которого через третий элемент ИЛИ подключены к входу Запрет ключа. Для повышения точности

15 синхронизации в устройство введены дешифратор и блок задержки, причем дополнительный выход делителя частоты подключен к входу дешифратора, включенного между выходом делителя

20 частоты и управляющим входом дискримина тора ложной синхронизации, выход которого через блок задержки подклю- чей к другому входу ключа, вход которого соединен с другим входом бло25ка задержки 2 . ...

Однако у этого устройства большое , время вхождения в синхронизм, Цель изобретения - сокращение времени вхождения в синхронизм.

Для достижения поставленной цели в устройство синхронизации с дискретным управлением, содержащее селектор фронтов импульсов, выход которого подключен к входам дискриминатора ложной синхронизации и фазового дискриминатора, выходы которого через усредняющий блок подключены к одному из входов делителя частоты, к другому входу которого подключен выход задающего генератора, а выход делителя частоты подключен к управляющим входам фазового дискриминатора и дискриминатора ложной синхронизации, содержащее также три элемента ИЛИ и слюч, при этом выходы фазового дискриминаторй через первый элемент ИЛИ подключены к одному из входов ключа, к другому входу которого подключен выход дискриминатора ложной синхронизации, а выход ключа подключей к дополнител ному входу делителя частоты через второй элемент ИЛИ, к второму входу которого подключен второй выход усредняющего блока, первый и второй выходы которого через третий элемент ИЛИ подключены к входу Запрет ключа, содержащее также дешифратор и .блок задержки, причем дополнительный выход делителя частоты подключен к входу дешифратора, включенного между выходом делителя частоты и управляющим входом дискриминатора ложной синхронизации, выход которого через блок задержки подключен к другому вхду ключа, вход которого соединен с другим входом блока задержки, введен счетчик импульсов, входал которого соответственно соединены с выходом блока задержки и выходом первого элемента ИЛИ, а выход счетчика импульсов подключен к дополнительному входу третьего элемента ИЛИ.

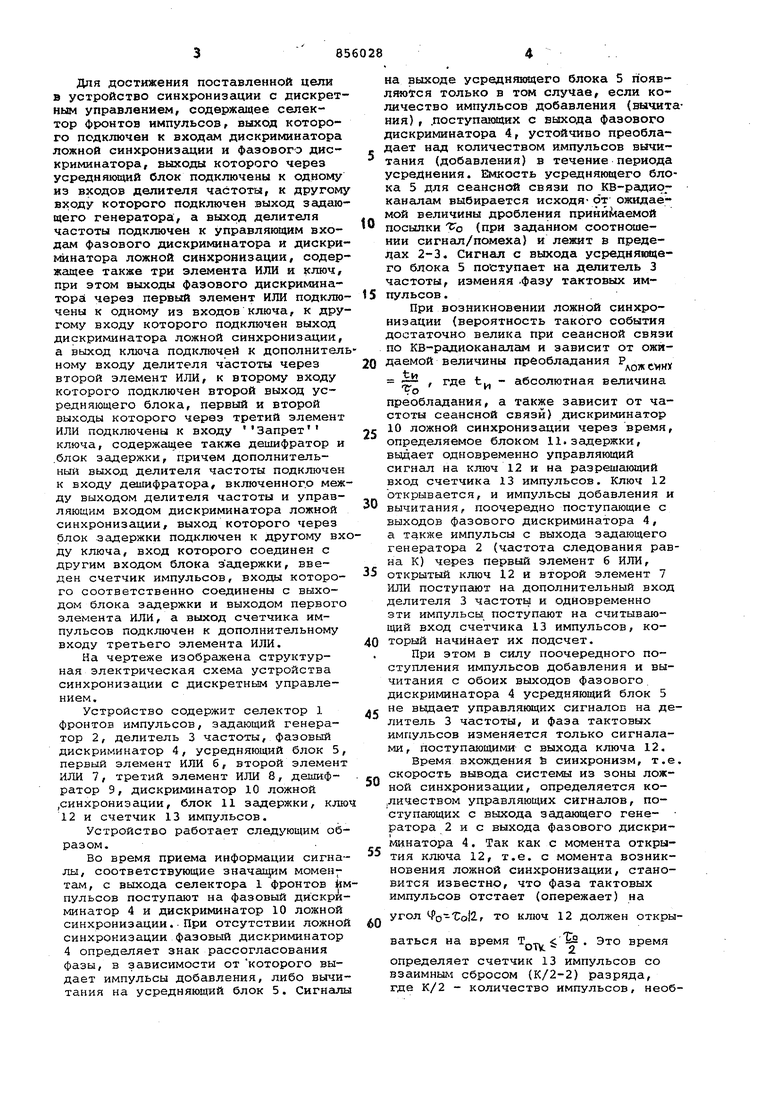

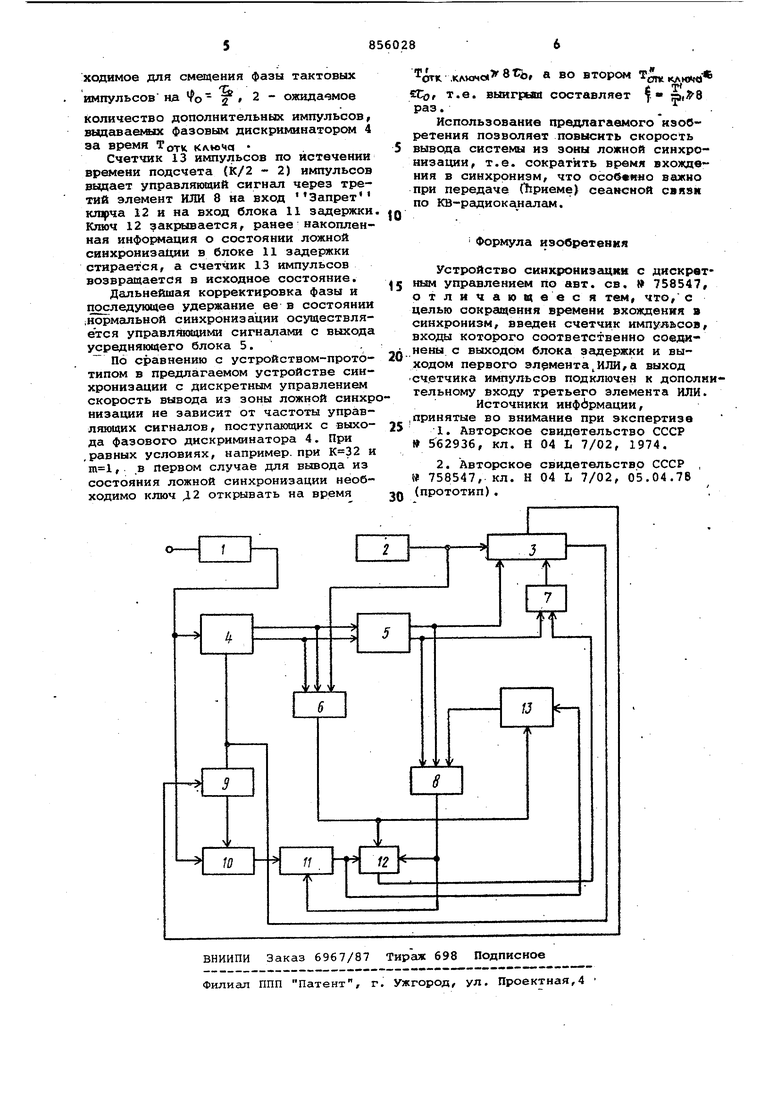

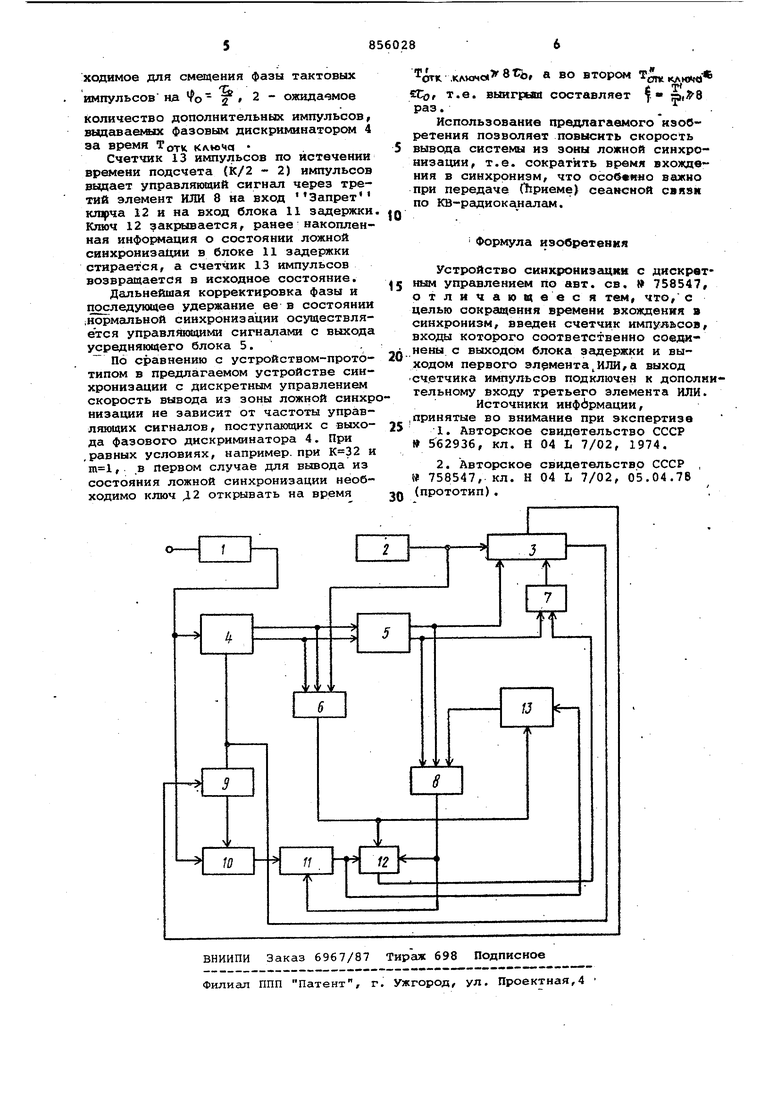

На чертеже изображена структурная электрическая схема устройства синхронизации с дискретным управлением.

Устройство содержит селектор 1 фронтов импульсов, задающий генератор 2, делитель 3 частоты, фазовый дискриминатор 4, усредняющий блок 5, первый элемент ИЛИ б, второй элемент ИЛИ 7, третий элемент ИЛИ 8, дешифратор 9, дискриминатор 10 ложной ,синхронизации, блок 11 задержки, клю 12 и счетчик 13 импульсов.

Устройство работает следующим образом..

Во время приема информации сигналы, соответствующие знача11р1М моментам, с выхода селектора 1 фронтов импульсов поступают на фазовый дискриминатор 4 и дискриминатор 10 ложной синхронизации.. При отсутствии ложной синхронизации фазовый дискриминатор 4 определяет знак рассогласования фазы, в зависимости от которого выдает импульсы добавления, либо вычитания на усредняющий блок 5. Сигналы

на выходе усреднякадего блока 5 появля ются только в том случае, если количество импульсов добавления (вычитния) , .поступающих с выхода фазового дискриминатора 4, устойчиво преобла дает над количеством импульсов вычитания (добавления) в течение периода усреднения. Емкость усредняющего блока 5 для сеансной связи по КВ-радиоканалам выбирается исходя-рт ожидаемой величины дробления принй аемой посылки ZTo (при заданном соотношении сигнал/помеха) и лежит в предедах 2-3, Сигнал с выхода усредняющего блока 5 поступает на делитель 3 частоты, изменяя .фазу тактовых импульсов .

При возникновении ложной синхронизации (вероятность такого события достаточно велика при сеансной связи по КВ-радиоканалам и зависит от ожидаемой величины преобладания Р

Aomewx tj2

tnабсолютная величина

где То

преобладания, а также зависит от частоты сеансной связи) дискриминатор 10 ложной синхронизации через время, определяемое блоком 11.задержки, вьйает одновременно управляющий сигнал на ключ 12 и на разрешающий вход счетчика 13 импульсов. Ключ 12 открывается, и импульсы добавления и вычитания, поочередно поступающие с выходов фазового дискриминатора 4, а также импульсы с выхода задающего генератора 2 (частота следования равна К) через первый элемент 6 ИЛИ, открытый ключ 12 и второй элемент 7 ИЛИ поступают на дополнительный вход делителя 3 частотьд и одновременно эти импульсы поступают на считывающий вход счетчика 13 импульсов, который начинает их подсчет.

При этом в силу поочередного поступления импульсов добавления и вычитания с обоих выходов фазового дискриминатора 4 усредняющий блок 5 не выдает управляющих сигналоБ на делитель 3 частоты, и фаза тактовых импульсов изменяется только сигналами, поступающими с выхода ключа 12.

Время вхождения fe синхронизм, т.е скорость вывода системы из зоны ложной синхронизации, определяется количеством управляющих сигналов, поступающих с выхода задающего генератора 2 и с выхода фазового дискриминатора 4. Так как с момента открытия ключа 12, т.е. с момента возникновения ложной синхронизации, становится известно, что фаза тактовых импульсов отстает (опережает) на

угол Ч о-Со12г то ключ 12 должен открыТо

ваться на время Т $

Это время

определяет счетчик 13 импульсов со взаимным сбросом (К/2-2) разряда, где К/2 - количество импульсов, необ

Авторы

Даты

1981-08-15—Публикация

1978-12-18—Подача