(54) УСТРОЙСТВО СИНХРОНИЗАЦИИ С ДИСКРЕТНЫМ

УПРАВЛЕНИЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации с дискретным управлением | 1978 |

|

SU856028A2 |

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

| Устройство синхронизации с дискретным управлением | 1974 |

|

SU562935A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU938419A1 |

| Устройство тактовой синхронизации | 1985 |

|

SU1254589A1 |

| Устройство тактовой синхронизации | 1981 |

|

SU978378A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1059689A1 |

| Устройство синхронизации | 1981 |

|

SU1003376A1 |

| Устройство тактовой синхронизации с пропорциональным регулированием | 1978 |

|

SU731604A2 |

| Устройство тактовой синхронизации | 1980 |

|

SU906016A1 |

1

Изобретение относится к устройствам передачи сообщений дискретными сигналами и может использоваться в системах передачи коротких кодограмм и команд телеуправления.

По основному авт. св. № 562935 известно устройство синхронизации с дискретным управлением, содержащее селектор фронтов импульсов, выход которого подключен ко входам дискриминатора ложной синхронизации и фазового дискриминатора, выходы которого подключены к усредняющему блоку и первому элементу ИЛИ, выход которого через ключ и второй элемент ИЛИ подключен к дополнительному входу делителя . частоты, первый и второй выходы усредняющего блока подключены через третий элемент ИЛИ ко входу «запрет ключа и одновременно первый выход связан со вторым элементом ИЛИ, а второй выход подключен к делителю частоты, к второму входу которого подключен выход задающего генератора, а выход делителя частоты подключен к управляющему входу фазового дискриминатора.

Однако такое устройство имеет невысокую точность синхронизации.

Цель изобретения - повыщение точности синхронизации.

Это достигается тем, что в устройство синхронизации с дискретным управлением, содержащее селектор фронтов имульсов, зас дающий генератор , делитель частоты, фазовый дискриминатор, блок усреднения, элементы ИЛИ, дискриминатор ложной синхронизации и ключ, введены дещифратор и блок задержки, причем дополнительный выход делителя частоты подключен к входу дешифЮ ратора, включенного между выходом делителя частоты и управляющим ьходом дискриминатора ложной синхронизации, выход которого через блок задержки подключен к другому входу ключа, вход которого соединен с другим входом блока задержки.

15

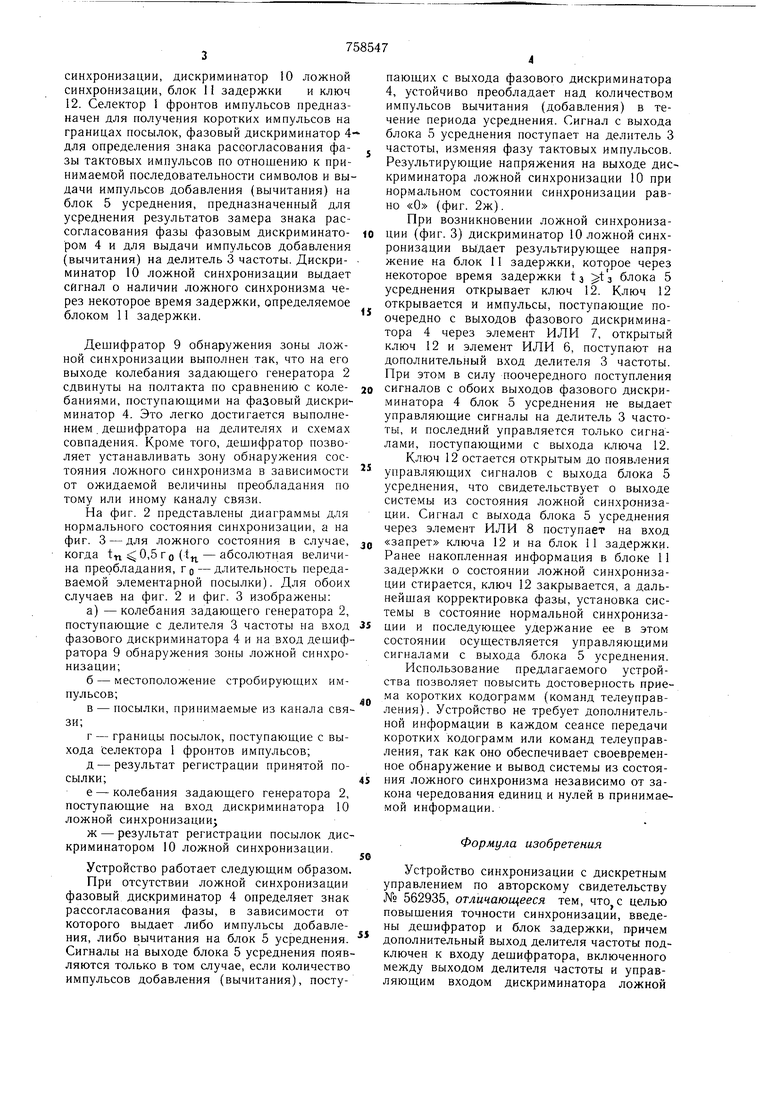

На фиг. 1 представлена структурная электрическая схема предлагаемого устройства; на фиг. 2 и 3 приведены диаграммы, поясняющие принцип работы устройства.

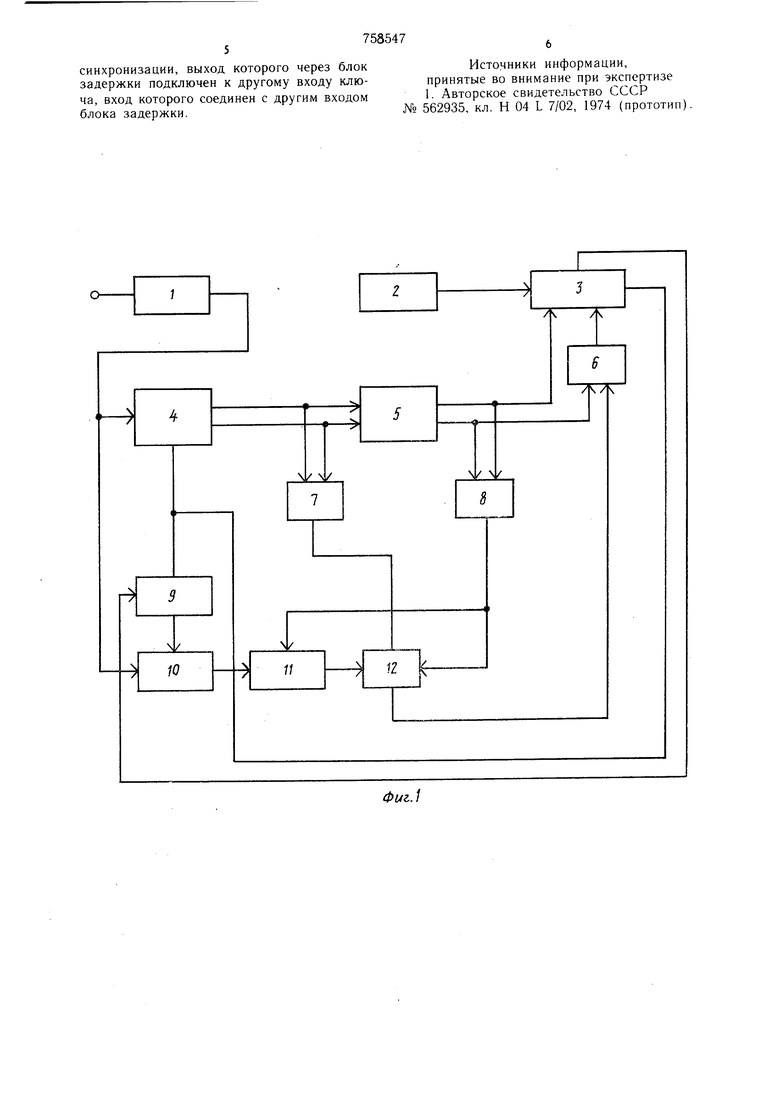

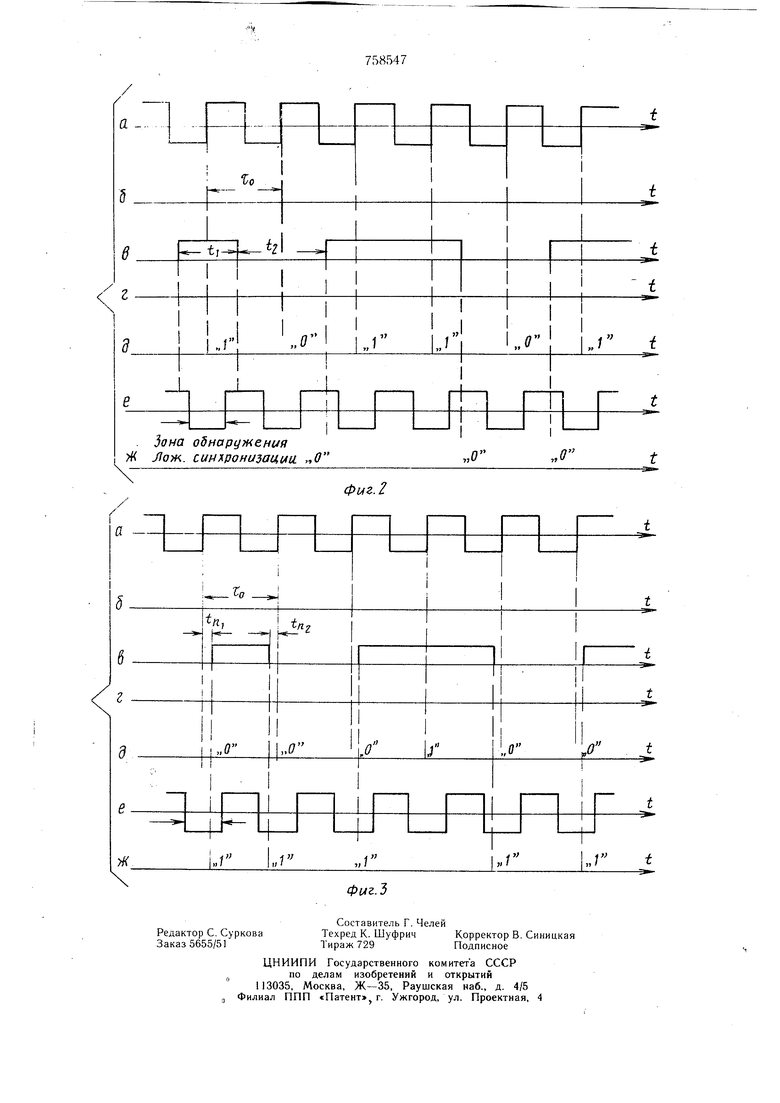

Устройство синхронизации с дискретным 20 управлением содержит селектор 1 фронтов импульсов, задающий генератор 2, делитель 3 частоты, фазовый дискриминатор 4, блок 5 усреднения, элементы ИЛИ 6, 7 и 8, дещифратор 9 обнаружения зоны ложной синхронизации, дискриминатор 10 ложной синхронизации, блок 11 задержки и ключ 12. Селектор 1 фронтов импульсов предназначен для получения коротких импульсов на границах посылок, фазовый дискриминатор 4для определения знака рассогласования фазы тактовых импульсов по отношению к принимаемой последовательности символов и выдачи импульсов добавления (вычитания) на блок 5 усреднения, предназначенный для усреднения результатов замера знака рассогласования фазы фазовым дискриминатором 4 и для выдачи импульсов добавления (вычитания) на делитель 3 частоты. Дискриминатор 10 ложной синхронизации выдает сигнал о наличии ложного синхронизма через некоторое время задержки, определяемое блоком 11 задержки. Дешифратор 9 обнаружения зоны ложной синхронизации выполнен так, что на его выходе колебания задаюш,его генератора 2 сдвинуты на полтакта по сравнению с колебаниями, поступающими на фазовый дискриминатор 4. Это легко достигается выполнением дешифратора на делителях и схемах совпадения. Кроме того, дешифратор позволяет устанавливать зону обнаружения состояния ложного синхронизма в зависимости от ожидаемой величины преобладания по тому или иному каналу связи. На фиг. 2 представлены диаграммы для нормального состояния синхронизации, а на фиг. 3 - для ложного состояния в случае, когда tn 0,5 г g (1 - абсолютная величина преобладания, Гр - длительность передаваемой элементарной посылки). Для обоих случаев на фиг. 2 и фиг. 3 изображены: а) - колебания задающего генератора 2, поступаюшие с делителя 3 частоты на вход фазового дискриминатора 4 и на вход дешифратора 9 обнаружения зоны ложной синхронизации;б - местоположение стробирующих импульсов;в - посылки, принимаемые из канала связи;г - границы посылок, поступаюш,ие с вы.хода Селектора 1 фронтов импульсов; д-результат регистрации принятой посылки;е - колебания задающего генератора 2, поступающие на вход дискриминатора 10 ложной синхронизации ж - результат регистрации посылок дискриминатором 10 ложной синхронизации. Устройство работает следующим образом. При отсутствии ложной синхронизации фазовый дискриминатор 4 определяет знак рассогласования фазы, в зависимости от которого выдает либо импульсы добавления, либо вычитания на блок 5 усреднения. Сигналы на выходе блока 5 усреднения появ ляются только в том случае, если количество импульсов добавления (вычитания), поступающих с выхода фазового дискриминатора 4, устойчиво преобладает над количеством импульсов вычитания (добавления) в течение периода усреднения. Сигнал с выхода блока 5 усреднения поступает на делитель 3 частоты, изменяя фазу тактовых импульсов. Результирующие напряжения на выходе дискриминатора ложной синхронизации 10 при нормальном состоянии синхронизации равно «О (фиг. 2ж). При возникновении ложной синхронизации (фиг. 3) дискриминатор 10 ложной синхронизации выдает результирующее напряжение на блок 11 задержки, которое через некоторое время задержки t il блока 5 усреднения открывает ключ 12. Ключ 12 открывается и импульсы, поступающие поочередно с выходов фазового дискриминатора 4 через элемент ИЛИ 7, открытый ключ 12 и элемент ИЛИ 6, поступают на дополнительный вход делителя 3 частоты. При этом в силу поочередного поступления сигналов с обоих выходов фазового дискриминатора 4 блок 5 усреднения не выдает управляющие сигналы на делитель 3 частоты, и последний управляется только сигналами, поступающими с выхода ключа 12. Ключ 12 остается открытым до появления управляющих сигналов с выхода блока 5 усреднения, что свидетельствует о выходе системы из состояния ложной синхронизации. Сигнал с выхода блока 5 усреднения через элемент ИЛИ 8 поступает на вход «запрет ключа 12 и на блок 11 задержки. Ранее накопленная информация в блоке 11 задержки о состоянии ложной синхронизации стирается, ключ 12 закрывается, а дальнейшая корректировка фазы, установка системы в состояние нормальной синхронизации и последующее удержание ее в этом состоянии осуществляется управляющими сигналами с выхода блока 5 усреднения. Использование предлагаемого устройства позволяет повысить достоверность приема коротких кодограмм (команд телеуправления). Устройство не требует дополнительной информации в каждом сеансе передачи коротких кодограмм или команд телеуправления, так как оно обеспечивает своевременное обнаружение и вывод системы из состояния ложного синхронизма независимо от закона чередования единиц и нулей в принимаемой информации. Формула изобретения Устройство синхронизации с дискретным управлением по авторскому свидетельству № 562935, отличающееся тем, целью повышения точности синхронизации, введены дешифратор и блок задержки, причем дополнительный выход делителя частоты подключен к входу дешифратора, включенного между выходом делителя частоты и управляющим входом дискриминатора ложной

5

синхронизации, выход которого через блок задержки подключен к другому входу ключа, вход которого соединен с другим входом блока задержки.

758547

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 562935, кл. Н 04 L 7/02, 1974 (прототип)

Авторы

Даты

1980-08-23—Публикация

1978-04-05—Подача