(54) УСТРОЙС1 ВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ ДЛЯ БЛОЧНЫХ КОДОВ

/iv jJiijMeinu Ht-.J включенного между выходом ivHcpUTOpa тактовых импульсов и входом делителя частоты.

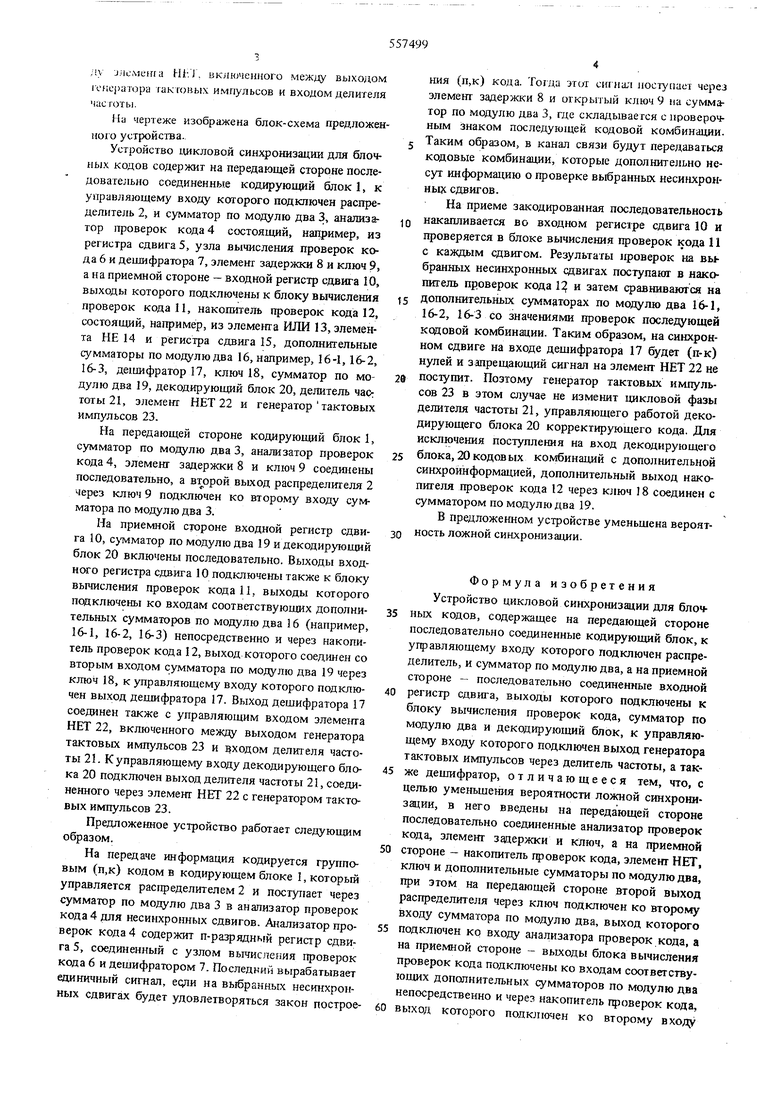

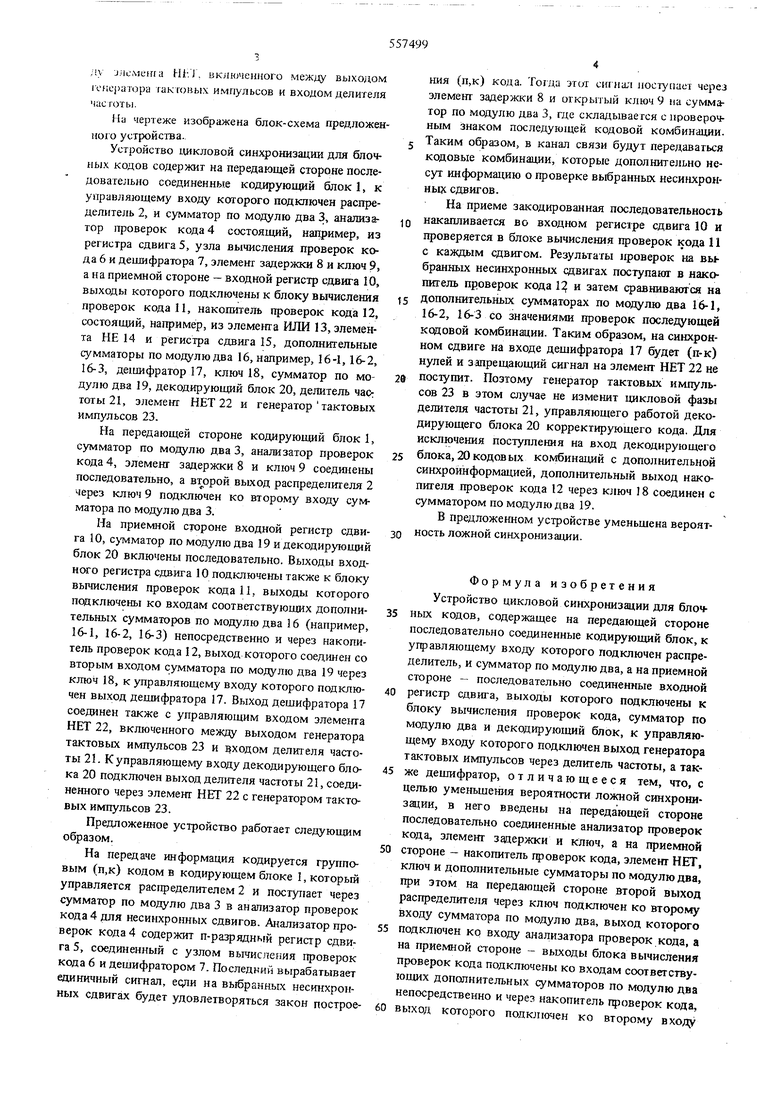

На чертеже изображена блок-схема предложенного устройстаа.

Устройство цикловой синхронизации для блочных кодов содержит на передающей стороне последовательно соединенные кодирующий блок 1, к управляющему входу которого подключен распределитель 2, и сумматор по модулю два 3, аналюэг тор проверок кода 4 состоящий, например, из регистра сдвига 5, узла вычисления проверок кода 6 и дешифратора 7, элемент задержки 8 и ключ 9, а на приемной стороне - входной регистр сдвига 10, выходы которого подключены к блоку вычисления проверок кода 11, накопитель проверок кода 12, состоящий, например, из элемета ИЛИ 13, элемента НЕ 14 и регистра сдвига 15, дополнительные сумматоры по модулю два 16, например, 16-1,16-2, 16-3, дешифратор 17, ключ 18, сумматор по модулю два 19, декодирующий блок 20, делитель чар: тоты 21, элемент НЕТ 22 и генератор тактовых импульсов 23.

На передающей стороне кодирующий блок 1, сумматор по модулю два 3, анализатор проверок кода 4, элемент задержки 8 и ключ 9 соединены последовательно, а второй выход распределителя 2 через ключ 9 подключен ко второму входу сумматора по модулю два 3.

На приемной стороне входной регистр сдвига 10, cjTviMaTOp по модулю два 19 и декодирующий блок 20 включены последовательно. Выходы входного регистра сдвига 10 подключены также к блоку вычисления проверок кода 11, выходы которого подключены ко входам соответствующих дополнительных сумматоров по модулю два 16 (например, 16-1, 16-2, 16-3) непосредственно и через накопитель проверок кода 12, выход которого соединен со вторым входом сумматора по модулю два 19 через ключ 18, к управляющему входу которого подключен выход дещифратора 17. Выход дещифратора 17 соединен также с управляющим входом элеме1гга НЕТ 22, включенного между выходом генератора тактовых импульсов 23 и уходом делителя частоты 21. К управляющему входу декодирующего блока 20 подключен выход делителя частоты 21, соединенного через элемент НЕТ 22 с генератором тактовых импульсов 23.

Предложенное устройство работает следующим образом.

На передаче информация кодируется групповым (п,к) кодом в кодирующем блоке 1, который управляется расгфеделителем 2 и поступает через сумматор по модулю два 3 в анализатор проверок кода 4 для несинхронных сдвигов. Анализатор проверок кода 4 содержит п-разрядньгй регистр сдвига 5, соединенный с узлом вычисления проверок кода 6 и дешифратором 7. Последний вырабатывает единкчньгй сигнал, ecfiK на выбранных несинхронных сдвигах будет удовлетворяться закон построения (п,к) кода. Тогда этся сигнал поступает через элемент задержки 8 и открытый ключ 9 на сумматор по модулю два 3, где складьшается с проверочным знаком последующей кодовой комбинации. Таким образом, в канал связи будут передаваться кодовые комбинации, которые дополнительно несут информацию о проверке выбранных несинхронных сдвигов.

На приеме закодированная последовательность

накапливается во входном регистре сдвига 10 и проверяется в блоке вычисления проверок кода 11 с каждым сдвигом. Результаты проверок на выбранных несинхронных сдвигах постулашг в накопитель проверок кода Ц и затем сравниваются на

дополнительных сумматорах по модулю два 16-1, 16-2, 16-3 со значениями проверок последующей кодовой комбинации. Таким образом, на синхронном сдвиге на входе дещифратора 17 будет (п-к) нулей и здарещающий сигнал на элемент НЕТ 22 не

поступит. Поэтому генератор тактовых импульсов 23 в этом случае не изменит цикловой фазы делителя частоты 21, управляющего работой декодирующего блока 20 корректирующего кода. Для исключения поступления на вход декодирующего

блока, 20кодовых комбинаций с дополнительной синхройнформацией, дополнительный выход накопителя проверок кода 12 через ключ 18 соединен с сумматором по модулю два 19.

В предложенном устройстве уменьщена вероятность ложной синхронизации.

Формула изобретения

Устройство цикловой синхронизации для бпочных кодов, содержащее на передающей стороне последовательно соединенные кодирующий блок, к управляющему входу которого подключен распределитель, и сумматор по модулю два, а на приемной стороне - последовательно соединенные входной

регистр сдвига, выходы которого подключены к блоку вычисления проверок кода, сумматор по модулю два и декодирующий блок, к управляющему входу которого подключен выход генератора тактовых импульсов через делитель частоты, а также депотфратор, отличающееся тем, что, с целью уменьщения вероятности ложной синхронизации, в него введены на передающей стороне последовательно соединенные анализатор проверок кода, элемент задержки и ключ, а на приемной

стороне - накопитель гфоверок кода, элемент НЕТ, ключ и дополнительные сумматоры по модулю два, при этом на передающей стороне второй выход распределителя через ключ подключен ко второму входу сумматора по модулю два, выход которого

подклгочен ко входу анализатора проверок кода, а на приемной стороне - выходы блока вычисления проверок кода подключены ко входам соответствующих дополнительных сумматоров по модулю два непосредственно и через накопитель проверок кода,

выход которого подключен ко второму входу сумматора no модулю два через ключ, к управляютему входу которого подключен выход дешифратора, который подключен к управляющему входу jjieMcina НЬТ, включенного между выходом генератора гакговых ишгульсов и входом делителя частоты. Источники информации, принятые во впима.чие при экспертизе: 1. Блейхман В. С. С1шхронизирую1цие свойства смежных классов циклических кодов, Вопросы радиоэлектроники, серия XI, Техника проводной связи, вып. 7, стр. 47-52, 1966.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цикловой синхронизации для блочных кодов | 1975 |

|

SU565403A1 |

| Устройство цикловой синхронизации для групповых кодов | 1975 |

|

SU557502A1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Устройство блочной синхронизации для групповых кодов | 1980 |

|

SU932643A1 |

| Устройство цикловой синхронизации | 1981 |

|

SU949832A1 |

| Устройство для цикловой синхронизации корректирующих кодов | 1978 |

|

SU788413A2 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1987 |

|

SU1462492A1 |

| Пороговый декодер сверточного кода | 1989 |

|

SU1667264A1 |

| Устройство для приема телесигналов | 1981 |

|

SU1003127A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

1

Авторы

Даты

1977-05-05—Публикация

1975-03-31—Подача