1

Изобретение относится к области вычислительной техники и может быть использовано при проектировании арифметических устройств ЭВМ.

В большинстве современных ЭВЛ1 выполняются арифметические операции над числами с плавающей запятой.

Известны арифметические устройства, в которых для повышения точности при обработке чисел с плаваюш,ей запятой, выталкиваемой при выравнивании меньшего операнда, разряд запоминается на специальном дополнительном триггере и после суммирования (вычитания) мантисс на вход переноса младшего разряда подается та цифра, которая сохранится в этом дополнительном триггере 1.

В других арифметических устройствах операция сложения (вычитания) мантисс производится на сумматоре, количество разрядов которого на единицу больше, чем количество разрядов результата. Процесс округления заключается в прибавлении единицы к предварительному результату с последующим исключением этого дополнительного разряда из результата 2.

Прототипом изобретения является сумматор, содержащий регистры порядков и мантисс первого и второго слагаемого, сумматоры порядков и мантисс, причем выходы регистров мантисс подключены ко входам сумматора мантисс, выходы регистров порядков подключены ко входам сумматора порядков, а выходы сумматора мантисс подключены ко входам регистра мантиссы второго слагаемого, выходы сумматора порядков подключены ко входам регистра порядка второго слагаемого 3.

Недостаток известных устройств заключается в том, что регистры и сумматор мантисс расширены на величину дополнительной цифры.

Целью изобретения является устранение этого недостатка, т. е. уменьшение количества оборудования.

15

Для достин ения этой цели в устройство введен регистр предварительного порядка, ко входам которого подключены выходы регистров порядков, а выходы его соединены со входами регистра порядка второго слагаемого, выходы старших разрядов регистров мантисс первого и второго слагаемого и сумматора мантисс соединены соответственно со входами младших разрядов регистров порядков первого и второго слагаемого и сумматора порядков, а выходы младших разрядов регистров порядков первого и второго слагаемого соединены соответственно со входами старших разрядов регистров мантисс первого и второго слагаемого.

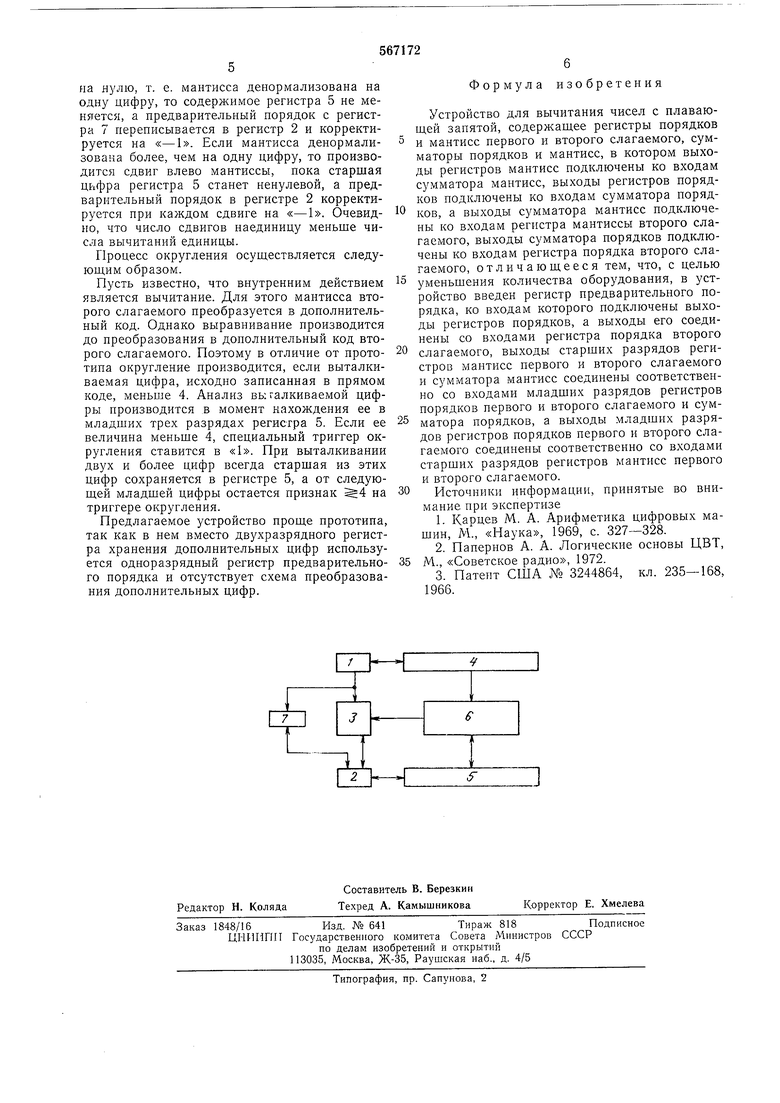

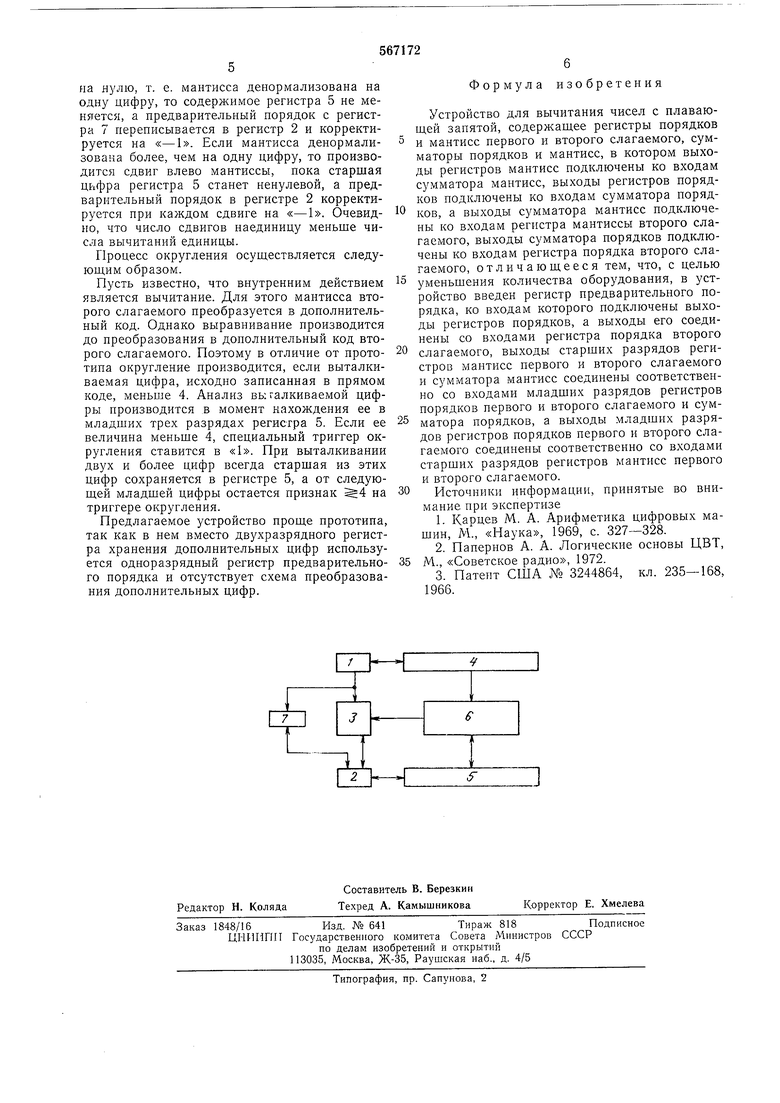

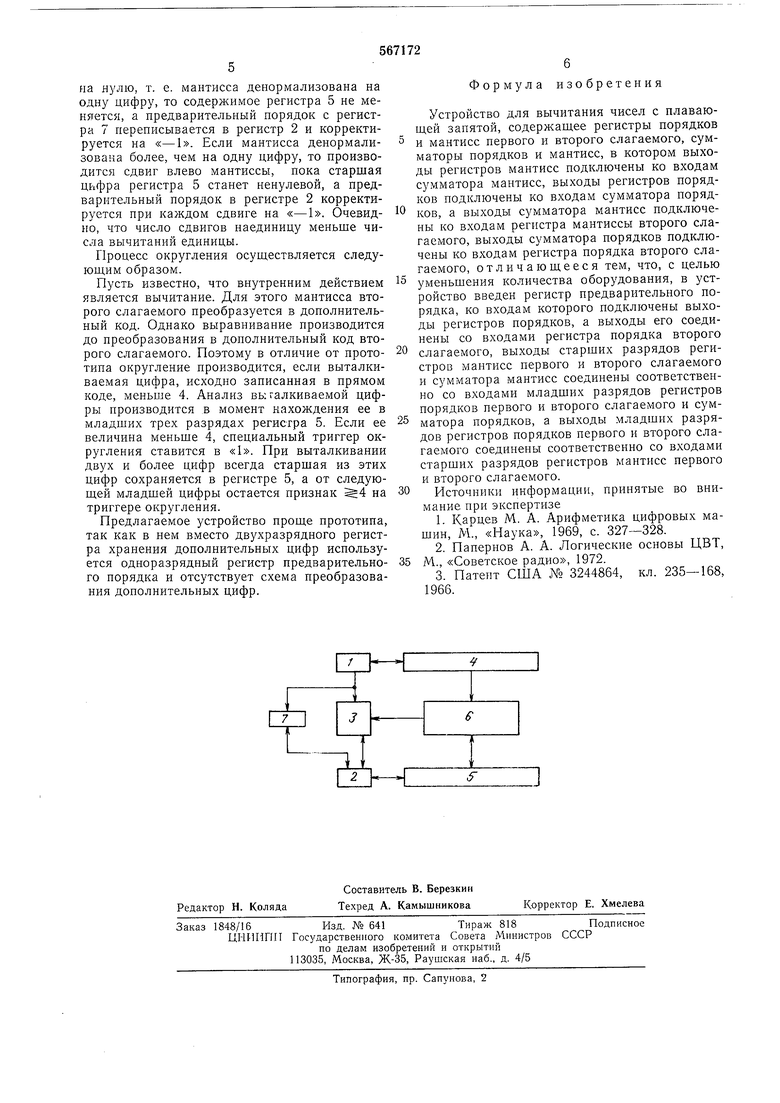

Блок-схема устройства изображена на чертеже.

Она содержит регистр 1 порядка первого слагаемого, регистр 2 порядка второго слагаемого, сумматор 3 порядков, регистр 4 мантиссы первого слагаемого, регистр 5 мантиссы второго слагаемого, сумматор 6 мантисс, регистр 7 предварительного порядка.

Выходы регистров порядков 1 и 2 соединены со входами сумматора 3 порядков и с регистром 7 предварительного порядка, выходы которых соединены с регистром 2 порядка второго слагаемого. Выходы регистров мантисс 4 и 5 соединены со входами сумматора 6 мантисс, выход которого соединен со входом регистра 5 мантиссы второго слагаемого. Выходы старшего разряда каждого из регистров мантисс 4 и 5 соединены соответственно с входами .младших разрядов регистров порядков

1и 2, а выходы младших разрядов регистров порядков 1 и 2 соединены соответственно с входами старших разрядов регистров мантисс 4 и 5. Выход старшего разряда сумматора 6 мантисс соединен с младшим разрядом сумматора 3 порядков.

Регистр 7 предварительного порядка - трехразрядный регистр, предназначенный для временного хранения предварительного порядка (это может быть, например, регистр памяти).

Устройство работает следуюш,им образом.

Вначале определяется разность порядков. Для этого дополнение порядка второго слагаемого записывается в регистр 2 и суммируется на сумматоре 3 порядков с порядком первого слагаемого, т. е. определяется разность порядков.

По знаку разности, определяемому наличием или отсутствием переноса из старшего разряда сумматора порядков 3, определяется больший порядок.

При равенстве порядков (П1 П2) дешифратор нуля сумматора 3 порядков формирует управляющий сигнал для суммирования мантисс. Если , то производится нормализация первого слагаемого; мантисса сдвигается влево на регистре 4 до тех пор, пока либо П не станет равным Пг, либо старшая цифра в регистре 4 станет ненулевой. При каждом сдвиге содержимое регистра 1 уменьшается на -1 и полученное значение суммируется с содержимым регистра 2, т. е. определяется П}-Пз. Этот процесс длится до тех пор, пока П не станет равным Ylz.

Если в результате нормализации П равен Пг, то производится суммирование мантисс. Если после нормализации порядки не сравнились, т. е. , то второе слагаемое масштабируется: мантисса сдвигается вправо, а порядок корректируется иа величину сдвинутых цифр. Так как в регистре 2 записано дополнение Пг, то при сдвиге вправо мантиссы второго слагаемого из содержимого регистра

2вычитается «1. После каждого вычитания производится сравнение порядков, содержимое регистра 1 суммируется с содержимым регистра 2. Сдвиг мантиссы вправо производится до тех пор, пока либо 111 не станет равным П2, либо мантисса не станет равной нулю.

Рассмотрим сдвиг вправо мантиссы второго слагаемого. После нормализации мантиссы первого слагаемого при первый сдвиг вправо мантиссы второго слагаемого не производится, но порядок в регистре 2 корректируется на «-1. Пусть после этой коррекции П: равен Па. Тогда следуюш,им шагом будет суммирование мантисс. Однако, та как сдвиг мантиссы второго слагаемого не производился, то в одноименных разрядах регистров 4 и 5 будут находиться цифры мантисс с разными весами, а именно: в регистре 4 вес каждой цифры на единицу больше, чем вес соответствуюш,ей цифры в регистре 5. Для совмеш,ения цифр мантисс первого и второго слагаемых содержимое регистра 4 сдвигается влево на одну цифру. При этом предварительный порядок с регистра 1 переписывается в регистр 7 предварительного порядка, а в регистр 1 переписывается сдвигаемая влево старшая цифра регистра 4. В регистр 2 записываются нули, так как старшая цифра мантиссы второго слагаемого в рассматриваемом случае должна равняться нулю. Обнуление

регистра 2 осуществляется записью содержимого сумматора 3 порядков при П1 П2, т. е. когда 0.

В результате произведенных действий каждый из регистров 4 и 5 расширился на одну

цифру за счет регистров 1 и 2 порядков, а сумматор 6 мантисс расширился за счет сумматора 3 порядков. При этом младшая цифра не выталкивалась из регистра 5, а сохранилась в его младших разрядах.

Дальнейшее суммирование мантисс производится на сумматорах порядков и мантисс одновременно: на сумматоре 3 порядков обрабатываются старшие (14-е) цифры мантисс, а на сумматоре 6 мантисс остальные 13 цифр,

включая одну дополнительную цифру. Если имеется перенос из старшего разряда цепи переноса сумматора 6, то он добавляется к суммируемым на сумматоре 3 старшим цифрам. При вычитании формируется дополнительный код от 14 цифр второго слагаемого, старшая цифра в регистре 2, исходно равная нулю, принимает инверсное значение «III (7). После суммирования старшая цифра записывается в регистр 2, а остальные цифры -

в регистр 5. Если старшая цифра мантиссы результата не равна нулю (сигнал с сумматора порядков аналогичный П1 П2), т. е. мантисса нормализована, то производится сдвиг ее вправо. При этом старшая цифра с

регистра 2 переписывается в старшую цифру регистра 5, а в регистр 2 с регистра 7 записывается предварительный порядок; младшая цифра регистра 5 выталкивается. Если старшая цифра в регистре 2 равна

нулю, а старшая цифра, в регистре 5 не ранна нулю, т. е. мантисса денормализована на одну цифру, то содержимое регистра 5 не меняется, а нредварительный порядок с регистра 7 нереписывается в регистр 2 и корректируется на «-1. Если мантисса денормализована более, чем на одну цифру, то производится сдвиг влево мантиссы, пока старшая цьфра регистра 5 станет ненулевой, а предварительный порядок в регистре 2 корректируется при каждом сдвиге на «-1. Очевидно, что число сдвигов наединицу меньше числа вычитаний единицы.

Процесс округления осушествляется следующим образом.

Пусть известно, что внутренним действием является вычитание. Для этого мантисса второго слагаемого преобразуется в дополнительный код. Однако выравнивание производится до преобразования в дополнительный код второго слагаемого. Поэтому в отличие от прототипа округление производится, если выталкиваемая цифра, исходно записанная в прямом коде, меньше 4. Анализ вы галкиваемой цифры производится в момент нахождения ее в младших трех разрядах регистра 5. Если ее величина меньше 4, специальный триггер округления ставится в «1. При выталкивании двух и более цифр всегда старшая из этих цифр сохраняется в регистре 5, а от следуюш,ей младшей цифры остается признак 4 на триггере округления.

Предлагаемое устройство прош,е прототипа, так как в нем вместо двухразрядного регистра хранения дополнительных цифр используется одноразрядный регистр предварительного порядка и отсутствует схема преобразования дополнительных цифр.

6 Формула изобретения

Устройство для вычитания чисел с плавающей запятой, содержащее регистры порядков и мантисс первого и второго слагаемого, сумматоры порядков и мантисс, в котором выходы регистров мантисс подключены ко входам сумматора мантисс, выходы регистров порядков подключены ко входам сумматора порядков, а выходы сумматора мантисс подключены ко входам регистра мантиссы второго слагаемого, выходы сумматора порядков подключены ко входам регистра порядка второго слагаемого, отличающееся тем, что, с целью уменьшения количества оборудования, в устройство введен регистр предварительного порядка, ко входам которого подключены выходы регистров порядков, а выходы его соединены со входами регистра порядка второго слагаемого, выходы старших разрядов регистров мантисс первого и второго слагаемого и сумматора мантисс соединены соответственно со входами младших разрядов регистров порядков первого и второго слагаемого и сумматора порядков, а выходы младших разрядов регистров порядков первого и второго слагаемого соединены соответственно со входами старших разрядов регистров мантисс первого и второго слагаемого.

Источники информации, принятые во внимание при экспертизе

1.Карцев М. А. Арифметика цифровых машин, М., «Наука, 1969, с. 327-328.

2.Папернов А. А. Логические основы ЦВТ, М., «Советское радио, 1972.

3.Патент США № 3244864, кл. 235-168, 1966.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

| Арифметическое устройство | 1978 |

|

SU809169A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Арифметическое устройство | 1971 |

|

SU522497A1 |

| Устройство для умножения | 1984 |

|

SU1226447A1 |

Авторы

Даты

1977-07-30—Публикация

1975-09-30—Подача