Изобретение отоосится к радиотехнике, может использоваться в системах связи с многократным псжторением сообщений. .

Известен способ исправления ошвбсж в системах связи, состоящий в замене иска|женных комбинаций комбинациями, принятыми без ошибок, причем в случае подачи ; сигнала запрос на приемной стороне анализируются N кодовых комбинаций, и запра шиваемая кодовая комбинация принимается только в том случае, когда все N комбя- наций приняты без ошибок. В случае обнаружения ошибок хотя бы в одной из комбинаций все эти комбинации стираются

. Однако при известном спею обе необходима передача сигнала запрос на повтс ение сообщения.

Наиболее близок к предлагаемому способ исправления ошибок в системах связи с многократным повторением сообщений, состоя- ших из кодовых комбинаций обнаруживающего кода, заключающийся в приеме кодовых комбинаций, анализе и обнаружении в первом никло |1Ородачи схиибок в каждой кодовой комбиио1Г,1И- В последующих циклах передачи анализируют только те кодовые комбинации, в которых ошибки обнаружены во всех предыдущих циклах передачи, и запоминают кодовые комбинации, принятые без ошибок 2.

Однако и при атом способе продолжитель ность обработхв сигвалов, необходимая для приема всех- кодовых комбинаций сообщения, весьма велика.

Цель нзобретення - ускорение обработтш сигналов при нсправленни ошибок в системах связи.

Предлагаек4ый спос исправления ошибок в системах связи с многократным повторением сообщений, состоящих из кодовых комбинаций обнаруживающего кода, заключающийся в приеме кодовых комбинаций, анализе и обнаружении; в первом цикле передачи ошибсж в каждой кодовой комбинации, анализе в последующих циклах передачи только тех кодовых комбинаций, а которых ошибки обнаружены во всех предыдущих циклах передачи, в запоминании кодс«ых комбинаций, принятых без ошибок, отличает :я тем, что дополнит льно запоминают кодови« кок(бинаиии

с ошибками on заданное число циклов передачи, для каждой из которых поэлемег)гно исправляют ошибки по критерию бояьшинст Bfl, выделяют исправленные кодовые комби- нлнии и запоминяюг их, а кодовые комбина- НИИ, в которых обнаружены опшбки, после исправления стирают.

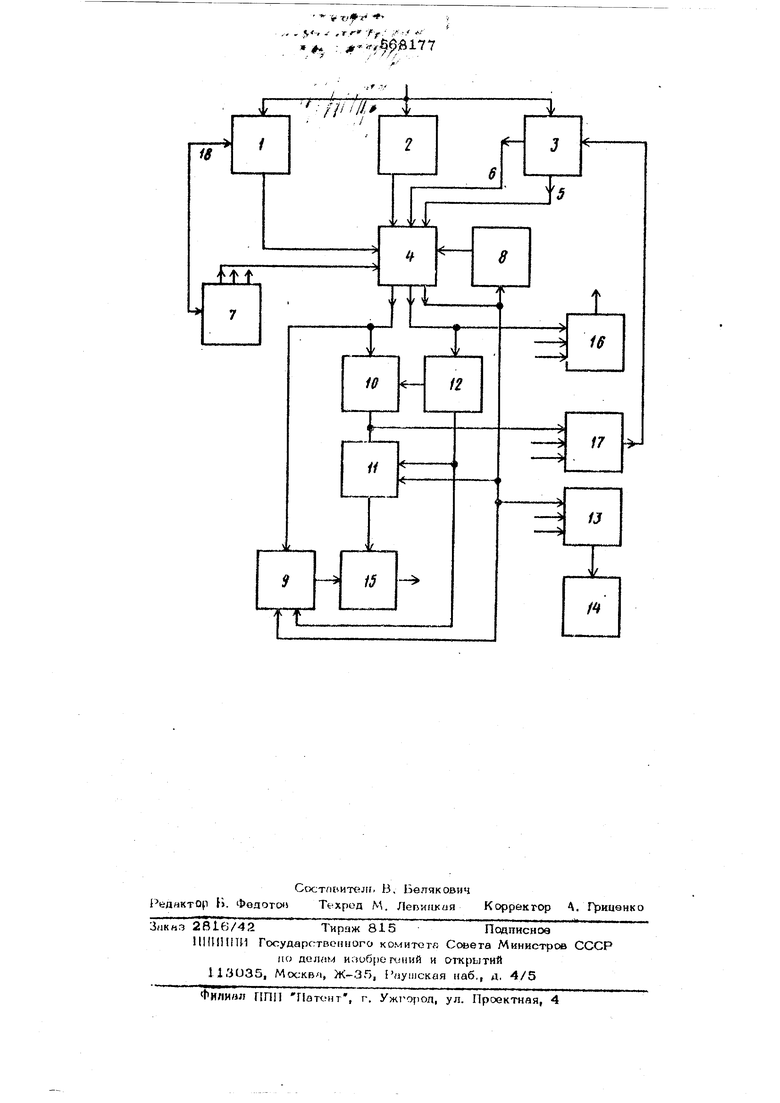

На чертеже представлена структурная электрическая схема для -реализации способа исправления О1либок в системах связи число кодовых комбинаций в сообщении равно четырем, а заданное число циклов, после которого исправляются ошибки, равно трем).

Устройство содержит блок 1, выявляющий признак ачало сообщения , блсж памя ти 2 емкостью на одну ксаовую комбинадию, блок обнаружения ошибок 3, входы которых являются входом устройства, блок сгробирования 4, информационные входы которого подсоединены к выходу блока памяти 2 и вы ходам 5 и 6 блока обнаружения сшибок 3, а стробирующие - к выходу блока 1, к соотвогс1вую1лему выходу приемного распредалителя 7 на четыре кодовые комбинации и выходу блокировки 8j ключ 9, один из управпяюших и информационный входы когорог-о подсоединены д соответствую шим выходам блока сгробнрования А, блок 10 cl llfыl(iutlл ошибок в кодовых алиментах., и Iфop alUlO)iHый вход которогоподсреци 11,-и к соочветствуюшему выходу блока стробирС)ания 4, а выход -- к инфо} мационнму входу ключа 11, счегчик 12 на три, аход. подсоединен к соответствующему выходу блока стробирования 4, а вы-« ход - к управляющим входам блока 10 и ключей 9 и 11, элемент ИЛИ 13 на фи входа, каждый иэ которых соединен с соот ве-п;:гвуЮ1иим выходом блока стробирования 4, ij Быход - со счетчиком 14 числа приня-t гых комбииаиий, элемент ИЛИ 15, входы которого соединены с выходами ключей О и 11, а выход является выходом устройства, блок 16 формирования сигнала запрос каждый из трех входов которого соединен с соответствующим выходом блока стробирования 4, а выход - со входом обратного капала, элемент ИЛИ 17, каждый из трех входг) которого соединен с выходом блока 10, а выход - с соогветствуюшим

э-ходом блока обнаружения ошибок 3. Вход 18 блокп 1 соединен с выходом приемного распрсдслит :ля 7.

Усг1)Ойство работает следующим образом Закопиров-аннсх сообишиие, состоящее из чст1лрох кодовых комбинаций, поступает на пходь блока 1, блока памяти 2 и блока обнаружения ошибок 3, В момент окончания )Иома кодовой комбинации, в которо) содоржится признак начало сообтения, на другой вход блсякл 1 поступает сигнал с приемного распределителя 7, и при отсутствии ошибок в код1«ой комбинации на его выходе появляется сигнал, означающий начало приема сообшения.

Вторая кодовая комбинация запксываеся в блок памяти 2 и проверяется в блсже обнаружения ошибок 3 на отсутствие оигибок. Если ошибки неТ| в момент окончания ее приема разрешающий сигнал с выхода 5 поступает через блок стробирования 4 на управдяюшив входы ключей 9 и 11, а информация с блока памяти 2 через блок стробирования 4 поступает на информационный вход ключа 9. На другие управпяюише входы ключей 9 и 11 поступает сигнал со счетчика 12, который разрешае прохождение информации через ключ 9 я элемент ИЛИ 15 на выход устройства и одншременно запрещает прохождение информации из блока 10 через ключ 11. Кроме «входов ключей 9 и 11 сигнал с выхода 5 через блсж стробирсжания 4 по дается на триггер 8 блокировки и через элемент ИЛИ 13 - на счетчик 14. Счетчик фиксирует факт приема одной кодовой комбинации, а на выходе триггера 8 появляется сигнал, запрещающий дальнейшее прохождение информации из блока памяти и сигналов из блока обнаружения ошибок 3 через блок стробирования 4 на ключи 9 и 11, блок 10, счетчик 11, элемент ИЛИ 13 и блок 16.

В случае обнаружения ошибки в блоке обнаружения ошибок 3 на выходе 6 вырабатывается сигнал запрос, который, пройдя через блок ст}юбирования 4,-фиксируется счетчиком 12 и через блок 16 поступает на вход обратного канала. Од повременно с.этим информация из блока памяти 2 поступает че|)ез блок стробирования 4 в блок 1О исправления ошибок и запоминается в нем.

Принятая повторно (во втором цикле передачи) вторая кодовая комбинация проверяется так же, как и в первом цикле. При этом, в случае обнаружения в ней оигибок, она пшторно запоминается блоком Ю.

При обнаружении ошибки во второй кодовой комбинации во всех трех циклах подряд в блоке 10 по сигналу счетчик 12 поэлементно исправляются О1либки в искаженной информации кратности ( ) вкяюмительно. Исправленная кодонвя KOKIбинапия поступает черва элемент ИЛИ 17 в блок обнвружения ошибки 3 для проверки Если ошибки в ней нет, на выходе 5 появляется сигнал разрешения, который чороа блок стробирования 4 поступает на один и управляющих входов клшчей 9 и 11. Сигнал со счетчика 12, поступающий на другие управляющие входы ключей 9,11, разрешает прохождение информации из блока 10 через ключ 11 на элемент ИЛИ 15 и далее на выход, одновременно запрещая прохождение искаженной информации из блока памяти 2 через ключ 9. В случае обнаружения ошибки в исправленной кодовой комбинадии информация, хранящаяся в блоке 1О, по сжончании. третьего цикла стирается, и в следующем шикле передачи вторая кодовая комбинация проверяется так же, как и R пераом цикле. . Блоки, принимающие две другие кодовые комбинации, не {изображенные, на чертеже. содержат каждый: блок стробирования 4, триггер 8, ключи 9 и 11, бл(ж 10, счетчик .12, элемент ИЛИ 15 и работают аналогично. После приема всех четырех кодовых комбинаций на выходе счетчика 14. числа принятых кодовых комбинаций появляется сигнал, который обнуляет все схемы устройства и возвращает триггеры 8 в исходное состояние. Все схемы обнуляются блоком 16 в гех случаях, когда исчерпывает ся максимально допустимое число цикле п& редачи данного сообщения. Блок 16 формирования сигнала запрос рабогает так, что за время приема одного цикла сигнал запрос вырабатывается только один раз, независимо от того, один или несколько сигналов поступает на ее вход за &ТОТ цикл. Совместное выполнение операций по исправлению ошибок в кодовых комбинациях и кодовых элементах с последующей проверкой исправленных кодовых комбинаций позвсь ляет уменьшить затрачиваемое на исправле- НИИ ошибок BfieKiH болпо, (м на но орлгш нию с известным способом /I|.IH иснольаопжпп избыточного кода П (К ) 12 (24) и p/iботе по { аналу с вероятно ;;гьи:) ошибки я ном Р 21О без снижения досто1зерности iifiHuwтой информации; Формула изобретения Способ исправления ошибок в системах связи с многократным повторением сообщений, состоящих из кодовых комбинаций обнаруживало„его кода, заключающийся в приеме кодовых комбинаций, анализе я обнаруженви в первом передачи ошибок в каждой кодовой комбинации, анализе в последующих циклах пере- |Дачи только тех кодовых комбинаций, в которых ошибки обнаружены во всех предыдущих иклах передачи, и запок«ийания кодовых комбинаций, п|эинятых без ошибок, отличающийся тем, что, с целью ускорения обработки сигналов, дсшолнительно запоминают кодовые ксмбинации, принятые с ошибками, выявлях т одноименные кодовые комбинации с ошибками за заданное число циклов пе{юдачи, для каждой из которых поэлементно исправляют ошибки по критерию большинства, выделяют исправленные кодовые комбинации и запоминают их, а кодовые комбинации, в которых обнаружены ошибки поо ле исправления,стирают. Источники информации, принятые во внимание при экспертизе: 1.Авторское свидетельство N 187395, аОб F 11/08, 1966. 2.Патент США № 3428944, «л. 34O-14ai . 1969,

T. ,, , «,.-. . ,rr -ff/ , tf

, :..ei77

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления ошибок | 1974 |

|

SU544151A1 |

| Устройство для приема дискретной информации,закодированной корректирующим кодом | 1983 |

|

SU1099397A2 |

| Анализатор кодовых комбинаций для устройств передачи информации с решающей обратной связью | 1978 |

|

SU781872A2 |

| Устройство для приема избыточной информации | 1981 |

|

SU1001147A1 |

| Устройство для приема дискретной информации,закодированной корректирующим кодом | 1984 |

|

SU1172022A2 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1596464A1 |

| Устройство для исправления ошибок в кодовой комбинации | 1974 |

|

SU526898A1 |

| Устройство декодирования с исправлением ошибок | 1985 |

|

SU1293855A1 |

| Система передачи данных по каналам с обратной связью | 1980 |

|

SU966923A1 |

| Устройство анализа кодовых комбинаций | 1976 |

|

SU649152A1 |

Авторы

Даты

1977-08-05—Публикация

1974-08-23—Подача