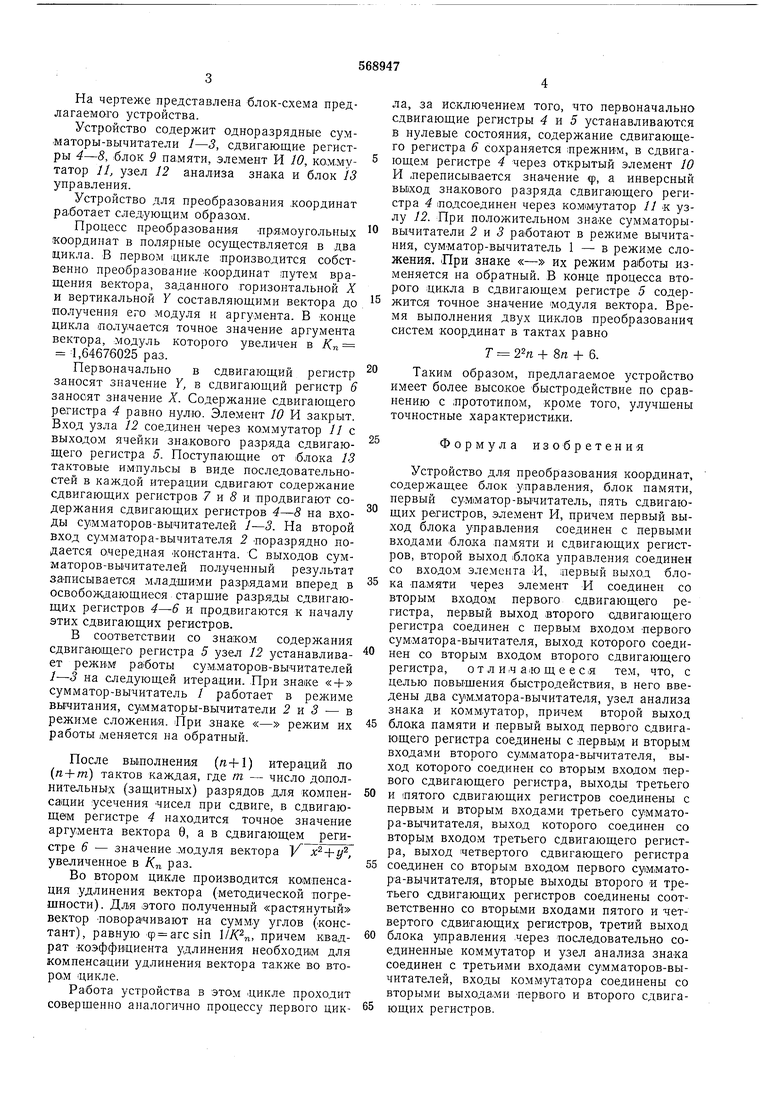

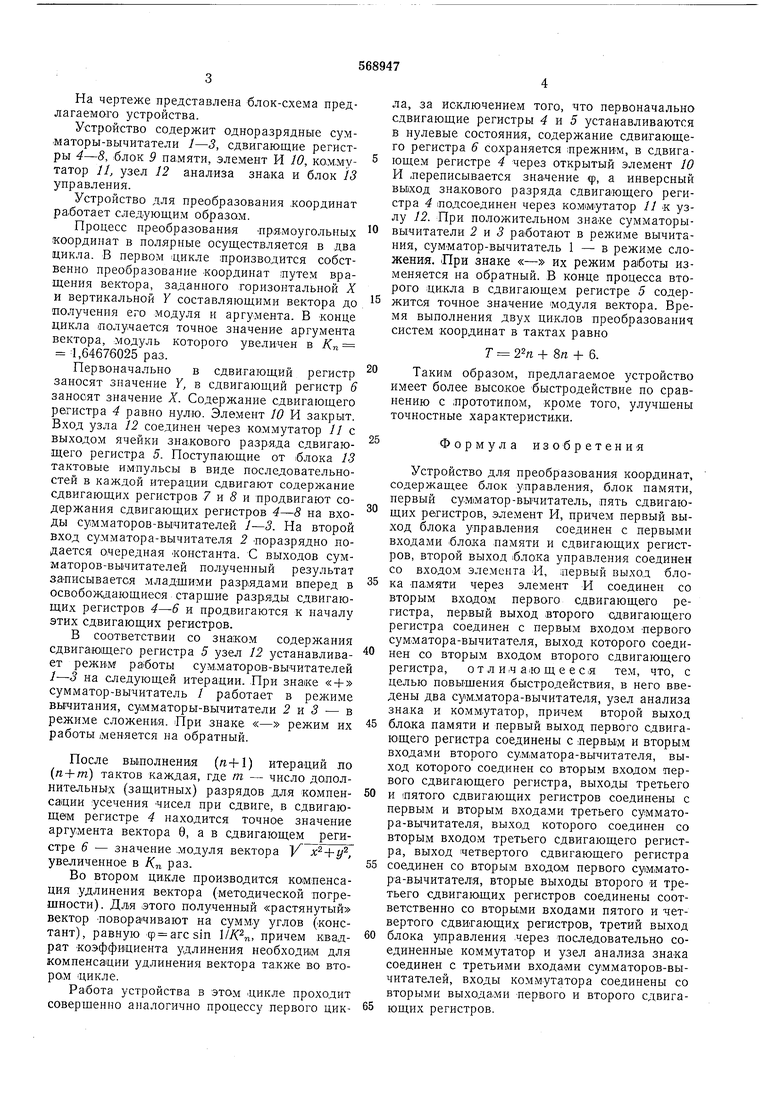

На чертеже представлена блок-схема предлагаемого устройства.

Устройство содержит одноразрядные сумматоры-вычитатели 1-3, сдвигающие регистры 4-8, блок 9 памяти, элемент И 10, кО:М,мутатор 11, узел 12 анализа знака и блок 13 управления.

Устройство для преобразования .координат работает следующим образом.

Процесс преобразования прямоугольных координат в полярные осуществляется в два цикла. В перво.Л1 щикле производится собственно преобразование -координат лутем вращения вектора, заданного горизонтальной X и вертикальной Y составляющими вектора до получения его модуля и аргумента. В конце цикла получается точное значение аргумента вектора, :Модуль которого увеличен в /Си 1,64676025 раз.

Первоначально в сдвигающий регистр заносят значение У, в сдвигающий регистр 6 заносят значение X. Содержание сдвигающего регистра 4 равно нулю. Элемент 10 И закрыт. Вход узла 12 соединен через К0;ммутатор 11 с выходом ячейки знакового разряда сдвигающего регистра 5. Поступающие от блока 13 тактовые импульсы в виде последовательностей в каждой итерации сдвигают содержание сдвигающих регистров 7 и 5 и продвигают содержания сдвигающих регистров 4-8 на входы су;.мматоров-вы1читателей /-3. На второй вход сумматора-вычитателя 2 -поразрядно подается очередная -константа. С выходов сумматоров-вычитателей полученный результат записывается млад-щими разрядами вперед в освобождающиеся старщие разряды сдвигающих регистров 4-6 и продвигаются к началу этих сдвигающих регистров.

В соответствии со знаком содержания сдвигающего регистра 5 узел 12 устанавливает режим сум,маторов-вы-читателей /-3 на следующей итерации. .При знаке «-f сумматор-вычитатель / работает в режиме вьгчитания, сумматоры-вычитатели 2 и 5 - в режиме сложения. При знаке «- режим их работы меняется на обратный.

После выполнения («+) итера-ций ло (п + т) тактов каждая, где т - число дополнительных (защитных) разрядов .дл-я компенсации усечения -чисел при сдвиге, в сдвигающем регистре 4 находится точное значение аргумента вектора Э, а в сдвигающем регистре 6 - значение .мо.дуля вектора 1/ , увеличенное в Кп раз.

Во втором цикле производится ко мпенсация .удлинения вектора (методической погрешности). Для этого полученный «растянутый вектор -поворачивают на сумму углов (-констант), равную ф arc sin , причем квадрат -коэффициента удлинения необходи1М для компенсации удлинения вектора та.кже во втором -цикле.

Работа устройства в этом днкле прохо.дит соверщенно аналогично процессу первого цикла, за исключением того, что первоначально сдвигаю.щие регистры и 5 устанавливаются в нулевые состояния, содержание сдвигающего регистра 6 сохраняется прежним, в сдвигающем регистре 4 через открытый элемент 10 И .переписывается значение ф, а инверсный выход знакового разряда сдвигающего регистра 4 1подсое.дннен через коммутатор 11 к узлу J2. При положительном знаке сумматорывычитатели 2 и 3 работают в режиме вычитания, сум-матор-вычитатель 1 - в режиме сложения. При знаке «- их режим работы изменяется на обратный. .В конце процесса второго цккла в сдвигающем регистре 5 со.держится точное значение модуля вектора. Время выполнения двух циклов преобразования систем координат в тактах равно

Т 2Ч+ 8п + 6.

Таким образо.м, предлагаемое устройство имеет более высо.кое быстродействие по сравнению с лрототипом, кроме того, улучщены точностные характеристики.

Формула изобретения

Устройство для преобразования координат, содержащее блок управления, блок памяти, первый сумматор-вычитатель, пять сдвигающих регистров, элемент И, причем первый выход блока управления соединен с первыми входами блока памяти и сдвигающих регистров, второй выход блока управления соединен со входом элемента И, первый выход блока -памяти через элемент И соединен со вторым ВХОДО.М первого сдвигающего регистра, первый выход второго сдвигающего регистра соединен с первым входом -первого сумматора-вычитателя, выход которого соединен со вторым входом второго сдвигающего регистра, отли-ча-ющееся тем, что, с целью повы-шения быстродействия, в него введены два сум.матора-вычитателя, узел анализа знака и комм-утатор, причем второй выход

блока памяти и первый выхо.д первого сдвигающего регистра соединены с лервым и вторым входами второго сумматора-вычитателя, выход которого соединен со вторым входом первого сдвигающего регистра, выходы третьего

и пятого сдвигающих регистров соединены с первым и вторым входа.ми третьего сумматора-вычитателя, выход которого соединен со вторым входом третьего сдвигающего регистра, выход четвертого сдвигающего регистра

соединен со вторым входом первого сумматоРа-вычитателя, вторые выходы второго -и третьего сдвигающих регистров соединены соответственно со вторыми входами пятого и четвертого сдви гающих регистров, третий выход

блока управления через последовательно соединенные коммутатор и узел анализа зна-ка соединен с третьими входами сумматоров-вычитателей, входы коммутатора соединены со вторыми выходами первого и второго сдвигающих регистров.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР

№ 478306, кл. G Об F 15/20, 1973.

2. Авторокоесвидетельство

СССР

№ 4511996, кл. G 06 F 16/20, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования координат | 1977 |

|

SU660055A2 |

| Устройство для вычисления обратного гиперболического тангенса | 1973 |

|

SU465630A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МОДУЛЯ ТРЕХМЕРНОГО ВЕКТОРА | 1993 |

|

RU2040039C1 |

| Устройство для вычисления гиперболического тангенса | 1973 |

|

SU526890A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ КООРДИНАТ | 1991 |

|

RU2007749C1 |

| Устройство для вычисления тангенса | 1975 |

|

SU650073A1 |

| Устройство для вычисления элементарных функций | 1975 |

|

SU553612A1 |

| Устройство для вычисления тригонометрического тангенса | 1973 |

|

SU537344A1 |

| Устройство для преобразованияКООРдиНАТ | 1979 |

|

SU836636A1 |

| Устройство для вычисления логарифмической функции | 1973 |

|

SU541167A1 |

Авторы

Даты

1977-08-15—Публикация

1974-07-15—Подача