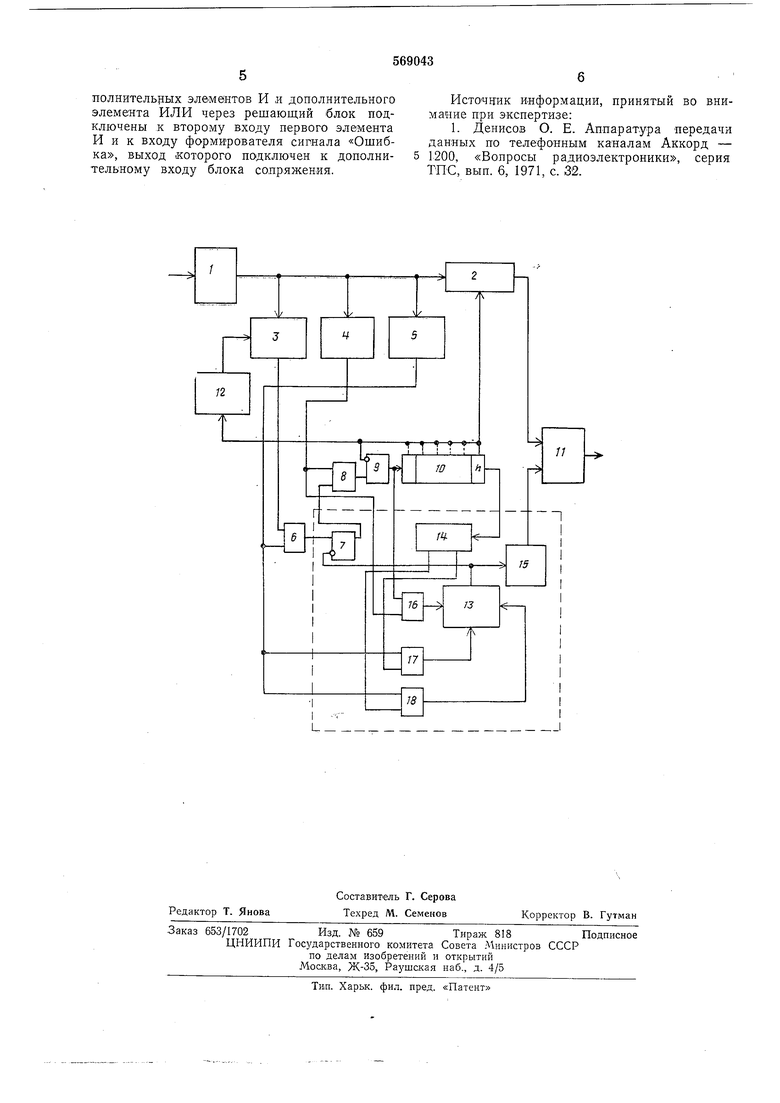

которого подключен к входам накопителя 2, блока 3 сравнения циклических номеров, декодера 4 и нриемника 5 сигнала «Фаза, причем выходы блока 3 и приемника 5 через последовательно соединенные первый элемент ИЛИ 6, первый элемент И 7, второй элемент ИЛИ 8, к второму входу которого подключен выход декодера 4 и второй элемент И 9, подключены к входу регистра блокировки 10, тактовый выход последнего подключен к второму входу второго элемента И 9 непосредственно, а ко входам блоков сЗ и // сопряжения соответственно через датчик 12 циклических номеров, накопитель 2, решающий блок 13, блок 14 задерж ки, формирователь 15 сигнала «О/шибка, два дололнительных элемента И /б и /7 и дополнительный элемент ИЛР /5, при этом выход декодера 4 л вход регистра 9 блокировки подключены к соответствующим входам первого дополнительного элемента И 16, выход регистра 9 блокировки через блок 14 задержки подключен к одному из входов вторОГО дополнительного элемента И 17 и дополнительного элемента ИЛИ 18, к другому входу которых подключен выход приемника 5, а выходы пер.зого и второго дополнительных эле.ментов И 16 v. 17 к дополнительного элемента ИЛИ 18 через решающий блок 13 подключены к второму входу первого элемента И 7 и к входу формирователя 15, а его выход подключен к дополнительному входу блока // сопряжения.

Устройство работает следующим образом.

При обнаружении оши-бки в принятой комбинации, несовпадении циклического номера принятой комбинации ожидаемому или приеме сигнала «Запрос сигналом с выхода датчика 12 циклических «омеров запускается регистр 10 блокировки, сигналами с его выходов стираются й+,1 комбинаций с выхода накопителя 2, в течение п+1 циклов запрещается работа датчика 12 циклических но.меро,в, а в течение п циклов - запись «Ь в регистр 10 блокировки при помощи вторс о элемента И .9. Сигналом с выхода декодера 4 одновременно с запуском регистра 10 блокировки через первый дополнительный элемент И 16 на вход решающего блока 13 записывается «1, которая в случае приема сигнала «Зацрос во время блокировки стирается сигналом с выхода приемника 5 через дополнительный элемент ИЛИ 18.

В случае приема сигнала «Запрос непосредственно после -блокировки, вследствие необваруженлого иска1жени1Я сигнала «Запрос на противоположной станции, сигналом с выхода регистра 10 блокировки запускается блок 14 задержки, с выходов которого выдается два сигнала: первый - в конце анализа комбинации, принимаемой непасред-ствеппо после б.токировки этим сигналом, в случае, если эта комбинация - сигнал «Запрос, через второй дополнительный элемент И 17 выдается тактовый сигнал, осуществляющий выдачу «1 с выхода рещающего блока 13,

второй - с задержкой по отношению к перво.му, не превышающей длительности одного символа, этим сигналом через дополнительный элемент ИЛИ 18 осуществляется стира.ние «I в решающем блоке 13.

Сигналом с выхода решающего блока 13 осзществляется запрет запуска регистра 10 блокировки при помощи первого элемента И 7 и залуск формирователя 15 сигнала «Ошибка, последний выдается па выход устройства через блок // солрлжения.

Предлагаемое устройство позволяет избежать сдвиг информации при необнаруживаемом искажении сигнала «Запрос в обратном ка«але, nppi этом на одной из стаиций принимается одна комбинация с необнаруженной ошибкой, а на другой - одна комбинация с отметкой «Оши&ка, но вставок и выпадений информации не происходит.

Кроме того, зстройство для приема дискретной информации в системах с решающей обратной связью позволяет уменьшить время, необходимое для исключения вставок и выпадений информации при искажениях служебных сигналов с одновременным увеличением скорости передачи информации.

Формула изобретения

Устройство для приема дискретной информации в системах с решающей обратной

связью, содержащее согласующий блок, выход .которого подключен ко входам накопителя, блока сравнения циклических номеров, декодера и приемника сигнала «Фаза, причем выходы блока сравнения циклических номеров и приемника сигнала «Фаза через последовательно соединенные первый элемент ИЛИ, первый элемент И, второй элемент ИЛИ, к второму входу которого подключен выход декодера, и второй эле.мент И подключены к входу регистра блокировки, тактовый выход которого подключен к второму входу второго элемента И непосредственно, а к входам блока сравнения циклических номеров и блока сопрял ения соответственно через дагчик циклических номеров и накопитель, о тличающееся тем, что, с целью сокращения времени на исключение вставок и выпадений при прие.ме информации, введены решающий блок, блок задержки, формирователь

сигнала «Ошибка, два дополнительных элемента И и дополнительный элемент ИЛИ, при этом выход декодера и вход регистра блокировки подключены к соответствующим входам первого дополнительного элемента И,

выход регистра блокировки через блок задержки подключен к одному из входов второго дополнительного элемента И и дополнительного элемента ИЛИ, к другому входу которых подключеН выход приемника скгнала «Фаза, а выходы первого и второго дополнительных элементов И л дополнительного элемента ИЛИ через решающий блок подключены к второму входу первого элемента И и к входу формирователя сигнала «Ошибка, выход которого подключен к дополнительному входу блока сопряжения.

Источник информации, принятый во внимание при экспертизе:

1. Денисов О. Е. Аппаратура передачи данных по телефонным каналам Аккорд - 5 1200, «Вопросы радиоэлектроники, серия ТПС, вып. 6, 1971, с. .32.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для защиты от ошибок | 1982 |

|

SU1070700A1 |

| Устройство для приема дискретной информации | 1981 |

|

SU1131031A1 |

| Устройство для приема дискретной информации | 1980 |

|

SU907845A2 |

| Устройство для приема самосинхронизирующейся дискретной информации | 1980 |

|

SU924902A2 |

| Устройство передачи и приема дискретной информации | 1989 |

|

SU1646066A1 |

| Устройство для приема дискретной информации | 1987 |

|

SU1501296A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1596464A1 |

| Устройство для защиты от ошибок | 1978 |

|

SU766029A1 |

| Устройство для передачи и приема дискретной информации с коррекцией ошибок | 1984 |

|

SU1197114A1 |

| Устройство защиты от ошибок | 1983 |

|

SU1272514A1 |

Авторы

Даты

1977-08-15—Публикация

1976-02-23—Подача