I

Изобретение относится к вычислительной технике, в частности.к запоминающим устройствам.

Известны ячейки памяти для регистров сдвига на МДП-транзисторах. Одни из Них отличаются высоким быстродействием и экономичны по потребляемой мощности, но слоны в эксплуатации, так как требуют большого количества тактовых импульсов .

Другие ячейки памяти просты в эксплуа- таиии, но имеют сравнительно невысокое быстродействие и неэкономичныпо потребляемой мощности 2.

Наиболее близкой к изобретению является ячейка памяти для регистра сдвига, содержащая коммутирующий МДП- ранзистор и инвертор, выполненный на последовательно включенных нагрузочном и ключевом МДП-транзисторах причем затвор нагрузочного транзистора подключен к- шине тактового питания З. Эта ячейка имеет невысокое быстродействие. Обусловлено это наличием на выходе каждого каскада большой паразитной емкости, представляющей собой емкость затвор-канал ключевого трян

зистора, а также малой крутизной характеристик нагрузочного транзистора, которая должна быть в 1О-20 раз меньше крутизны характеристик ключевого транзистора дл обеспечения на выходе каскада напряжения логического О.

Цель изобретения - повышение быстродействия ячейки.

Достигается это тем, что в известной ячейке памяти для |регистра сдвига исток коммутирующего МДП-транзистора подклк чен к затвору ключевого МДП-траизистора, а сток - к шине тактового питания.

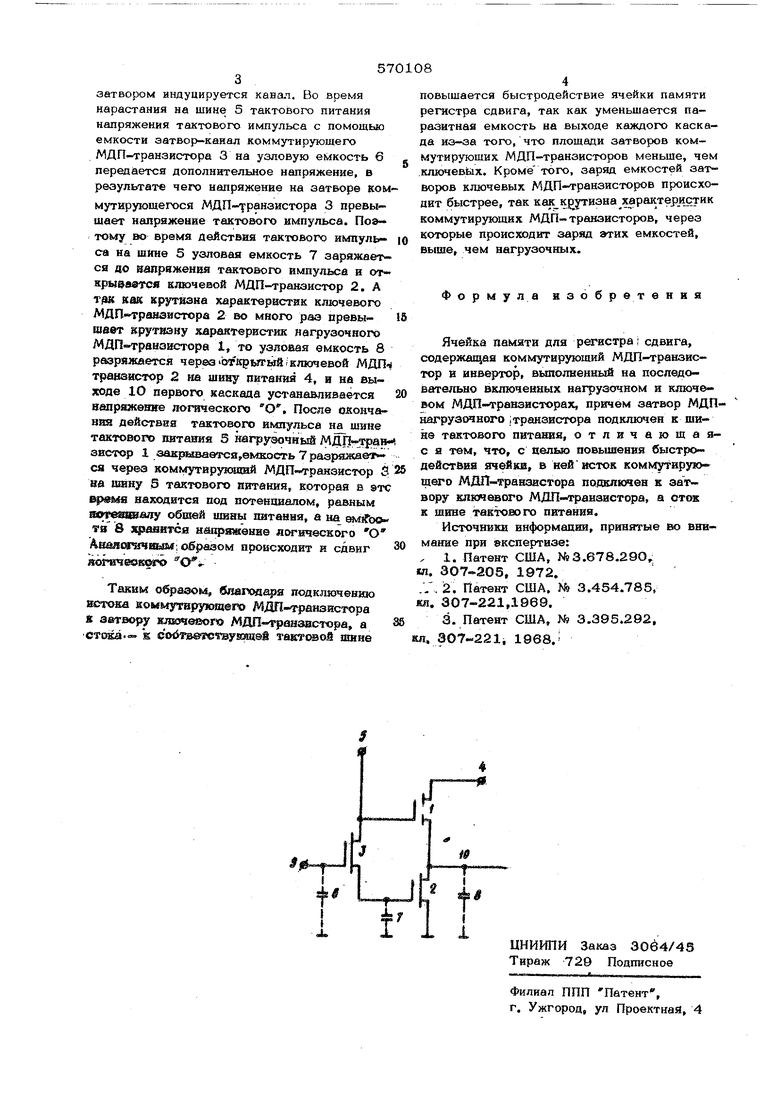

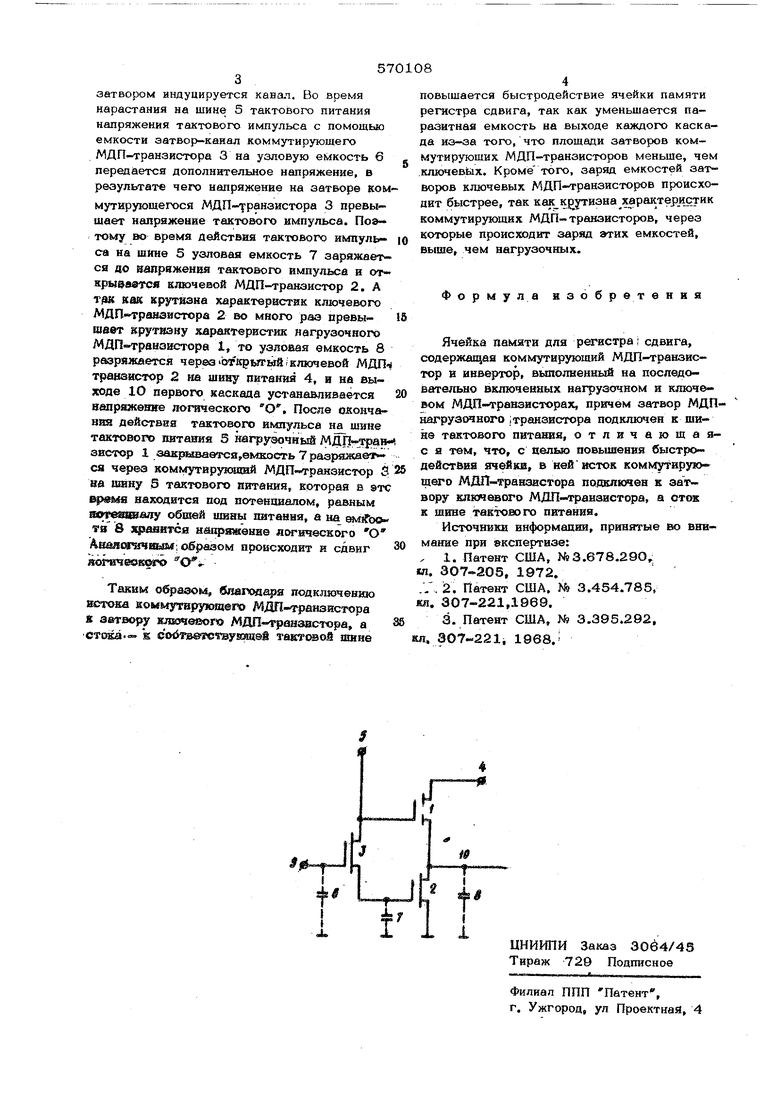

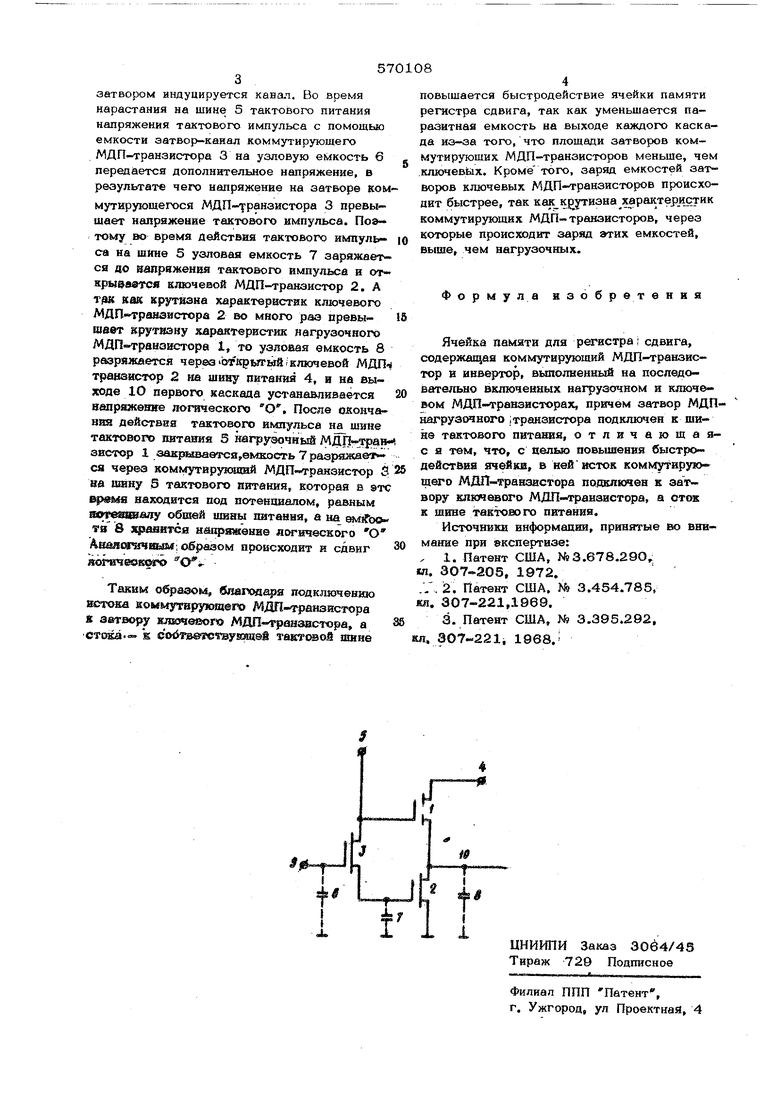

На чертеже дана предлагаемая ячейка,

Ячейка памяти для регистра сдвига содержит нагрузочный МДИ-транзистор 1, ключевой МДП-транзистор 2, коммутирующий МДП-транзистор 3, шину питания 4, шину тактового питания 5, узловые емкости 6, 7 и 8. Кроме того ячейка имеет вход 9 и выход 10.

Предлагаемая ячейка работает следующим образом. При подаче на вход 9 напряжения логической Еоммутирукяшй МДПтранзистор 3 открывается, т.е. под его затвором индуцируется канал. Во время нарастания на шине 5 тактового питания напряжения тактового импульса с помощью емкости затвор-канал коммутирующего МДП-транзистора 3 на узловую емкость 6 передается дополнительное напряжение, в результате чего напряжение на затворе ком мутирующегося МДП-ч-ранзистора 3 превышает напряжение тактового импульса. Поэтому во время действия тактового импульса на шине 5 узловая емкость 7 заряжается до квлраженвя тактового импульса и от крыэавтся ключевой МДП-транаистор 2. А Т|9К как крутизне характерЕхстик ключевого МДП транаистора 2 во много раз превышвет крутизну характеристик нагрузочного МДП-транаистора 1, то узловая емкость 8 разряжается черезЬткрыпгый; ключевой МДПтранзистор 2 на шиву питания 4, в на выходе 1О первого каскада устанавливается вапряж ше логического О, После олончавня действия тактового импульса на шине тактоворо питания 5 нагруэочйый МЯП-тр«1М зистор 1 аакрывается емкость 7 разряжает- ся через коммутврукшшй МДП- ранзистор S аа ншну 5 тактового питания, которая в этс находитса под потенциалом, равным aoveasaaay обшей ишаы питання, а на sMgoo ти 8 хранится нзоряженве яогического О А0ая(Я вч1ШМ; образом происходит и сдвиг яогич жсго . Таким образом, бдагсшаря подключению астока коммутирующего МДП-транзйстора к затвору ключвйого МДП-1)йнз0стора, а стока « k содтввтсчггуялаад тактозой ашне повышается быстродействие ячейки памяти регистра сдвига, так как уменьшается паразитная емкость на выходе каждого каскада из-за того, что площади затворов коммутирующих МДП-транзисторов меньше, чем .ключевых. Кроме того, заряд емкостей затворов ключевых МДП-транзисторов происходит быстрее, так как к5 утизна характеристик коммутирующих МДП-трб1нзисторов, через которые происходит заряд этих емкостей, выше, чем нагрузочных. Форму л а и 3 о б р е т е н и я Ячейка памяти для регистра сдвига, содержащая коммутирующий МДП-транзнстор в инвертор, выполненный на последовательно включенных нагрузочном н ключевом МДП-транзисторах, причем затвор МДПнйгруэочного ;транзистора подключен к шине тактового питания, отличаюисаяс а тем, что, с целью повьшення быстродействвя ячейка, в нейноток коммутирующего МДП-транзистора подключен к затвору Елючевого МДП.-транзистора, а сток к швне тактового питания. Источники информация, принятые во внимание прн экспертизе: . 1. Патент США, Ne3.678.29O, I. 307-205, 1972. .V. 2. Патент США. № 3.454.785, л. 307-221,1969. 3. Патент США, № 3.395.292, . 307-22li 1968.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти для регистра сдвига | 1977 |

|

SU680055A2 |

| Элемент памяти для регистра сдвига | 1978 |

|

SU706880A1 |

| Ячейка памяти для регистра сдвига | 1983 |

|

SU1125655A1 |

| Ячейка памяти на МДП транзисторах | 1981 |

|

SU968854A1 |

| ДВУХКАСКАДНЫЙ ДИНАМИЧЕСКИЙ СДВИГОВЫЙ РЕГИСТР | 2014 |

|

RU2542898C1 |

| Буферное устройство | 1977 |

|

SU622204A1 |

| ДВУХТАКТНЫЙ ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2556437C1 |

| Элемент памяти для регистра сдвига | 1979 |

|

SU832600A1 |

| Ячейка памяти для регистра сдвига | 1980 |

|

SU902075A1 |

| Ячейка памяти для регистра сдвига | 1972 |

|

SU503295A1 |

Авторы

Даты

1977-08-25—Публикация

1975-11-03—Подача