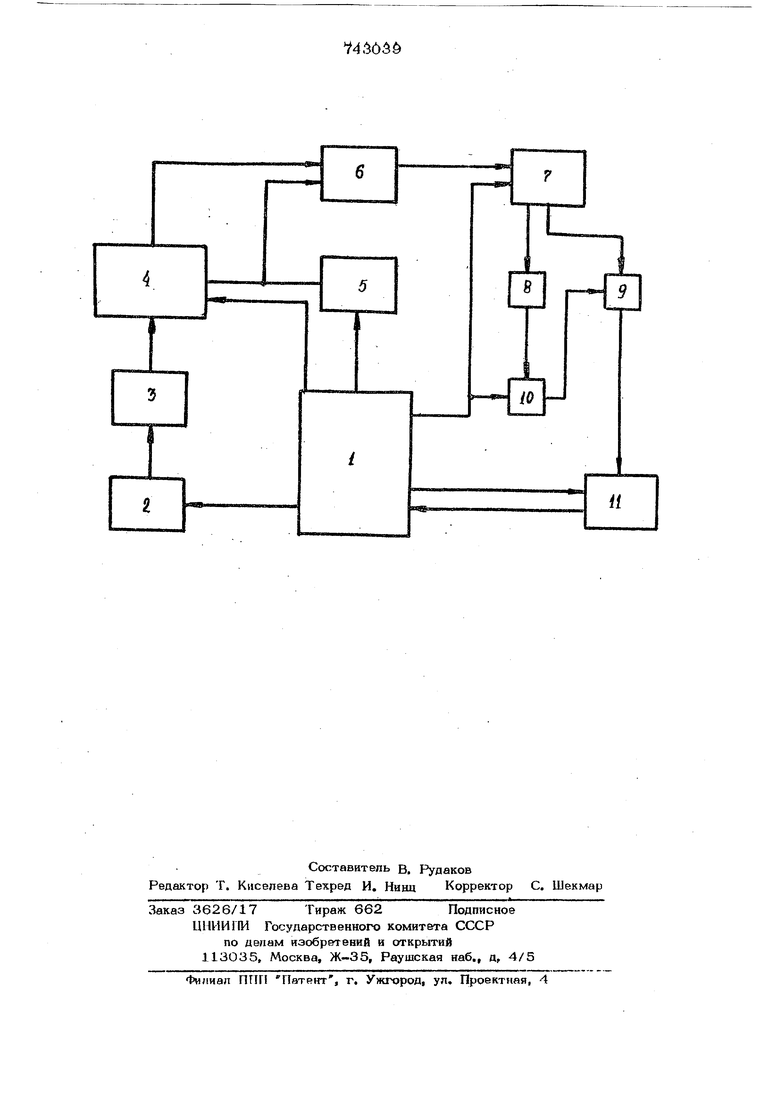

Изобретение относй ея к запоминак щим устройствам и может быть использовано для контроля адресного тракта накопителя. Известно устройство для контроля памяти, содержащее датчики контрольны сигналов по координатам X и У, выполненные на сердечниках, обмотки которык подключены к магнитному накопителю, связанному с дешифраторами адреса X и У, блок управления, усилители и схемы обнаружения отказа дешифраторов X и .У. Это устройство позволяет обнаружи неисправность адресного тракта блоков памяти с магнитными дешифраторами 11 Недостатком его является то, что это устройство предназначено для проверки только магнитных дешифраторов и обнаруживает неисправности только по отсутствии координатных токов в обмот ках таких дешифраторов. Наиболее близким техническим решением к изобретению является устройство для контроля адресного тракта накопителя, содержащее поспедовательно соединенные регистр адреса и дешифратор адреса, выход которого подключен к одному из входов накопителя, другие входы которо-. го подключены к выходу регистра числа и первому выходу блока управления, второй и третий выходы которого соединены со входами регистра адреса и регистра числа, блок сравнения, входы которого подключены к выходам накопителя и регистра числа 2. Недостатком этого устройства является низкая эффективность, не позволяющая выявить многократные ошибки, возникающие при отказах элементов адресного тракта, и в связи с этим большое время восстановления работоспособности устройства. Цель изобретения - повышение быстродействия и расширение области применения за счет обеспечения возможности выявления многократных ошибок. Поставленная цель достигается тем, что устройство содержит счетчик, элементы И, триггер и регистр ошибок, выход и первый вход которого подключены, соответственно ко входу и четвертому выходу блока управленля, второй вход соединен с выходом одного из элементов И, входы которого подключены к одним из выходов счетчика и вьрсоду триггера, первый вход которого соединен с пятым выходом блока управления и одним из входов счетчика, другие вход и вьиод счетчика подключены соответственно к выходу блока сравнения и входам другого элемента И, выход которого подключей ко второму входу триггера. На чертеже, представлена блок-схема устройства. Устройство содержит блок 1 управле- ния, регистр 2 адреса, дешифратор 3 адр

са, накопитель 4, регистр 5 числа, блок 6 сравнения, счетчик 7, первый 8 и второй 9 элементы И, триггер Ю и регистр 11 ошибок. Первый, второй и третий выходы блока 1 подключены соответственно ко входам накопителя 4, регистра 5 числа и регистра 2 адреса. Выход и первый вход регистра 11 подключены соот ветственно ко входу и четвертому выходу блока 1, второй вход соединен с выходом элемента 9 И, входы которого подключены к одним из выходов счетчика 7 и вьь ходу триггера 10. Первый вход триггера 10 соединен с пятым выходом блока 1 и одним из входов счетчика 7, другие вход и выход счетчика 7 подключены соответственно к выходу блока 6 сравнения и входам элемента 8 И, выход которого подключен ко второму входу тригге ра 10.

Устройство работает в двух режимах проверки адресного тракта (проверка входных цепей, проверка выходных цепей адресного тракта). В обоих режимах выявляются неисправности,, приводящие к постоянному выбору или не- выбору адресного тракта по какому-либо В.ХОДУ (выходу).

Рассмотрим работу устройства при проверке входных .цепей адресного тракта.

При пуске устройства происходит автоматическая установка в ноль регистров 2,5 и 11 и счетчика 7 (на чертеже соответствующие цепи установки условно не показаны).

Блок 1 управления формирует режим записи информации в накопитель 4 и разV

пи адресного тракта приведет к двухкрат ному выбору половины те.х адресов, к которым организовано обращение в накопителе 4. При этом в каждый двухкратно

выбранный адрес первоначально записывается О, а затем в этот же адрес перезаписывается . В связи с этим при сравнении считанной информации по какому-либо разряду накопителя 4 с

состоянием этого же разряда регистра числа на выходе блока 6 сравнения получаем 2 г ошибок. Подсчет количества ощибок ведется счетчиком 7, .в котором число разрядов равно п,/2. В случае

t -того входа адресного

неисправного

.

2 Циклов считывания тракта через в счетчике 7 имеется число ощибок, определяющее неисправность t-того в.хода адресного тракта. В этом случае

элемент 9 И дещифрирует cocTOHfrae

70 к/1 , равное ь , и сигнал с

его выхода поступает на первый вход регистра 11 ошибок. Елпок 1 управления вырабатывает управляющий сигнал после

прохождения всех циклов считьшания

при проверке i-той входной цепи адресного тракта, по которому и происходит запись информации с неисправности t-той входной цепи адресного тракта в

регистр 11 ошибок и обнуляет счетчик 7 и триггер 1О. Если блок 6 сравнения зафиксирует число ошибок, равное 2 тг , что возможно, например при неисправности запоминающих элементов, то срабатывает элемент 8, дешифррфующий состояние счетчика 7 равное г Сигнал с выхода элемента 8 И перебрасьшает триггер 1О, который блокирует 4 решает формирование кодов адреса и числа, EinoK 1 управления организует пересчет адресов первоначальной в первой половине регистра 2 адреса, в другую половину регистра 2 адреса записывается О. BQOK 1 управления также форми™ рует число, необходимое для проверки определенного входа адресного тракта: при проверке i -го входа по кажиощ выбираемому адресу накопителя 4 записывается число, соответствующее состоянию L -того разряда регистра 2 адреса. Через 2циклов записи информации блок 2 управления формирует сигнал считывання (где П - количество разрядов в регистре 2 адреса) и при этом блок 1 управления вновь формирует число, соответствующее состоянию I-того разряда регистра 2 адреса. Наличие неисправности любого вида в I -той входной цеэлемент 9 И. Таким образом, количеств ошибок, большее 2.-г- свидетельствующее о неисправности накопителя 4, не фиксируется устройством как ошибка адресного тракта. Это же произойдет и при наличии количества ошибок в счетчике, меньшего величины ч- , так как при этом элементы 8 и 9 И не срабатьшают. После проверки i -го входа адресного тракта блок 1 управления фор мирует число, необходимое для проверки ( I +1)-й входной цепи адресного тракта которое определяется сигналом ( L+l)-г разряда регистра 2 адреса. После проверки -j- -входного адресно го тракта блок 1 управления формирует сигнал, приводящий к считыванию информации об ошибках адресного тракта из регистра 11 ошибок и останову работы устройства, если есть хотя бы одна ошиб ка, записанная в регистр 11 ошибок. .Если же ошибок в работе адресного трак та нет, то блок 1 управления формирует адрес поступающий на регистр адреса, приводящий к выборке других 2 адресов из накопителя 4, определяемых выборкой старших Tt/2 разрядов регистра 2адреса. При этом первая половина регистра 2 адреса заполняется нулями, а пересчет адресов организуется во второй половине регистра 2 адреса. При проверке выходных цепей адресно го тракта необходимо использовать объем накопителя 4 больший, чем при проверке входных цепей. Действительно, если испалЬ)Зуется та же часть объема накопителя 4, что и дйя проверки входных цепей адресного тракта, то при неисправности какого-либо выхода дешифратора 3в счетчике 7 записьшается . Чтобы использовать одни и те же блоки для локализации ошибок как по входным, так и по выходным цепям адресного тракта, в последнем случае должен быть исполь- зован объем накопителя, в раза больший, чем в первом, т.е. „.,/1 2./i ,«-t - t. Следовательно, блок 1 управления дол жен формировать в регистре адреса 2 (И-1)-разрядный код адреса, изменяющийся от О до 2 а в rL-й разряд регистра адреса записывать О. Для проверки I -той выходной цепи адресного тракта блок 1 управления формирует число таким образом, что О записьшается по адресам с номерами (m-l) -2(где tn. изменяется от 1 до 2 /2), а по всем остальным адресам записываются единицы. При проверке (j +1)-й выходной цепи адресного тракта О запис1,1вается по всем адресам с номером ( +1) +{tn -2) 2 и т.д. Обнаружение неисправности i -и выкодной цепи происходит аналогично обнаружению неисправности 1 -и входной цепи. Таким образом, предлагаемое устройство позволяет обнаружить не только однократные, но и многократные ошибки в работе адресного тракта накопителя 4, локализовать неисправности с точностью до соответствующего неисправного входа или выхода адресного тракта и, тем самым, значительно уменьшить время устранения неисправности. Формула изобретения Устройство для контроля памяти, содержащее последовательно соединенные регистр адреса и дешифратор адреса, выход которого подключен к одному из входов накопителя, другие входы которого подключены к выходу регистра числа и первому выходу блока управления, второй и третий вьгходы которого соединены со входами регистра адреса и регистра числа, блок .сравнения, входы которого подключены к выходам накопителя и регистра числа, отличающеес я тем, что, с целью повышения быстродействия н расширения области применения за счет обеспечения возможности выявления многократных ошибок, оно содержит счетчик, элементы И, триггер и регистр ошибок, выход и первый вход которого подключены соответственно ко входу и четвертому выходу блока управления, второй вход соединен с выходом одного из элементов И, входы которого подключены к одним из выходов счетчика и выходу триггера, первый вход которого соединен с пятым вьгх.одом блока управления и одним из входов счетчика, другие в.хол и выход счетчика подключены соответственно к выходу блока сравнения и входам другого элемента И, выод которого подключен ко второму вхоу триггера. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР 555442, кл. & 11 С 29/ОО, 1975. 2.Авторское свидетельство СССР 333559, кл. G 11 С 29/00, 1970 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля памяти | 1980 |

|

SU926724A2 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU980166A1 |

| Оперативное запоминающее устройство с самоконтролем | 1977 |

|

SU708423A1 |

| Оперативное запоминающее устройство с самоконтролем | 1982 |

|

SU1042081A1 |

| Устройство для контроля оперативной памяти | 1983 |

|

SU1295455A1 |

| Устройство для контроля памяти | 1982 |

|

SU1020865A1 |

| Устройство для контроля памяти | 1979 |

|

SU769642A1 |

| Оперативное запоминающее устройство с самоконтролем | 1978 |

|

SU771731A1 |

| Запоминающее устройство с исправлением ошибок при считывании информации | 1976 |

|

SU607281A1 |

| Динамическое запоминающее устройство с самоконтролем | 1982 |

|

SU1022224A1 |

а

Авторы

Даты

1980-06-25—Публикация

1978-01-23—Подача