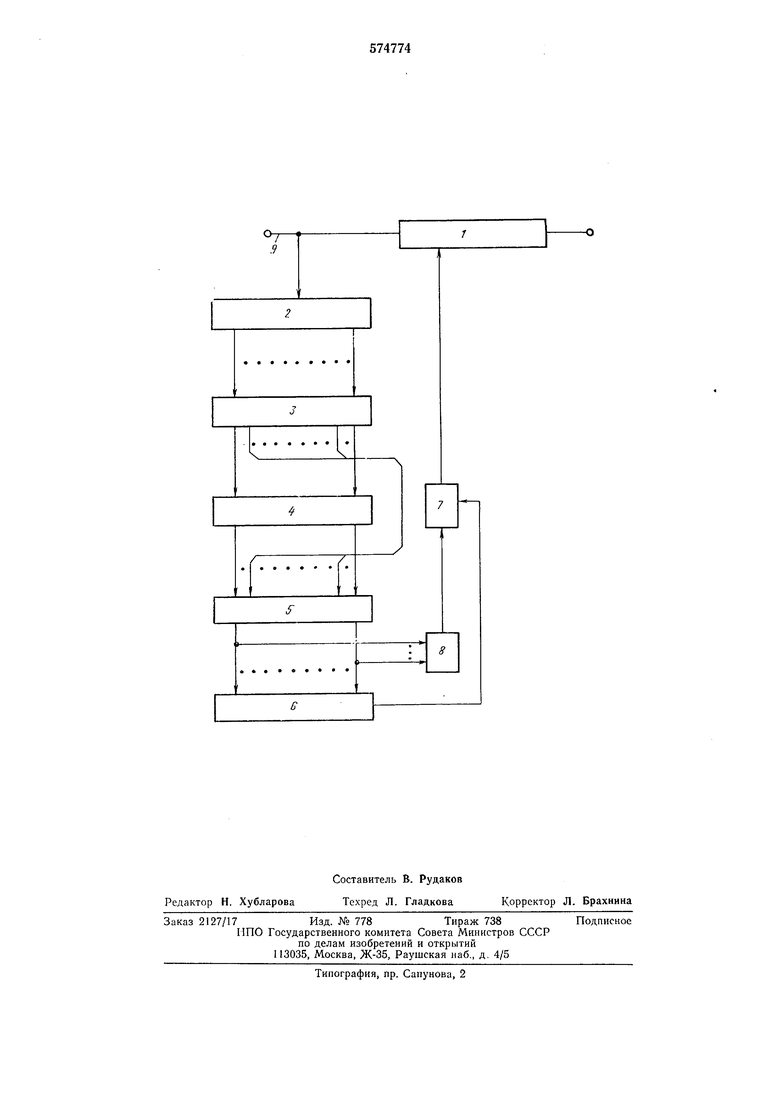

выходах дешифратора 2 появляются сигналы, которые через ключевые элементы 3 устанавливают соответствующие триггеры 4 в единичное состояние, подготавливая тем самым срабатывание элементов И 5. Триггеры 4 в единичном состоянии определяют допуск к соответствующим ячейкам памяти.

Кодовый адрес запрашиваемой ячейки поступает в блок 1 и дешифратор 2. На соответствующем выходе дешифратора появляется сигнал, который через один из выходов ключевых элементов 3 поступает на вход соответствующего элемента И 5. Если к запрашиваемой ячейке памяти разрешен допуск, то на вход этого элемента И 5 подается разрешающий сигнал с соответствующего триггера 4. Элемент И 5 срабатывает и через элемент ИЛИ 8 открывает элемент И 7, а также запускает датчик 6 интервалов времени. Датчик 6 формирует временной интервал, в течение которого разрешается допуск к запрашиваемой ячейке памяти. Этот сигнал через открытый элемент И 7 поступает в блок 1, выдающий сигнал разрешения допуска в течение сформированного интервала времени.

Таким образом, предложенное устройство позволяет выдавать разрешение на допуск за время, равное анализу одного кодового адреса, что суш.ественно повышает его быстродействие.

Формула изобретения

Устройство для защиты памяти, содержащее датчик интервалов времени, подключенный выходом к первому входу элемента И, блок регистрации адреса, входы которого соединены соответственно с адресными шинами

и выходом элемента И, отличающееся тем, что, с целью повышения быстродействия, оно снабжено последовательно соединенными дешифратором, ключевыми элементами, триггерами, дополнительными элементами И и

элементом ИЛИ, выход которого подключен ко второму входу элемента И, входы дешифратора и датчика временных интервалов соединены соответственно с адресными шинами и выходами дополнительных элементов И,

причем одни из входов последних подключены к соответствующим выходам ключевых элементов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 306463, кл. G06F 11/00, 1968.

2. Авторское свидетельство СССР № 397964, кл. G ПС 7/00, 1970.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для защиты памяти | 1979 |

|

SU841065A2 |

| Устройство для защиты блоков памяти | 1978 |

|

SU752498A1 |

| Адаптивное устройство для защиты памяти | 1983 |

|

SU1103291A1 |

| Устройство для защиты памяти | 1977 |

|

SU618741A1 |

| Устройство для защиты памяти | 1988 |

|

SU1508216A1 |

| Устройство для защиты памяти | 1983 |

|

SU1113854A1 |

| Устройство для защиты памяти | 1977 |

|

SU680060A1 |

| Логический анализатор | 1989 |

|

SU1730627A1 |

| Таймер | 1985 |

|

SU1357939A1 |

| Шифратор | 1980 |

|

SU920835A1 |

Авторы

Даты

1977-09-30—Публикация

1976-05-17—Подача